本文主要是介绍高速接口IO片上SSN分析方法,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

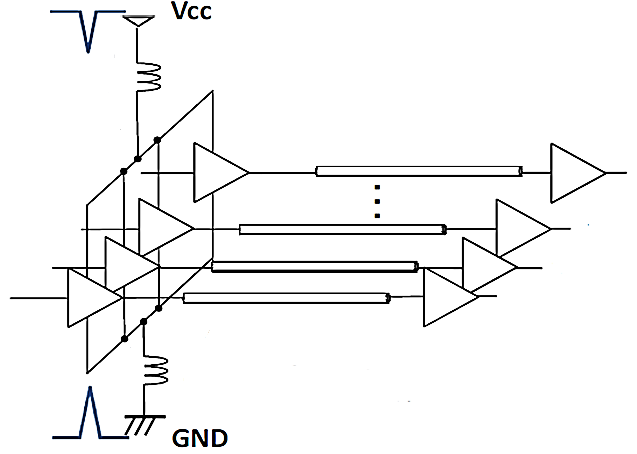

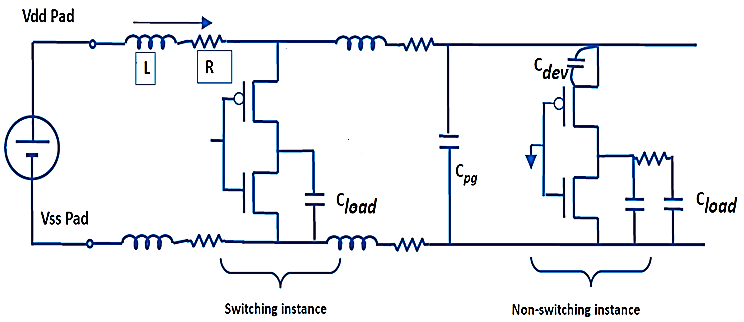

Gbps信号在当今的高速IO设计中非常常见。由于封装和板上的寄生电感,高速信号在高频下汲取电流,导致大的电源尖峰或骤降。像DDR5这样的并行总线接口有20多个高速IO一起切换,导致同时切换噪声(SSN)。SSN的不期望的产物是定时抖动或等效地称为PSIJ。随着并行总线中信号数量的增加,SSN进一步增加。当多个输出缓冲器同时改变其逻辑状态时,会产生大功率和接地反弹,如图所示。

SSN产生机理

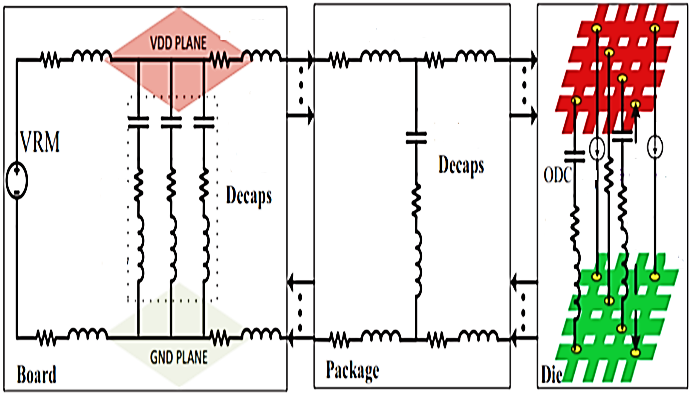

下图显示了系统PDN的等效电路,包括板、封装和管芯。片上PDN有助于在DC和高频中提供噪声。芯片上的导线结构很小,具有电阻,导致电网上的IR下降。芯片上的DC电压下降取决于位置,即靠近电源凸点的电路电压下降很小,而远离电源凸块的块电压下降很高。通过提高电源凸点电压来补偿芯片上的DC电压降并不是最好的解决方案。电路的这种位置依赖性在PCB和封装中并不重要,因为与管芯上的金属网布线相比,数字电源接地平面更大。芯片内部管子上电路的开关活动导致高频电流通过PDN,从而产生电压纹波。这种纹波可以使用On DIE DECAP来控制。

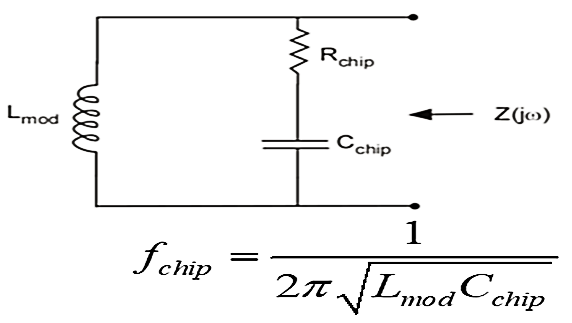

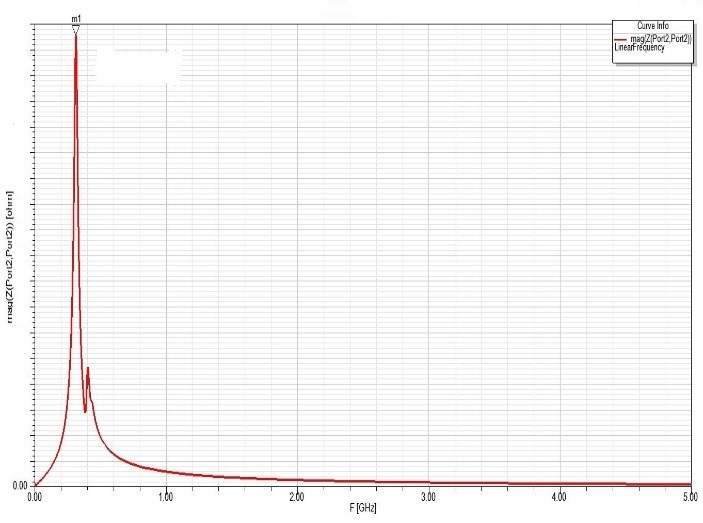

ODC与封装电感一起导致中频谐振,如下图所示。如果汲取的电流的频率落在PDN谐振频率范围内,谐振可能导致巨大的电源噪声。封装谐振频率还取决于板 PDN电感以及封装PDN电感。

板PCB通常比封装更大,因此板PDN电感比封装PDN电感小。晶体管切换是非常快的事件,PCB上的DCDC/LDO将无法满足芯片上电路的电流需求,因为稳压器离芯片太远(电感过高) 。电压纹波和接地反弹主要是由PDN 的电感(L*di/dt)引起的,如前文图所示。DDR5等并行总线接口中的SSN是由于大量驱动器同时切换导致电源和接地轨中的电压尖峰而发生的。SSN的结果是变化是总线上的延迟或定时偏移,过冲以及欠射信号导致波形失真,从而损害时序和电压裕度。从芯片驱动的电流通过其电源引脚和接地引脚具有返回路径。由于SSN的设计标准是电感时间常数需要明显小于其电容时间常数,因此需要容纳更多数量的电源和接地引脚以减少回路电流的电感。SSN可以通过信号SlewRate速率控制、片上PDN去耦优化、凸块和BGA球映射优化来控制,以保持电感环路较小。数据刺激模式编码方案还可以通过减少开关活动和控制 刺激频率范围以使PDN谐振不被激发来减少PG轨道上的 噪声。随着技术节点的收缩,晶体管切换得越快,每个凸块的瞬态电流越高,由于C4凸块间距的等效收缩尚未发生,SSN变得更糟。

片上SSN分析方法

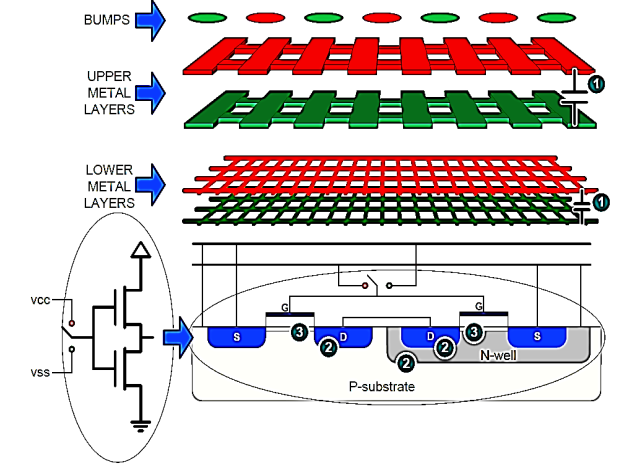

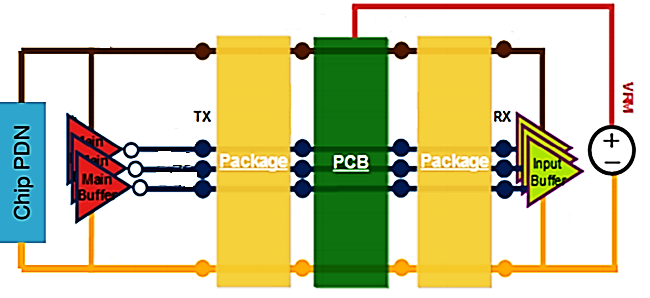

SSN分析的第一步是PDN模型的提取。下图显示了芯片的典型PDN网络。通常,需要芯片的GDSII或DEF LEF来进行布局提取。GDS可以是完整的芯片布局,也可以是只有IO环及其 PDN的部分布局。GDS定义了不同单元的放置位置、芯片上的电源和接地布线(宽度、间距、方向、利用率)以及单元与这些电源和接地线的连接。提取可以是R、 RC或RLC。仅提取“R”对于IRDROP分析有用,而对于SSN 类型的分析则需要RC或RLC提取。

片上PDN提取仅涉及电阻和电容的计算,因为片上PDN的电感可以忽略不计。裸片上解封装包括放置在设计中的去耦电容器单元以及由功率路由和电路提供的寄生电容。对于数字电路,寄生电容的重要部分来自在给定时间不翻转的电路块的电容。具有一些近似值的商业工具可以基于块中切换的概率来提取较大电路块中的平均电容。对于模拟和混合信号电路,由于非有源而产生的寄生电容与由功率路由提供的寄生电容相比,电路明显更小。

由于PDN是powermesh的网络,片上PDN的RC网络将具有数百万个节点。这种庞大的模型不能用于瞬态模拟,同时仿真时间也太长。RC模型的降阶是设计中的一个关键步骤。模型阶数减少从较大的线性电路开始,并将其减少到较小的线性等效电路,而不会对电路性能产生很大影响。在估计电路块的电源引脚上的正确纹波电压时,归一算法的准确性是非常关键的。商业仿真工具提供了使用Y矩阵进行模型降阶和极点数量较少的合成的算法。通过将片上PDN与封装和板上PDN相结合,并从芯片的金属层上的一个端口观察,可以得出系统PDN阻抗分布,如图所示。

由于封装电感和片上电容的相互作用,可以在中频范围内看到谐振。SSN分析需要捕获电路块汲取的电流,同时运行瞬态电路仿真来捕捉电路块电源接地(PG)引脚上的电流分布。电路块的电源引脚上的纹波取决于PDN网络设计。PDN的RC常数相对于电路的PG引脚越小,纹波越小。PDN设计的简化RC网络需要与电路的电流特征或spice模型相结合。与使用电路的spice模型相比,使用电流特征减少了瞬态模拟时间。任何一种方法都能提供完全相同的结果。在这个阶段可以优化片上解封装,以保持每个电路块上的纹波较低。图7显示了典型的SSO瞬态模拟设置。芯片PDN可以建模为集总 Rdie和Cdie或分布式宽带spice电路。Rdie-Cdie集总建模允许更快的瞬态模拟,但会损失准确性。集总芯片PDN的优点是快速的假设分析。最终的签核分析需要使用芯片PDN的分布式模型来完成。EM求解器利用信号和电源接地信息提取PCB和封装。需要确保PCB和封装的无源性和因果性。需要模拟偶数和奇数激励pattern的SSN模拟。捕获各种信号质量参数,如总线上的最小-最大偏斜、过冲、振铃。此外,在奇数和偶数模式激励下,可以捕捉到最小和最大电源噪声。

对于并行总线接口,非常需要知道同时切换的输出驱动器的正确数量。优化存在系统信道中的SSN对于确保片上PDN不会过载至关重要,因为当电容负载直接连接到IO焊盘时,电源噪声最差且不现实。

这篇关于高速接口IO片上SSN分析方法的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!