高速接口专题

高速接口IO片上SSN分析方法

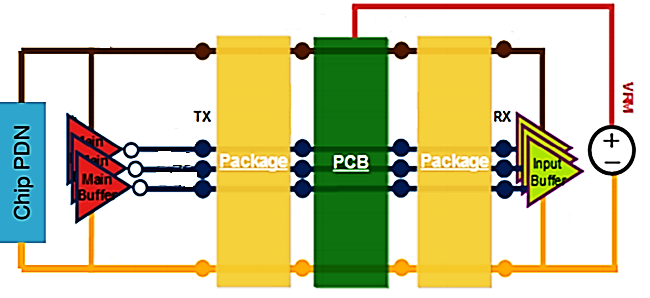

Gbps信号在当今的高速IO设计中非常常见。由于封装和板上的寄生电感,高速信号在高频下汲取电流,导致大的电源尖峰或骤降。像DDR5这样的并行总线接口有20多个高速IO一起切换,导致同时切换噪声(SSN)。SSN的不期望的产物是定时抖动或等效地称为PSIJ。随着并行总线中信号数量的增加,SSN进一步增加。当多个输出缓冲器同时改变其逻辑状态时,会产生大功率和接地反弹,如图所示。 SSN产

xilinx的高速接口构成原理和连接结构

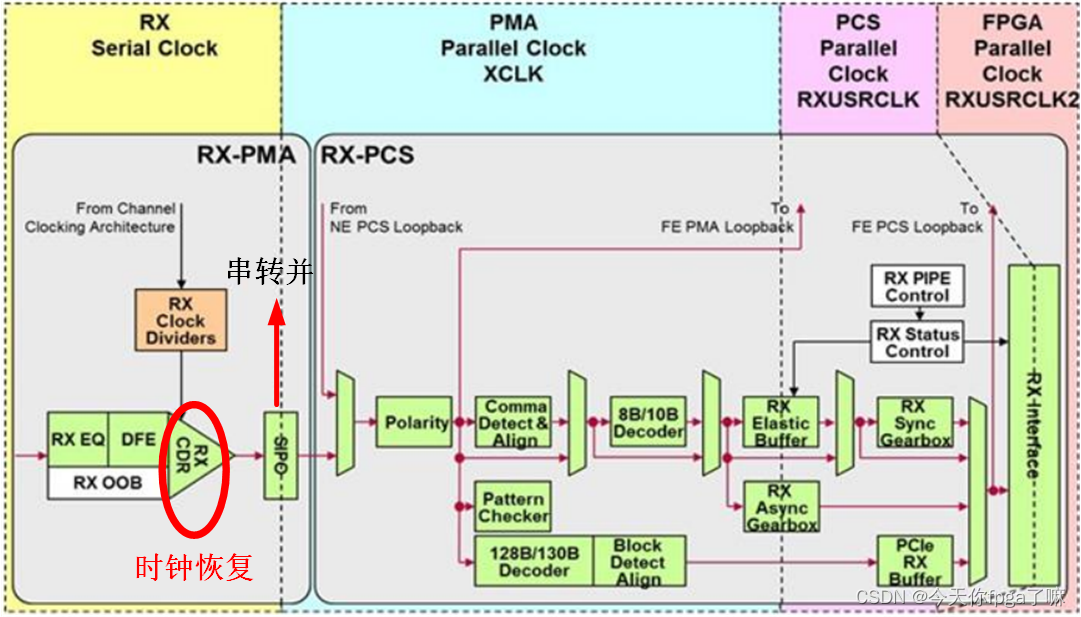

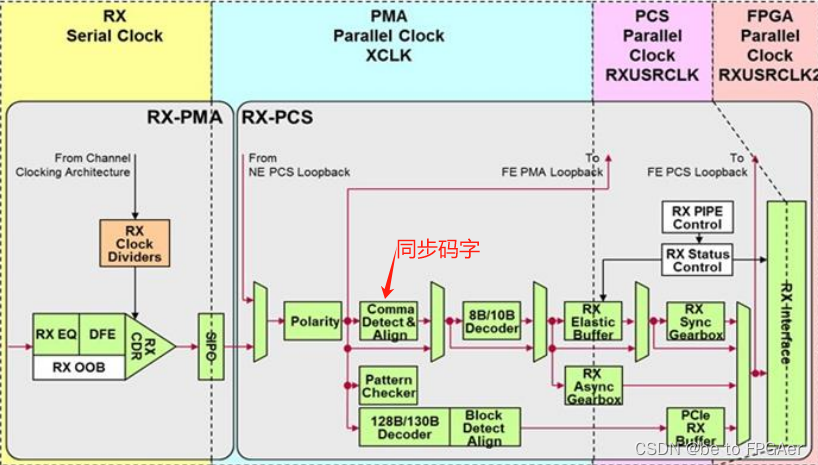

本文来源: V3学院 尤老师的培训班笔记【高速收发器】xilinx高速收发器学习记录Xilinx-7Series-FPGA高速收发器使用学习—概述与参考时钟GT Transceiver的总体架构梳理 文章目录 一、概述:二、高速收发器结构:2.1 QUAD2.1.1 时钟2.1.2 CHANNEL的内部结构:1)TX2)RX 一、概述: Xilinx 的高速接口称

xilinx 的高速接口构成原理和连接结构

Xilinx 的高速接口是 QUAD 为单位的意思是 4 对收发器组成一个 QUAD 这是收发器的最小单元。 例如下方的GTP接口只有一个quad,单个lane能达到5gbit/s,K7 GTX达到16gbit/s等。 SouthCLK 是由相邻的上游 QUAD 提供的时钟或者给相邻下游 QUAD 提供时钟,上图是一个独立的 QUAD。NorthCLK 是由下游的 QUAD 提供时钟,或者给相

【学习笔记】Serdes中的高速接口设计

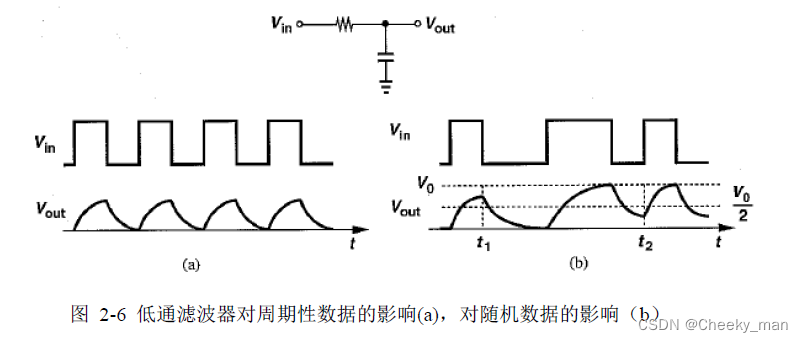

参考文献: 一、绪论 1.1 背景 “串行替代并行”: 串行传输使用差分信号传输以传输更长距离; 并行传输因串扰无法长距离传输;并行线路对信号偏斜量的要求,限制了最大的传输速率。 SerDes=Serializer + Deserializer Serializer:用于Tx端,译为串行器,将并行数据转化为串行数据(并转串)。 PLL:时钟源,以低速参考时钟作为输入,

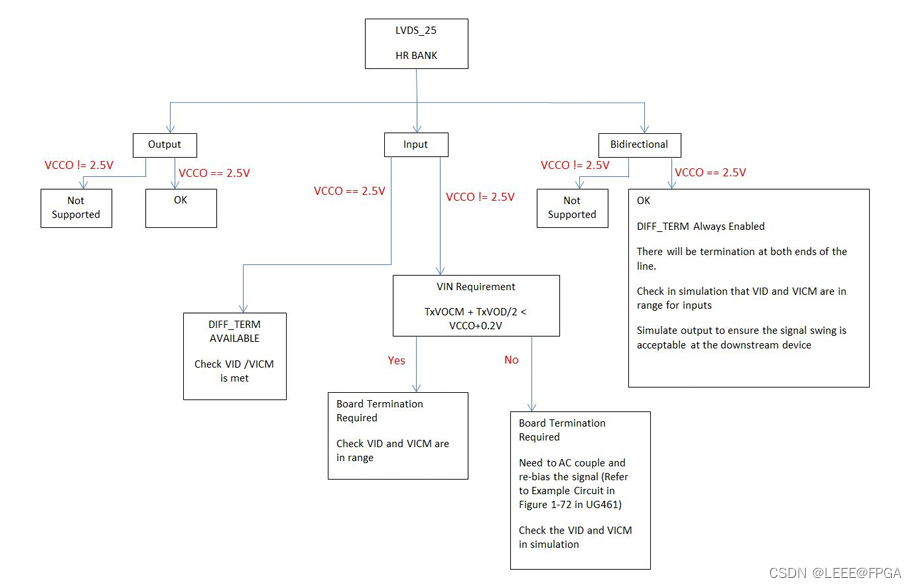

FPGA 高速接口(LVDS)

差分信号环路测试 1 概述 LVDS(Low Voltage Differential Signalin)是一种低振幅差分信号技术。它使用幅度非常低的信号(约350mV)通过一对差分PCB走线或平衡电缆传输数据。大部分高速数据传输中,都会用到LVDS传输。 目前FPGA开发板资料中涉及LVDS通信的方案并不多,但是LVDS实际上有大量的应用,特别是在高速ADC, 高分辨率摄像头,液晶屏显示技术

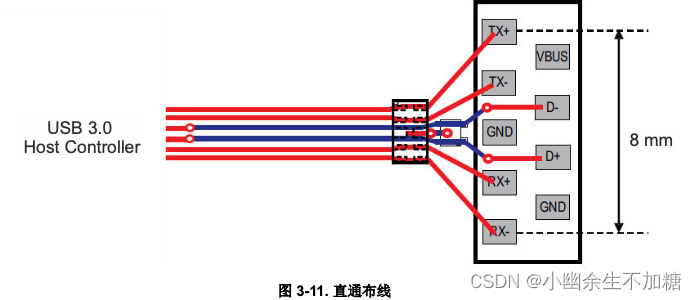

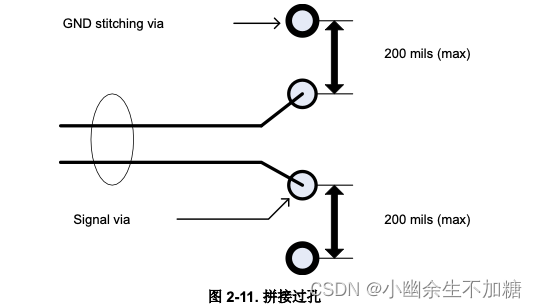

高速接口PCB布局指南(五)高速差分信号布线(三)

高速接口PCB布局指南(五)高速差分信号布线(三) 1.表面贴装器件焊盘不连续性缓解2.信号线弯曲3.高速信号建议的 PCB 叠层设计4.ESD/EMI 注意事项5.ESD/EMI 布局规则 tips:资料主要来自网络,仅供学习使用。 1.表面贴装器件焊盘不连续性缓解 避免在高速信号布线中采用表面贴装器件(SMD),其原因在于这些器件会导致中断,从而对信号质量产生负面 影响。

高速接口PCB布局指南(二)通用高速信号布线

高速接口PCB布局指南(二)通用高速信号布线 1.PCB材料编织2.高速信号布线长度3.高速信号布线长度匹配4.高速信号参考平面 tips:资料主要来自网络,仅供学习使用。 1.PCB材料编织 在常见的 PCB 材料上为差分信号布线时,由于构成 PCB 的玻璃纤维材料(Ɛr 约为 6)和环氧树脂(Ɛr 约为 3)的静态介电常数不同,差分信号对的每条布线都会面临不同的介电常数和相

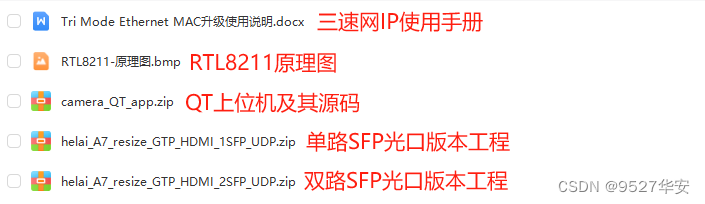

FPGA高端项目:图像缩放+GTP+UDP架构,高速接口以太网视频传输,提供2套工程源码加QT上位机源码和技术支持

目录 1、前言免责声明本项目特点 2、相关方案推荐我这里已有的 GT 高速接口解决方案我这里已有的以太网方案我这里已有的图像处理方案 3、设计思路框架设计框图视频源选择ADV7611 解码芯片配置及采集动态彩条跨时钟FIFO图像缩放模块详解设计框图代码框图2种插值算法的整合与选择 GTP 全网最细解读GTP 基本结构GTP 发送和接收处理流程GTP 的参考时钟GTP 发送接口GTP 接收接口

紫光同创FPGA实现HSSTLP高速接口视频传输,8b/10b编解码,OV5640采集,提供PDS工程源码和技术支持

目录 1、前言免责声明 2、我这里已有的 GT 高速接口解决方案3、设计思路框架设计框图OV5640摄像头配置及采集视频数据封装按键选择HSSTLP高速收发器详解HSSTLP基本了解HSSTLP之时钟HSSTLP之PCSHSSTLP之PMAHSSTLP之接口说明硬件设计HSSTLP IP调用和配置 SFP连接方案选择视频数据对齐视频数据解码图像缓存架构详解架构讲解视频缓存请求AXI总线HMI

紫光同创FPGA实现HSSTLP高速接口通信,8b/10b编解码数据回环,提供PDS工程源码和技术支持

目录 1、前言免责声明 2、我这里已有的 GT 高速接口解决方案3、设计思路框架HSSTLP详解HSSTLP基本了解HSSTLP之时钟HSSTLP之PCSHSSTLP之PMAHSSTLP之接口说明 硬件设计HSSTLP IP调用和配置 4、PDS工程详解5、上板调试验证并演示6、福利:工程代码的获取 紫光同创FPGA实现HSSTLP高速接口通信,8b/10b编解码数据回环,提供PDS