本文主要是介绍xilinx的高速接口构成原理和连接结构,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

本文来源:

- V3学院 尤老师的培训班笔记

- 【高速收发器】xilinx高速收发器学习记录

- Xilinx-7Series-FPGA高速收发器使用学习—概述与参考时钟

- GT Transceiver的总体架构梳理

文章目录

- 一、概述:

- 二、高速收发器结构:

- 2.1 QUAD

- 2.1.1 时钟

- 2.1.2 CHANNEL的内部结构:

- 1)TX

- 2)RX

一、概述:

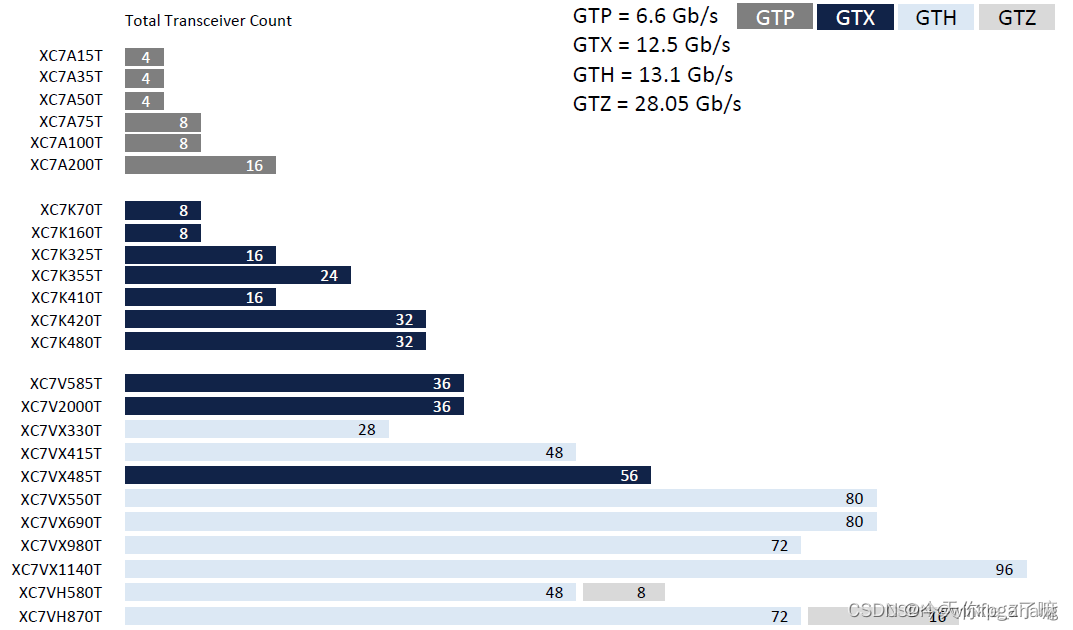

Xilinx 的高速接口称之为 transceivers(高速收发器),这部分电路是专用电路,供电等都是独立的,管脚和通用管脚不通用。每个系列的高速接口略有不同,分别为:

1.A7 的GTP

2.V7的GTH

3.K7的GTX

4.少量V7的GTZ

它们之间的区别在于最高线速率不同,GTZ>GTH>GTX>GTP.,结构大致相同。

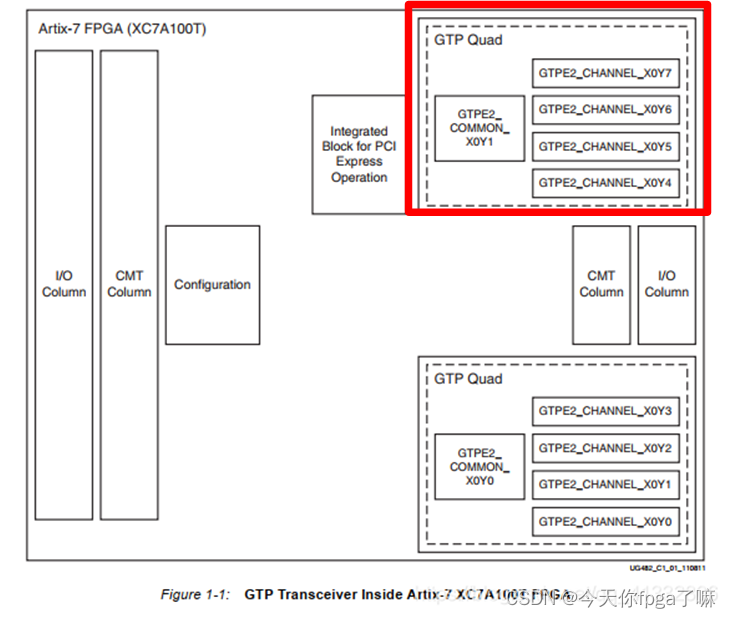

手上板子的芯片是xc7a100t系列的,因此需要参考的手册是ug482。

二、高速收发器结构:

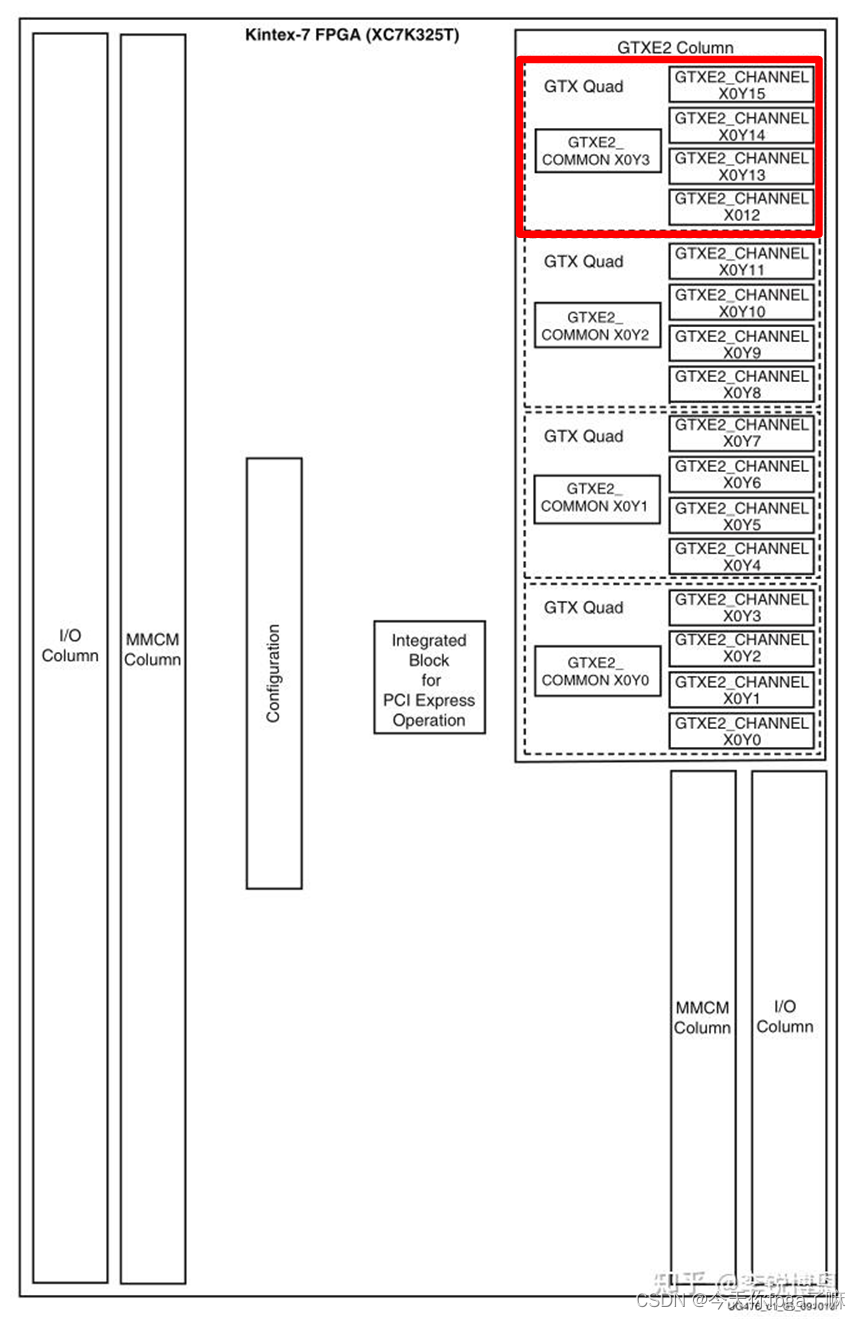

上图可以看到:A7系列的高速收发器(GTP)是上下两侧分布的,而K7系列的高速收发器(GTX)则是单列放置。

2.1 QUAD

Xilinx 的高速接口是 QUAD 为单位的,意思是 4 对收发器(channel)组成一个 QUAD ,这是收发器的最小单元。

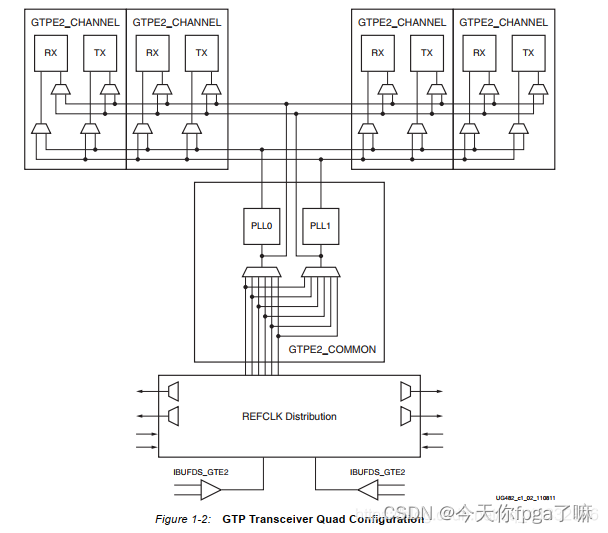

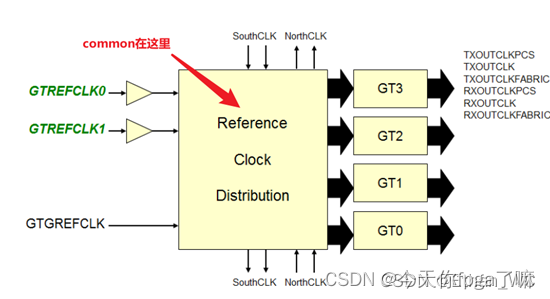

quad内部结构图如下:

可见一个quad包括:

1.4个channel,每个channel包含一对收发器

2.1个common(共享时钟资源),包含两个PLL。

3.两个REFCLK(参考时钟)。

注释:

1.GTREFFCLK0/1 是参考时钟,是给高速接口内的 PLL 提供的参考时钟用于产生 PLL 输出

时钟的。

2.GTGREFCLK 是用于测试高速接口的测试时钟,一般我们用户不需使用,比如 IBERT 这

种测试软件可以使用。

3.SouthCLK 是由相邻的上游 QUAD 提供的时钟或者给相邻下游 QUAD 提供时钟,上图是

一个独立的 QUAD。

4.NorthCLK 是由下游的 QUAD 提供时钟,或者给相邻上游的 QUAD 提供时钟。

2.1.1 时钟

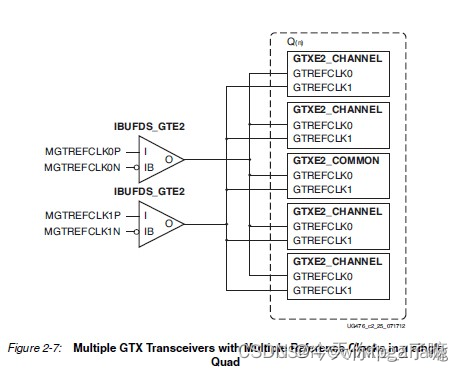

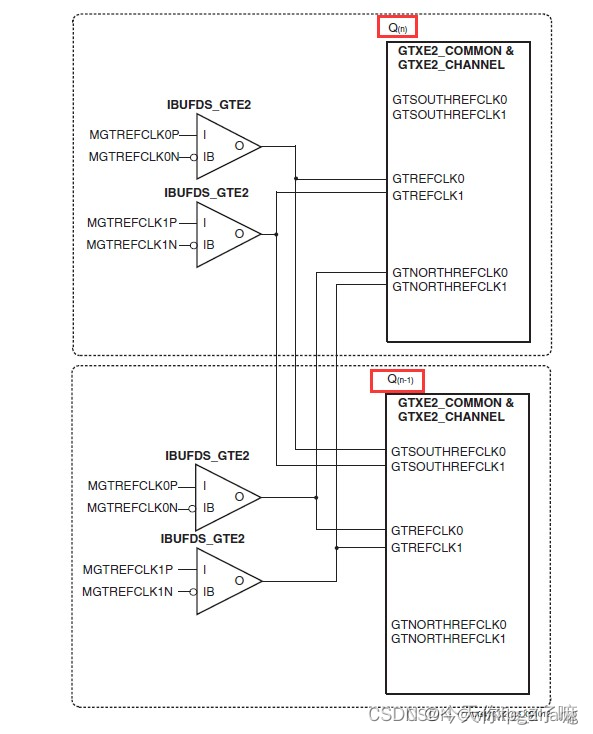

因为每一个Quad有两个外部参考时钟,因此对于每一个Quad来说,可以选择两个不同的参考时钟,每一个CHANNEL的接收端和发送端都可以独立选择参考时钟,如下图所示:

此外,还可以使用其他Qua的参考时钟(south clk & north clk),

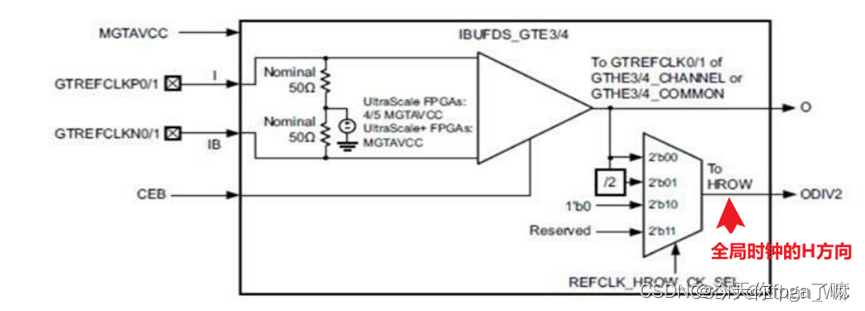

图上可以看到:REFCLK进来必须要经过一个IBUFDS_GTE,完成差分转单端。

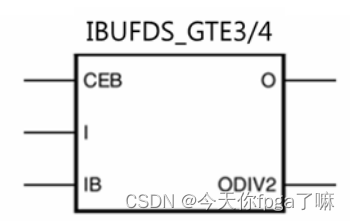

IBUFDS_GTE内部结构图:

注释:HROW是全局时钟放在水平方向还是垂直方向的节点,ODIV2是输出给用户逻辑用的,可以选二分频或者不分频或者直接拉低降低功耗。

注意CPLL和QPLL的区别:

1.QPLL,其中的Q含义就是QUAD,即一个GTX QUAD公用的PLL。

2.CPLL,即Channel PLL,含义是每一个Channel单独拥有的PLL。

3.两者支持的线速率不同CPLL的速率要小于QPLL。

2.1.2 CHANNEL的内部结构:

-

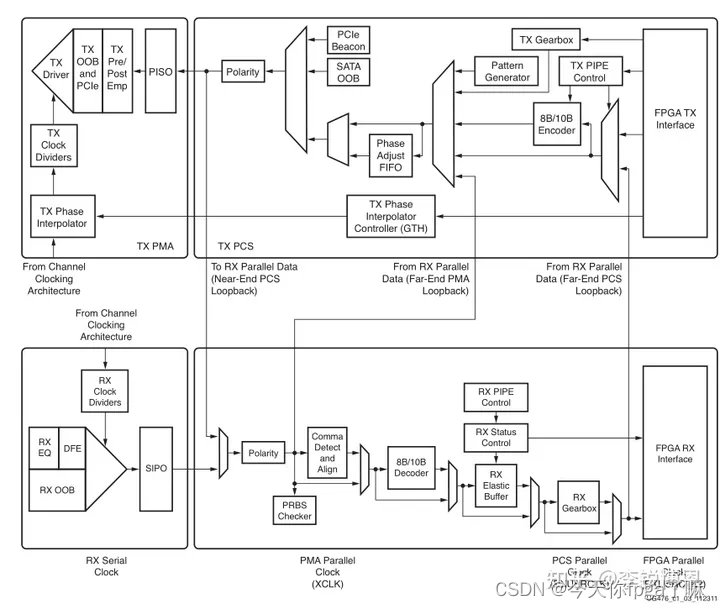

Transmitter的数据流大致为: FPGA用户逻辑的数据,进入FPGA TX接口,进入PCS,再经过PMA,转换为高速串行数据输出。

-

Receiver的数据流大致为:数据由PMA部分结构,转换为并行数据进入PCS,再经过RX接口输出给FPGA用户逻辑处理。

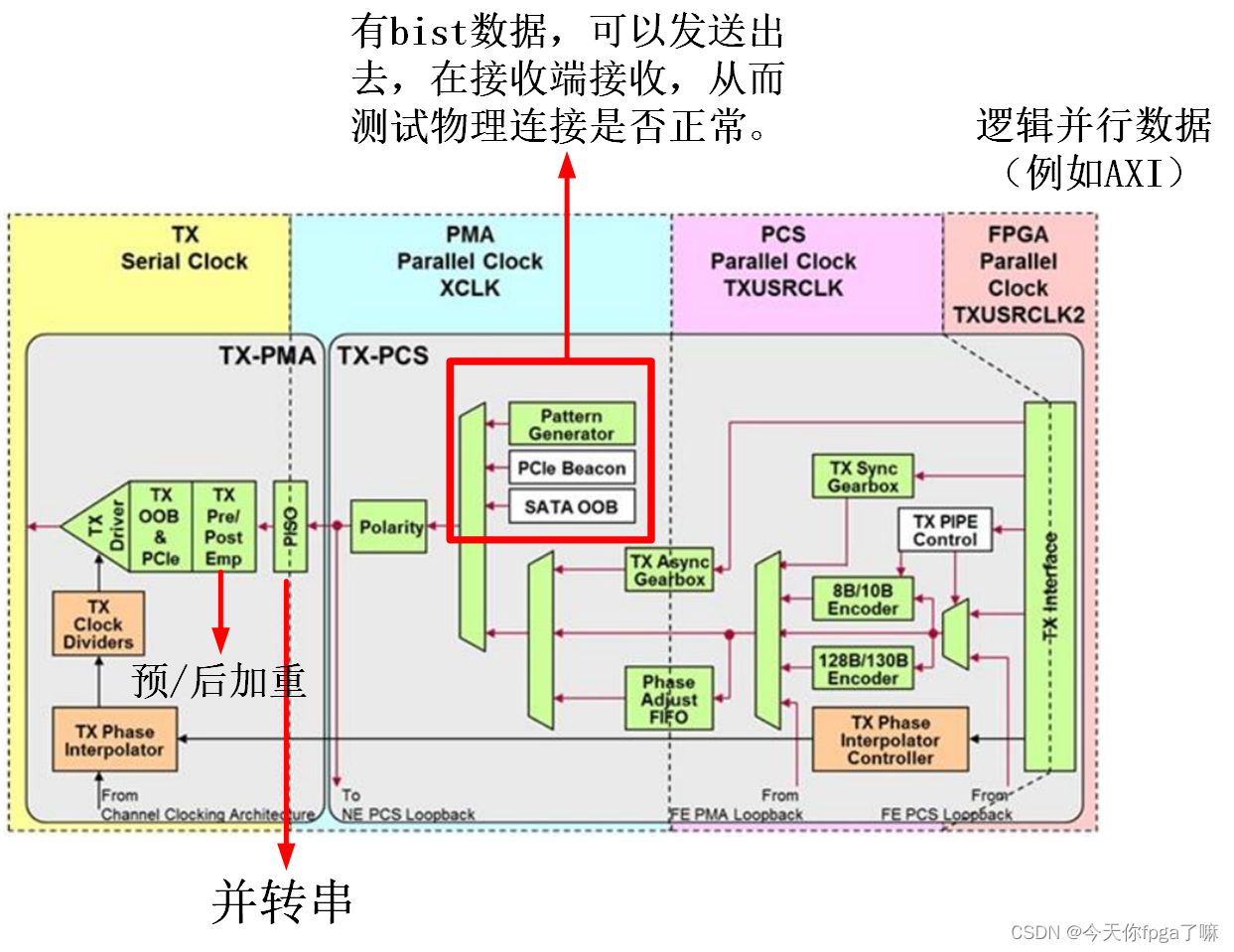

1)TX

其中: 用户的并行数据实际是64bit, PCS中会插入2bit数据让他变成66bit.(做64b/66b编码),但是PCSparallel clock 和PMA parallelclock之间的交互,它并不会一次将66位取走,比如他一次取走32位,两次才会取走64位。多余的两位就取不走了,怎么办?

答:一个周期剩余2bit数据,等到16个周期之后,就满32位了,此时TX Sync Gearbox缓存了32位了,就会告诉用户端,让他停一拍,此时TX Sync Gearbox就把积累的32位传递给PMA parallelclock这边了。

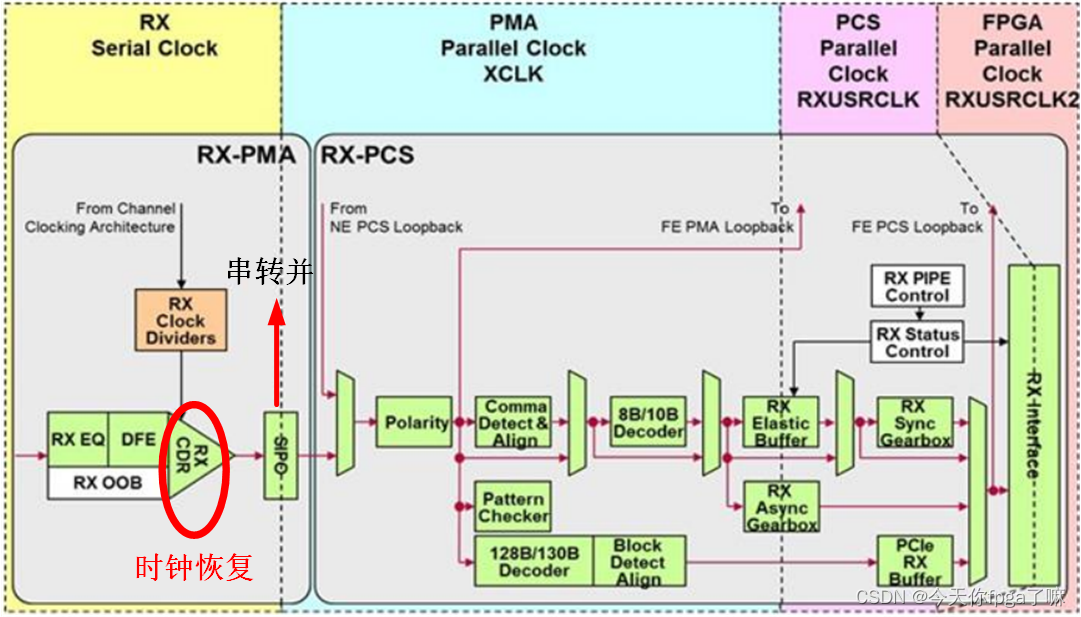

2)RX

其中比较重要的是:Rx-PMA中有CDR(时钟恢复模块),依赖refclk,从数据中将时钟恢复出来。

这篇关于xilinx的高速接口构成原理和连接结构的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!