连接结构专题

xilinx的高速接口构成原理和连接结构

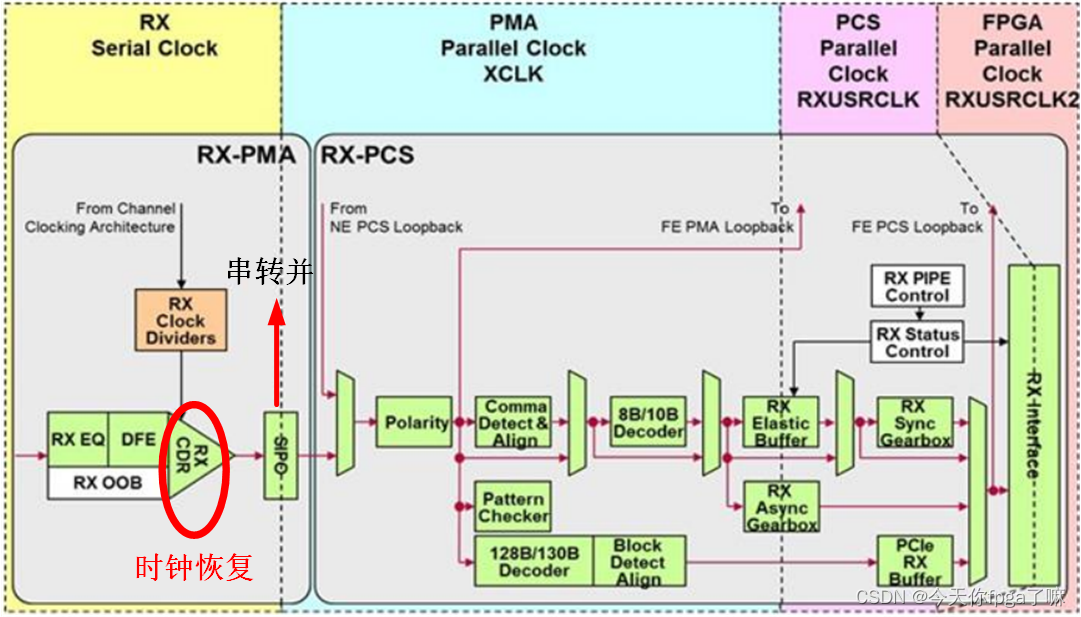

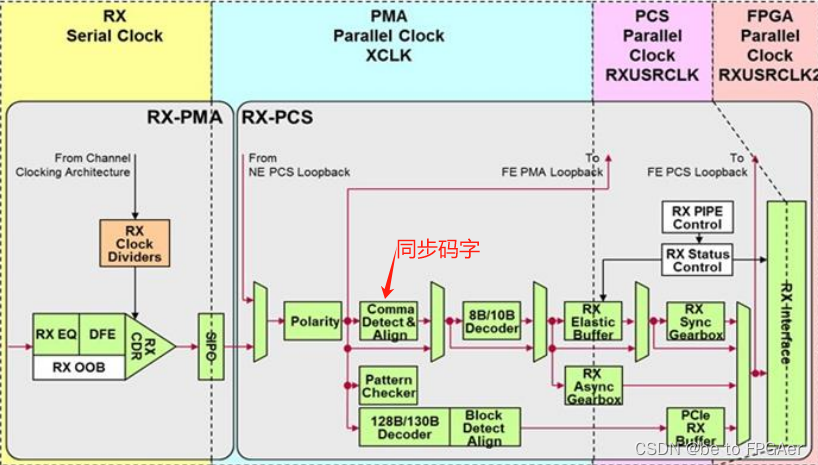

本文来源: V3学院 尤老师的培训班笔记【高速收发器】xilinx高速收发器学习记录Xilinx-7Series-FPGA高速收发器使用学习—概述与参考时钟GT Transceiver的总体架构梳理 文章目录 一、概述:二、高速收发器结构:2.1 QUAD2.1.1 时钟2.1.2 CHANNEL的内部结构:1)TX2)RX 一、概述: Xilinx 的高速接口称

xilinx 的高速接口构成原理和连接结构

Xilinx 的高速接口是 QUAD 为单位的意思是 4 对收发器组成一个 QUAD 这是收发器的最小单元。 例如下方的GTP接口只有一个quad,单个lane能达到5gbit/s,K7 GTX达到16gbit/s等。 SouthCLK 是由相邻的上游 QUAD 提供的时钟或者给相邻下游 QUAD 提供时钟,上图是一个独立的 QUAD。NorthCLK 是由下游的 QUAD 提供时钟,或者给相

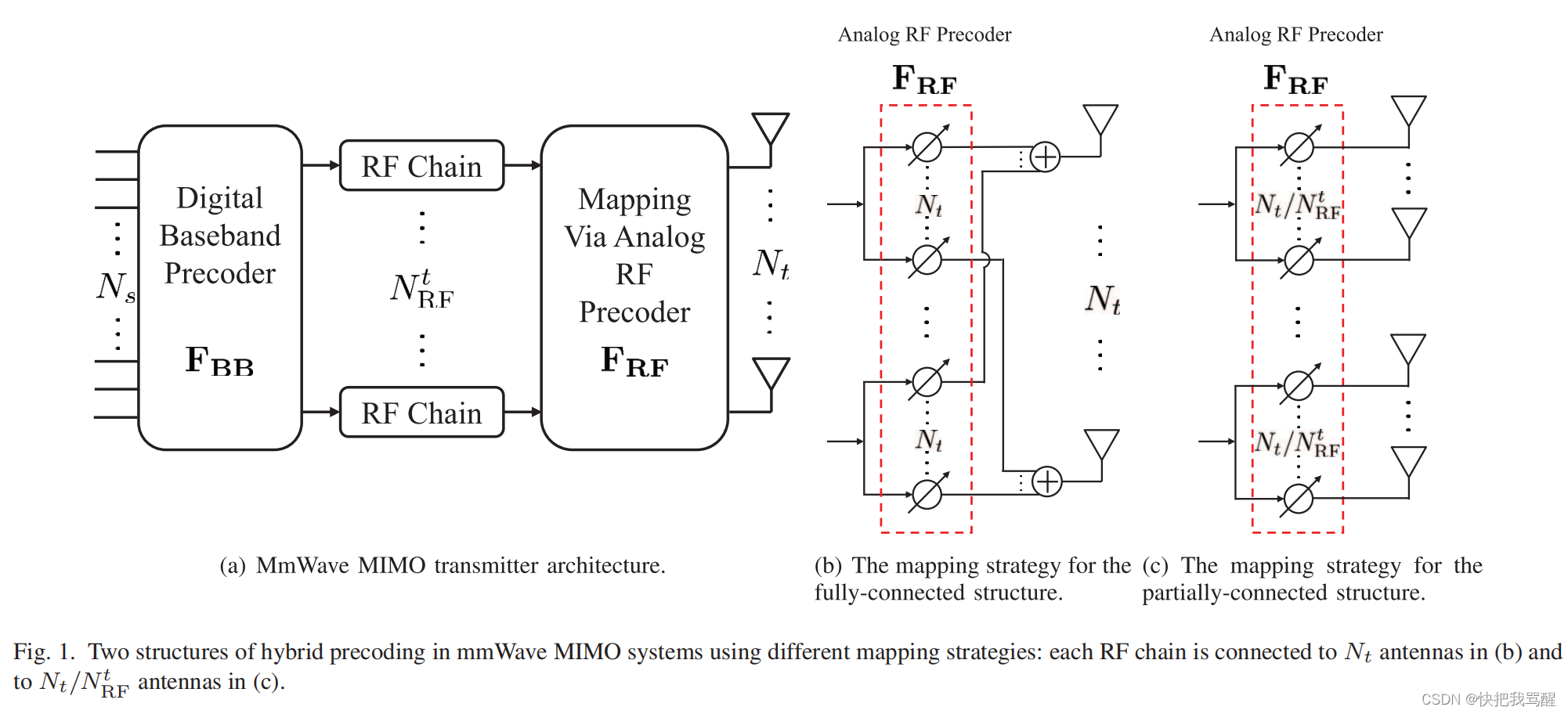

混合预编码(Hybrid Precoding)的全连接结构与子连接结构

A Survey on Hybrid Beamforming Techniques in 5G: Architecture and System Model Perspectives 全连接结构的混合预编码 子连接结构的混合预编码 Alternating Minimization Algorithms for HybridPrecoding in Millimeter Wave MIMO

混合预编码(Hybrid Precoding)的全连接结构与子连接结构

A Survey on Hybrid Beamforming Techniques in 5G: Architecture and System Model Perspectives 全连接结构的混合预编码 子连接结构的混合预编码 Alternating Minimization Algorithms for HybridPrecoding in Millimeter Wave MIMO