原语专题

Xilinx FPGA 原语解析(二):IBUFDS差分输入缓冲器(示例源码及仿真)

目录 前言: 一、原语使用说明 二、原语实例化代码模版 三、使用示例 1.设计文件代码 2.仿真文件代码 3.仿真结果 前言: 本文主要参考资料xilinx手册,《Xilinx 7 Series FPGA and Zynq-7000 All Programmable SoC Libraries Guide for HDL Designs》UG768 (v14.7) Octob

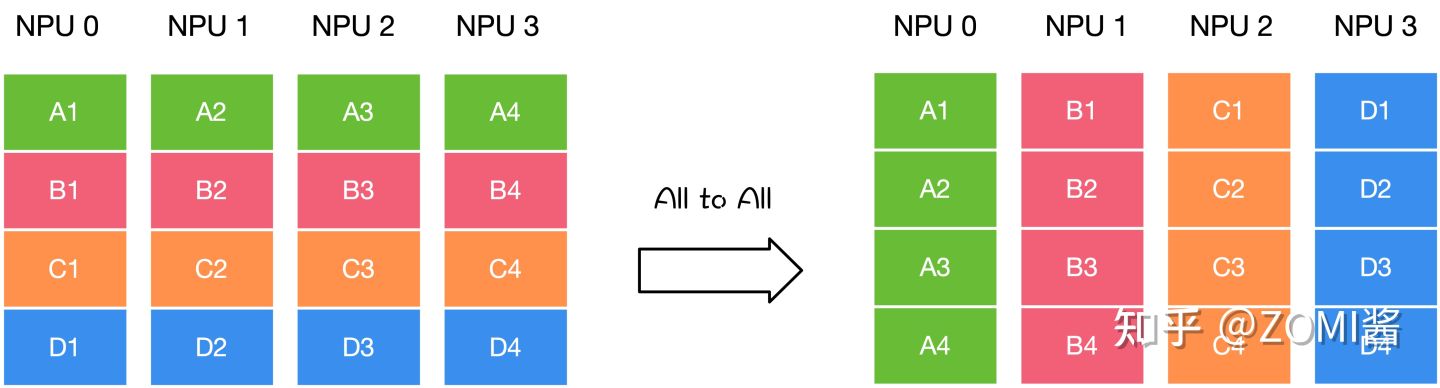

分布式训练硬核技术——通讯原语

针对分布式训练服务器的集群进行架构设计,是为了更好地解决机器学习中分布式训练中的通讯问题。目前机器学习中主要由两种分布式架构: 参数服务器架构(Parameter Server,PS)去中心化架构(Decentralized Network) 其中,分布式训练通常在计算集群上进行,集群的每个节点分别执行一部分计算。不同节点的计算之间有数据依赖和共享,需要将数据在不同节点间传输,这就是通

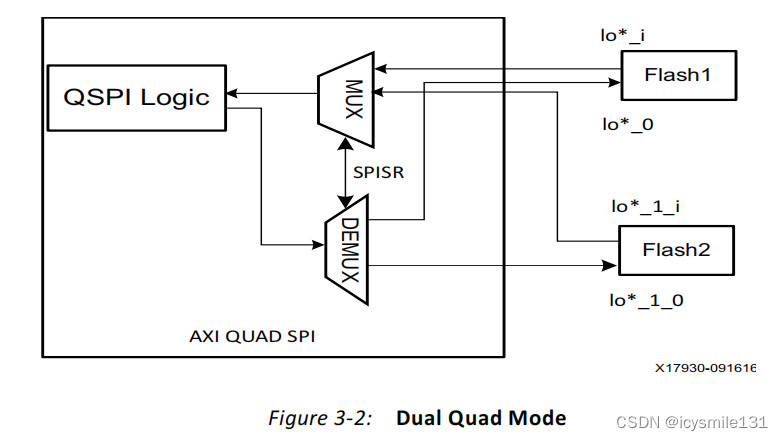

AXI Quad SPI IP核中的STARTUPEn原语参数

启动STARTUPEn Primitive (原语)参数在 FPGA的主 SPI模式下非常有用。当你启用这个参数时,对于 7 系列设备,STARTUPE2 原语会被包含在设计中;而对于 UltraScale™ 设备,则是 STARTUPE3 原语。这些原语在 FPGA 配置后成为IP核的一部分。 1 启用STARTUPEn 原语参数 STARTUPEn(如STARTUPE2或STARTUP

(P24)进程间通信介绍二:死锁 ,信号量与PV原语 ,用PV原语解决司机与售票员问题 ,用PV原语解决民航售票问题 ,用PV原语解决汽车租赁问题

文章目录 1.死锁2.信号量与PV原语3.用PV原语解决司机与售票员问题4用PV原语解决民航售票问题5.用PV原语解决汽车租赁问题 1.死锁 死锁是指多个进程之间相互等待对方的资源,而在得到对方资源之前又不释放自己的资源,这样,造成循环等待的一种现象。如果所有进程都在等待一个不可能发生的事,则进程就死锁了。 进程与进程间的关系 (1)互斥:类似人之间的矛盾关系 2个小孩争抢

C++标准模板(STL)- 迭代器库-迭代器原语-为迭代器各项性质提供统一接口

迭代器库-迭代器原语 迭代器库提供了五种迭代器的定义,同时还提供了迭代器特征、适配器及相关的工具函数。 迭代器分类 迭代器共有五 (C++17 前)六 (C++17 起)种:遗留输入迭代器 (LegacyInputIterator) 、遗留输出迭代器 (LegacyOutputIterator) 、遗留向前迭代器 (LegacyForwardIterator) 、遗留双向迭代器 (Legac

Universal Thresholdizer:将多种密码学原语门限化

参考文献: [LS90] Lapidot D, Shamir A. Publicly verifiable non-interactive zero-knowledge proofs[C]//Advances in Cryptology-CRYPTO’90: Proceedings 10. Springer Berlin Heidelberg, 1991: 353-365.[Shoup00] S

第6章:GO的并发数据结构和同步原语

第6章:GO的并发数据结构和同步原语 并发编程是GO语言的一大特色,它提供了丰富的并发数据结构和同步原语,使得开发者能够更容易地编写并发程序。本章将详细介绍GO语言中的并发数据结构,如通道(channels)、互斥锁(mutexes)、等待组(wait groups)等,以及如何使用这些结构和原语来同步和管理并发操作。 6.1 并发数据结构:通道(Channels) 通道是GO语言中实现并发

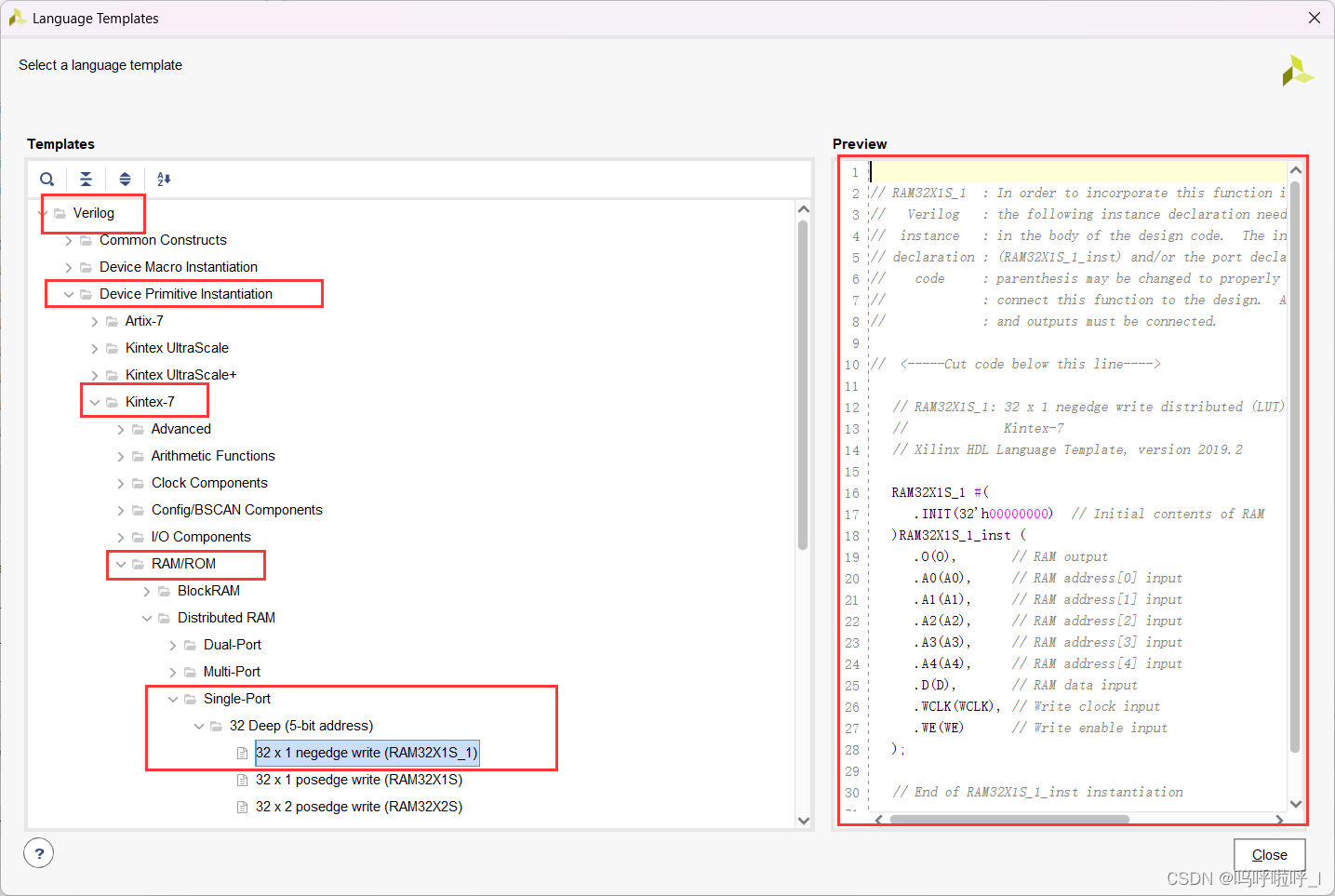

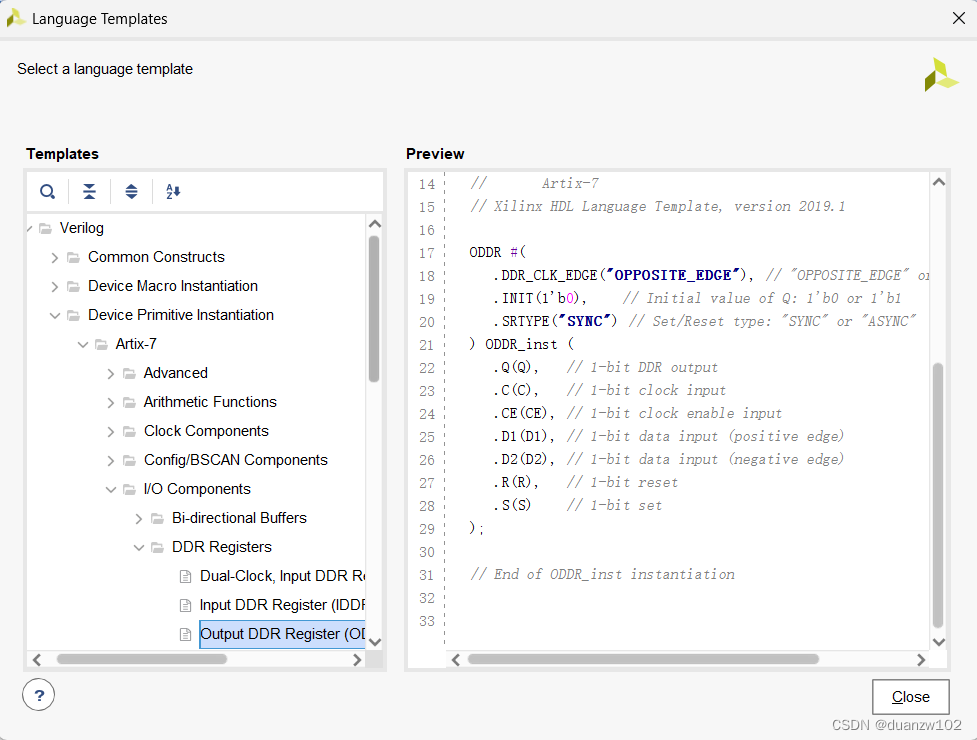

Xinlinx原语在哪查看如何使用/原语示例

1.打开Vivado 2.点击Tools,选择Language Templates 3.选择Language类型、Device Primitive Instantiation(原语)、Kintex-7(芯片系列),之后可以选择自己需要使用的类型,这里以分布式RAM为例,选中32×1的单端口分布式RAM后右侧就会给出例化的示例。

Xlinx相关原语讲解导航页面

原语就是对FPGA底层器件的直接调用,与IP功能是类似的,将原语的参数变成IP配置时的GUI界面参数,可能会更加直观。IP的缺陷在于繁杂,比如SelectIO IP内部包含IDDR、ODDR等等IO转换的功能,如果只想使用单沿转双沿一个功能,那么调用SelectIO IP相比直接使用IDDR原语会麻烦很多。 手册中关于原语的讲解其实是比较枯燥的,在实际使用时,还需要与vivado的Def

DSP48E1 (primitive)原语例化实例2

DSP48E1 (primitive)原语例化实例2 再补充两个比较常用的用法。 1 o <= in1*in2-c OPMODE=7'b0110101 ALUMODE=0001 CARRYIN=1 ALUMODE = 0001 可以实现- Z + (X + Y) - 1 = not (Z) + X + Y。 OPMODE[6:4]=011, Z选择C

DSP48E1 (primitive)原语例化实例

DSP48E1 (primitive)原语例化实例 之前倒腾dsp48e1的时候发现网上虽然有一些文章,但是大部分都是无用的文章, 正如某位同仁说的,高手都忙于泡妞,哪有精力来写文章, 把之前倒腾的代码贴出来供大家参考。 先把OPMODE和ALUMODE贴上,来自网上的文章 OPMODE用来决定下面这个图X,Y,Z这些mux的选择,一时半会看不懂,稍微花点时间是可以看懂的

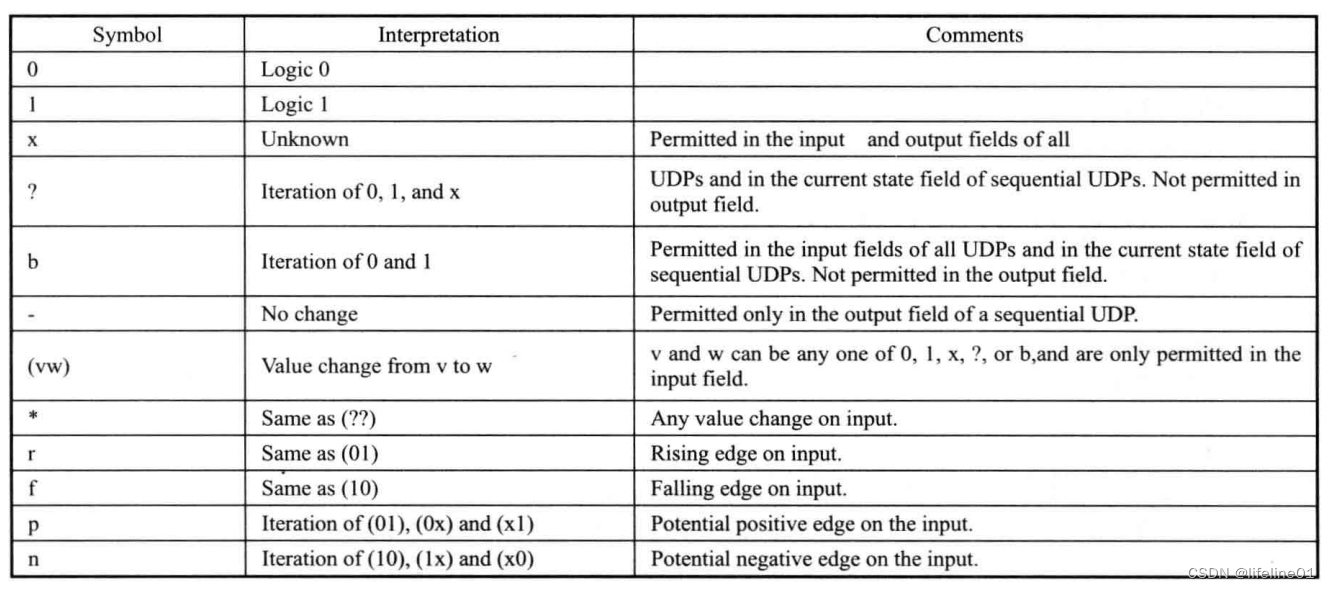

Verilog语法回顾--用户定义原语

目录 用户定义原语 UDP定义 UDP状态表 状态表符号 组合UDP 电平敏感UDP 沿敏感时序UDP 参考《Verilog 编程艺术》魏家明著 用户定义原语 用户定义原语(User-defined primitive,UDP)是一种模拟硬件技术,可以通过设计新的原语单元扩大门原语集合。UDP可以和门原语一样使用,用于表示要模拟的电路。 UDP分为两种: 1.组合U

ZYNQ7000学习——OSERDESE2原语学习

ZYNQ学习——OSERDESE2原语 OSERDESE2原语端口 OSERDESE2 Attributes 时钟 CLK:高速串行时钟。 CLKDIV:并行时钟,用于并串转换;由CLK分频而来。 二者需相位相同。 唯一有效的时钟分配方式: 1、CLK driven by BUFIO, CLKDIV driven by BUFR; 2、CLK and CLKDIV driven

Vivado原语模板

1.原语的概念 原语是一种元件! FPGA原语是芯片制造商已经定义好的基本电路元件,是一系列组成逻辑电路的基本单元,FPGA开发者编写逻辑代码时可以调用原语进行底层构建。 原语可分为预定义原语和用户自定义原语。预定义原语为如and/or等门级原语不需要例化,可以直接调用。用户自定义原语在Verilog中使用非常简单,将其作为模块名直接例化即可。Vi

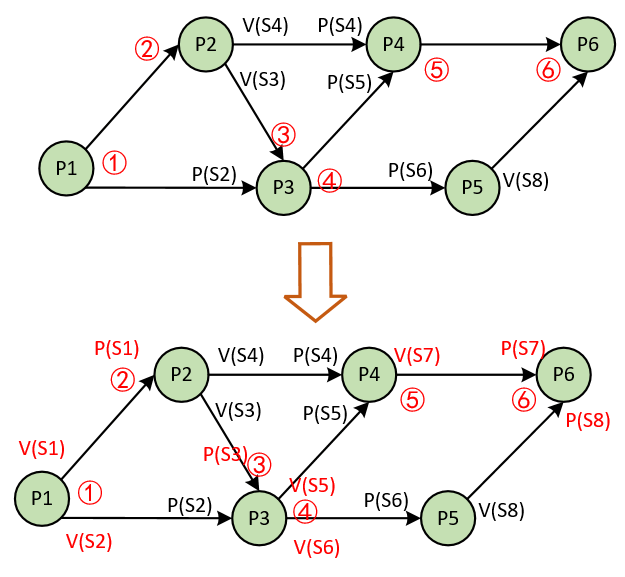

嵌入式基础知识-信号量,PV原语与前趋图

本篇来介绍信号量与PV原语的一些知识,并介绍其在前趋图上的应用分析。本篇的知识属于操作系统部分的通用知识,在嵌入式软件开发中,同样会用到这些知识。 1 信号量 信号量是最早出现的用来解决进程同步与互斥问题的机制(可以把信号量视为一个加锁标志位,实现对临界资源互斥的访问)。 信号量是一个整数: 当信号量S>=0时,代表可供并发使用的资源数量当信号量S<0时,代表已经没有可用资源,S的绝对值表

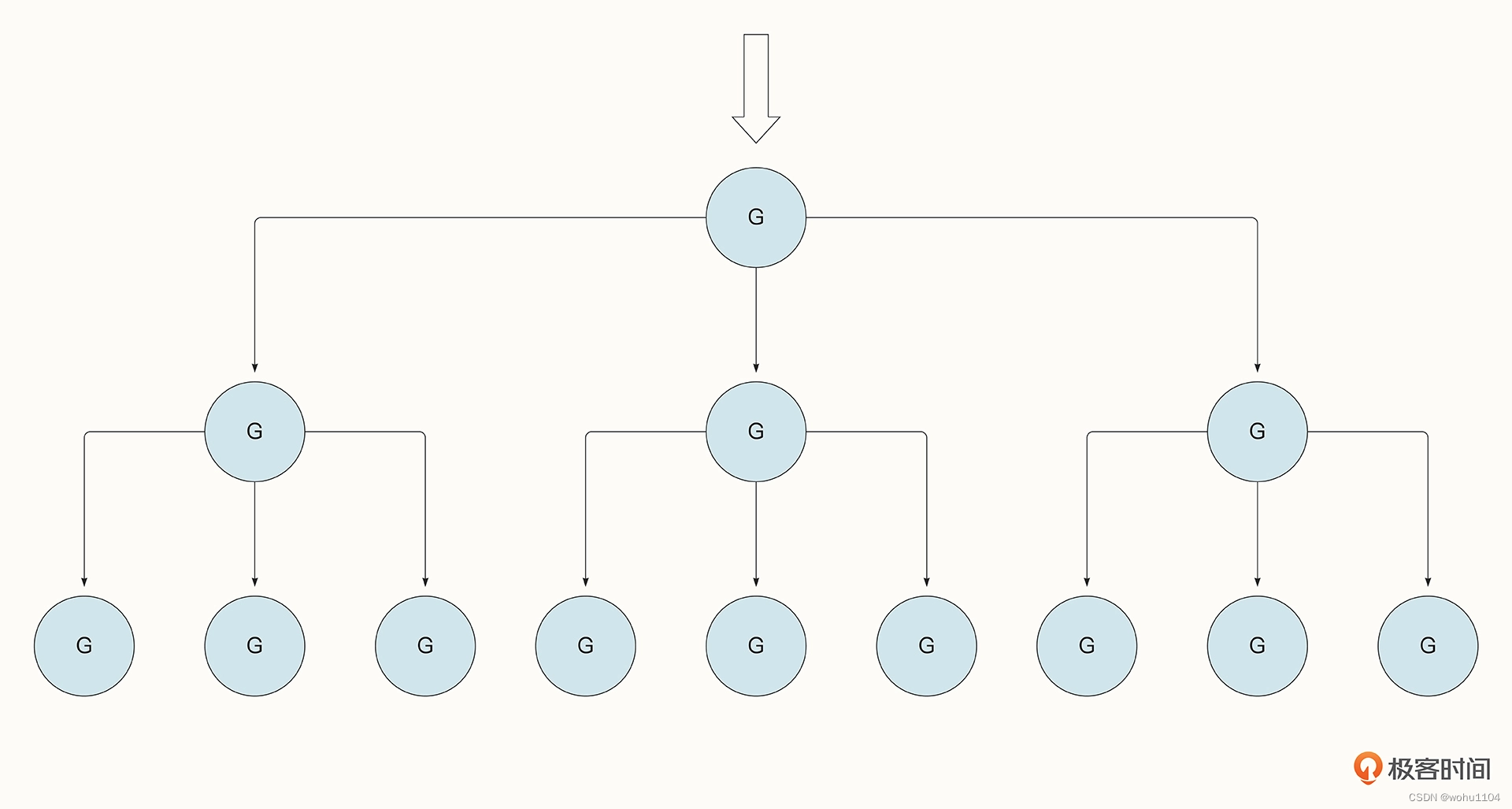

LLM分布式训练第一课(通讯原语)

这个系列作为TFLOPS和显存消耗的续篇,今天开始正式连载 上一部地址: LLM 参数,显存,Tflops? 训练篇(5) (qq.com) 前一篇文章举了65B模型的训练所消耗的显存的案例,如果把条件降低一点,我们看一下7B的模型需要多少显存? 2byte的模型静态参数权重(以16bit存储) = 14G 2byte的模型更新参数权重 (以16bit存储)= 14G 2byte的梯

Linux进程管理:(二)进程调度原语

文章说明: Linux内核版本:5.0 架构:ARM64 参考资料及图片来源:《奔跑吧Linux内核》 Linux 5.0内核源码注释仓库地址: zhangzihengya/LinuxSourceCode_v5.0_study (github.com) 进程调度的概念比较简单,假设在一个单核处理器的系统中,同一时刻只有一个进程可以拥有处理器资源,那么其他的进程只能在就绪队列(runq

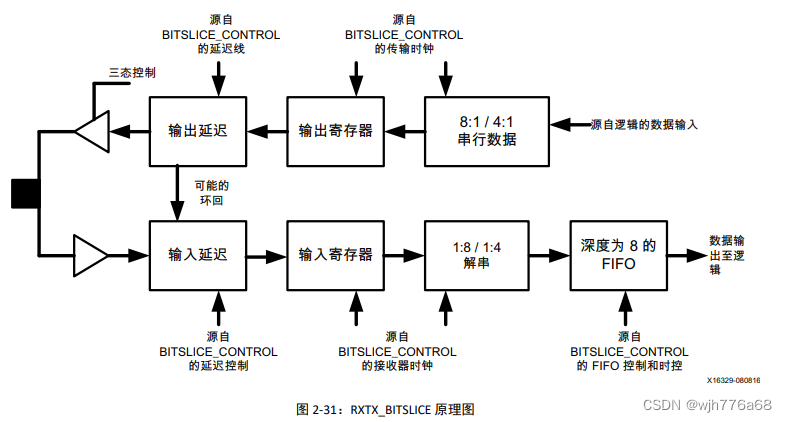

【SelectIO】bitslice原语学习记录

基本概念 在Ultrascale (plus)系列上的FPGA中,Xilinx引入了bitslice硬核,它取代了7系列上的IDELAYCTRL/IODELAY/IOSERDES/IODDR系列硬核,用于为HP(High Performance)类型Bank上的IO接口提供串并转化、信号延时、三态控制等功能。Xilinx为bitslice硬核提供了TXRX_BITSLICE/TX_BIT

Android游戏开发–使用OpenGL ES显示图形元素(原语)

这是android OpenGL ES系列的第2部分。 在上一篇文章中,我们研究了如何设置android项目以将提供的OpenGL视图与渲染器一起使用。 您可以使用该文章中的项目作为模板。 在开始展示事物之前,我们必须了解3D编程的一些基本概念,并熟悉术语。 我真的是基本几何。 3D图形发生在笛卡尔坐标系中 。 这意味着所使用的坐标系具有三个维度。 X , Y和Z。 传

Go 学习笔记(66)— Go 并发同步原语(sync.Mutex、sync.RWMutex、sync.Once)及并发模型(ping-pong 模式、fan-in 模式、fan-out 模式)

1. 竞态条件 一旦数据被多个线程共享,那么就很可能会产生争用和冲突的情况。这种情况也被称为竞态条件(race condition),这往往会破坏共享数据的一致性。 举个例子,同时有多个线程连续向同一个缓冲区写入数据块,如果没有一个机制去协调这些线程的写入操作的话,那么被写入的数据块就很可能会出现错乱。 比如,在线程 A 还没有写完一个数据块的时候,线程 B 就开始写入另外一个数据块了。

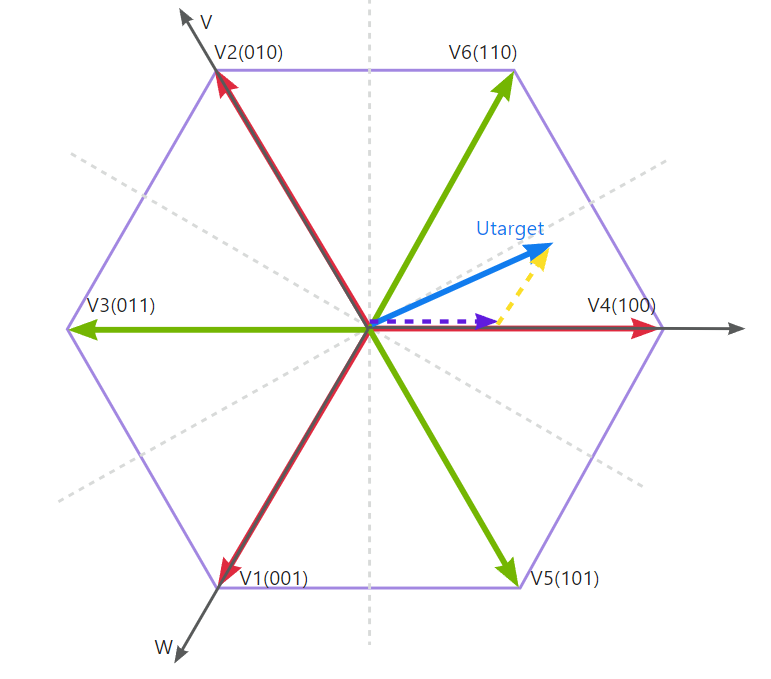

直流无刷电机FOC控制原语

直流无刷电机FOC控制原语 文章目录 直流无刷电机FOC控制原语1. 前言2. FOC控制原理2.1 磁的问题2.2 电的问题 3. 如何获取 `I_feedback` ?4. 如何调整 `I_feedback`?5. 总结 1. 前言 在这之前,我写了三篇关于直流无刷电机 FOC 矢量控制的文章,从理论驱动原理到实际控制实现。三篇博客发布后,受到大家的广泛好评,我也受到大家

Python Asyncio 库之同步原语常用函数详解

前记 Asyncio的同步原语可以简化我们编写资源竞争的代码和规避资源竞争导致的Bug的出现。 但是由于协程的特性,在大部分业务代码中并不需要去考虑资源竞争的出现,导致Asyncio同步原语被使用的频率比较低,但是如果想基于Asyncio编写框架则需要学习同步原语的使用。 0.基础 同步原语都是适用于某些条件下对某个资源的争夺,在代码中大部分的资源都是属于一个代码块,而Python对于代码块

信号量机制:原语PV操作的实现|源代码和解释

信号量机制 **目的:**实现互斥访问共享资源,实现进程同步。 一共3个操作 初始化P原语V原语 类型: 整型信号量:只包含临界资源数量。当资源不足的时候会自旋,会发生忙等,违背“让权等待”记录型信号量:包含等待队列等信息。当资源不足的时候,会进入等待队列。 单词解释: 源于荷兰语 P-V原语操作 P = plantinga = Probeer(’try’)=尝试 V= Verhoog

Go语言中的`sync`包同步原语

通过sync包掌握Go语言的并发 并发是现代软件开发的基本方面,而Go(也称为Golang)为并发编程提供了一套强大的工具。在Go中用于管理并发的基本包之一是sync包。在本文中,我们将概述sync包,并深入探讨其最关键的同步原语之一:等待组(Wait Groups)。 sync包概述 sync包是Go的标准库包,为并发编程提供了同步原语。它为开发人员提供了协调和同步Goroutines

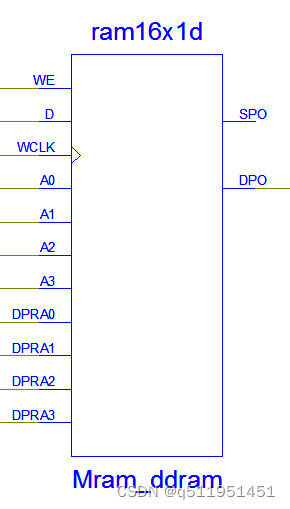

verilog语法进阶-分布式ram原语

概述 官方提供的原语 RAM16X1S_1 #(.INIT(16'h0000) // Initial contents of RAM) RAM16X1S_1_inst (.O(O), // RAM output.A0(A0), // RAM address[0] input.A1(A1), // RAM address[1] input.A2(A2),

Xilinx原语详解——IBUFDS OBUFDS

在使用FPGA时,往往会用到一些差分信号,比如HDMI接口,LVDS接口的ADC、显示器等等设备,而FPGA内部往往只会使用单端信号,就需要完成单端信号和差分信号的相互转换,xilinx提供了两个原语对所有IO信号实现差分和单端的转换,IBUFDS将FPGA输入的差分信号转换为单端信号,而OBUFDS负责把FPGA内部的单端信号转换为差分信号输出。 1、IBUFDS IBUFDS是一个