本文主要是介绍ZYNQ7000学习——OSERDESE2原语学习,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

ZYNQ学习——OSERDESE2原语

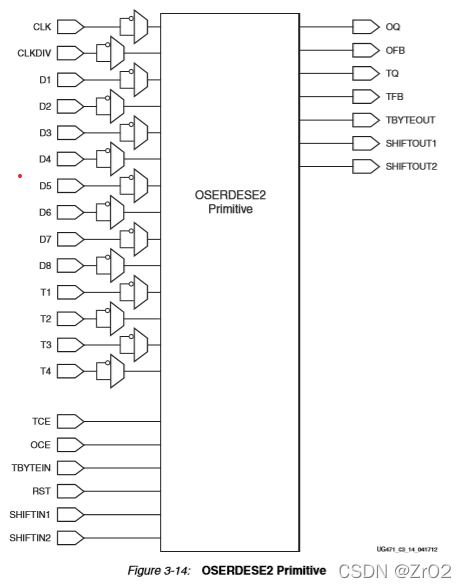

OSERDESE2原语端口

OSERDESE2 Attributes

时钟

CLK:高速串行时钟。

CLKDIV:并行时钟,用于并串转换;由CLK分频而来。

二者需相位相同。

唯一有效的时钟分配方式:

1、CLK driven by BUFIO, CLKDIV driven by BUFR;

2、CLK and CLKDIV driven by CLKOUT[0:6] of the same MMCM or PLL。

复位

OSERDESE2复位为高电平有效(若用PLL的locked信号作为复位时需加反相)。

数据线

输入

D1~D8:并行数据线,D1为发送的第一位。(可通过级联第二级slave模式的OSERDESE2原语来拓展输入数据宽度)

输出

OQ:串行数据输出端口,该端口无法驱动ODELAYE2。

OFB:串行数据输出端口,用于驱动ODELAYE2原语或发送反馈到ISERDESE2。

OP与OFB输出波形相同。

TQ:连接三态并串转换器的输出于IOB的三态输入。

TFB:

拓展输入数据位宽

- 仅可在DDR模式下,可将输出数据位宽提升至10:1或14:1。

- 需要将MASTER的 SHIFTOUT 端口连接至SLAVE的 SHIFTIN 端口。

- 输出必须通过buffer转成差分输出,否则将不能拓展。

- 不能用补充性的单端电平标准,eg: DIFF_HSTL and DIFF_SST

| Data Width | Slave Inputs Used |

|---|---|

| 10 | D3–D4 |

| 14 | D3–D8 |

三态

若工程无需使用到三态控制,则相关的控制信号(TCE、TBYTEIN、T1~T4)置0即可。

输入到输出延迟

延迟定义:

CLKDIV上升沿输入数据进入到OSERDESE2,到OQ输出串行数据流的第一位。

注:CLKDIV上沿采样数据,输出延迟单位为CLK周期。

OSERDESE2使用示例

代码

module OSERDESE2_test (// input;input clk,input [7:0] data,// output;output data_out,output data_out_test,output data_out_tri_state

);// wire TFB;// wire TQ;// wire clk_pll;wire clk_50M; //wire rst_n;OSERDESE2 #(.DATA_RATE_OQ ("DDR"), // DDR, SDR.DATA_RATE_TQ ("DDR"), // DDR, BUF, SDR.DATA_WIDTH (8), // Parallel data width (2-8,10,14).SERDES_MODE ("MASTER"), // MASTER, SLAVE.TBYTE_CTL ("FALSE"), // Enable tristate byte operation (FALSE, TRUE).TBYTE_SRC ("FALSE"), // Tristate byte source (FALSE, TRUE).TRISTATE_WIDTH (1) // 3-state converter width (1,4))OSERDESE2_inst (.OFB (data_out_test), // 1-bit output: Feedback path for data.OQ (data_out), // 1-bit output: Data path output// SHIFTOUT1 / SHIFTOUT2: 1-bit (each) output: Data output expansion (1-bit each).SHIFTOUT1 (),.SHIFTOUT2 (),.TBYTEOUT (), // 1-bit output: Byte group tristate.TFB (), // 1-bit output: 3-state control.TQ (data_out_tri_state), // 1-bit output: 3-state control.CLK (clk_200M), // 1-bit input: High speed clock.CLKDIV (clk_50M), // 1-bit input: Divided clock// D1 - D8: 1-bit (each) input: Parallel data inputs (1-bit each).D1 (data[0]),.D2 (data[1]),.D3 (data[2]),.D4 (data[3]),.D5 (data[4]),.D6 (data[5]),.D7 (data[6]),.D8 (data[7]),.OCE (1'b1), // 1-bit input: Output data clock enable.RST (~rst_n), // 由于使用锁相环,因此需将复位信号反相// SHIFTIN1 / SHIFTIN2: 1-bit (each) input: Data input expansion (1-bit each).SHIFTIN1 (1'b0),.SHIFTIN2 (1'b0),// T1 - T4: 1-bit (each) input: Parallel 3-state inputs.T1 (1'b0),.T2 (1'b0),.T3 (1'b0),.T4 (1'b0),.TBYTEIN (1'b0), // 1-bit input: Byte group tristate.TCE (1'b0) // 1-bit input: 3-state clock enable);// PLL;clk_wiz_0 instance_name(// Clock out ports.clk_50M (clk_50M), // output clk_50M.clk_200M (clk_200M), // output clk_200M// Status and control signals.locked (rst_n), // output locked// Clock in ports.clk_in (clk)); // input clk_inendmodule

TB

`timescale 1ns/1nsmodule tb_OSERDESE2_test ();reg clk = 1'b0;always #5 clk = ~clk;reg [7:0] data = 8'b0;wire data_out;wire data_out_test;wire data_out_tri_state;task delay_clks;input [7:0] number;begin repeat(number) @(posedge clk);#1;endendtaskinitial begindelay_clks(100);data = 8'b1010_1010;delay_clks(10);data = 8'b1001_0011;delay_clks(10);data = 8'b1111_1111;delay_clks(10);data = 8'b0;endOSERDESE2_test U_OSERDESE2_TEST (.clk (clk),.data (data),.data_out (data_out),.data_out_test (data_out_test),.data_out_tri_state (data_out_tri_state));endmodule

仿真结果

1时刻:clk_50M即CLKDIV上升沿采样输入数据。

2时刻:由查表可知,DDR、8:1时输入到输出延迟为4个CLK周期,即4个clk_200M周期,因此在2时刻开始输出串行化的数据。而输出数据由D1即data[0]开始,因此数据实际输出为01010101,后续输出以此类推。

这篇关于ZYNQ7000学习——OSERDESE2原语学习的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!