zynq7000专题

基于ZYNQ7000的交叉编译工具链Qt+OpenCV+ffmpeg等库支持总结

最近刚刚接触XILINX的ZYNQ板,刚接触没有十天。XILINX定位它为SOC,我也很认同,起码比TI定位MPU为SOC强很多。据说今年TI的最新产品也加入了ZYNQ板。 之前的MIPS处理器设计与实现的项目就算做告一段落,搞了将近7个月,成果显著,收获颇多,最近打算搞搞ZYNQ。 之前MIPS也有一套交叉编译工具,不过是老师提供的,自己也尝试搞了搞,太辛苦了,而且也没什么成果,因为我

Zynq7000 系列FPGA模块化仪器

• 基于 XilinxXC7Z020 / 010 / 007S • 灵活的模块组合 • 易于嵌入的紧凑型外观结构 • 高性能的 ARM Cortex 处理器 • 成熟的 FPGA 可编程逻辑 ,基于 IP 核的软件库 FPGA 控制器 Zynq7000 系列模块是基于 Xilinx XC7Z020/010/007S 全可编程片上系统 (SoC) 的 SOM(模块系统)板,属于 Xil

Zynq7000系列中的时钟管理

PS(处理系统)时钟子系统生成的所有时钟都源自三个可编程PLL(锁相环)中的一个:CPU、DDR和I/O。时钟子系统的主要组件如图25-1所示。 在正常工作期间,PLL被启用,并由PS_CLK时钟引脚驱动。在启用PLL之前需要保持PS_CLK稳定,并且必须保持其稳定性。时钟频率必须在数据手册中指定的工作范围内。 如果PLL被旁路,PS_CLK引脚上的时钟信号将作为各种时钟发生器的源。PS_CLK

ZYNQ7000学习——OSERDESE2原语学习

ZYNQ学习——OSERDESE2原语 OSERDESE2原语端口 OSERDESE2 Attributes 时钟 CLK:高速串行时钟。 CLKDIV:并行时钟,用于并串转换;由CLK分频而来。 二者需相位相同。 唯一有效的时钟分配方式: 1、CLK driven by BUFIO, CLKDIV driven by BUFR; 2、CLK and CLKDIV driven

MYIR-ZYNQ7000系列-zturn教程(27):lwip测试

开发板环境:vivado 2017.4 ,开发板型号xc7z010clg400-1,这个工程主要是进行eth测试 链接:https://pan.baidu.com/s/1dUm68xhKjobq1C6st9Zn3A 提取码:o868 step1 新建一个vivado工程 step 2 导入zynq配置文件 点击Create Block Design 点击OK 调用z

zynq7000 PL读写DDR3----实验笔记

环境:vivado2018.3 芯片: xc7z100ffg900-2 本实验参考资料主要来源:https://www.eefocus.com/antaur/blog/17-08/423773_0818c.html 实验目的:将ADC接收的数据先存入DDR3,待PS端读取完成后,再存入一批。 1、工程规划 DDR芯片的管脚是绑定到Zynq的DDR接口上的。 而Zynq系统的

Xilinx Vivado zynq7000 入门笔记

http://www.wodefanwen.com/lhd_3076u8kilp4i6jp0x0cx_1.html IP Integrator flow 1. 创建RTL工程 2. 创建IP Integrator Block Design 3. 添加zynq 处理器 ip中搜索zynq,添加zynq7 Processing System,其中的BFM版本为先前的IP处理器版本。鼠标右键点击F

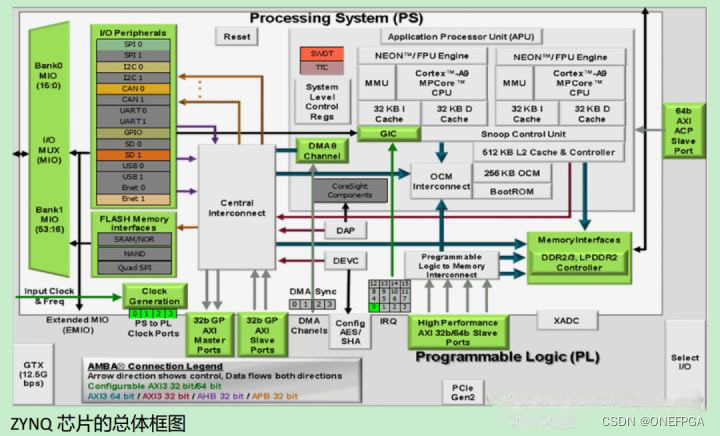

FPGA系统性学习笔记连载_Day4 Xilinx ZYNQ7000系列 PS、PL、AXI 、启动流程基本概念篇

四、ZYNQ 芯片内部用硬件实现了 AXI 总线协议,包括 9 个物理接口,分别为 AXI-GP0~AXIGP3,AXI-HP0~AXI-HP3,AXI-ACP 接口。 1、AXI_ACP 接口,是 ARM 多核架构下定义的一种接口,中文翻译为加速器一致性端口,用来管理 DMA 之类的不带缓存的 AXI 外设,PS 端是 Slave 接口。 2、AXI_HP 接口,是高性能/带宽的 AXI3.

Zynq7000简介

Zynq7000简介 Zynq7000由来 Zynq是Xilinx公司推出的一个可扩展处理平台,其将通用基础双ARMCortex-A9MPCore处理器系统作为“主系统”,结合低功耗28nm工艺技术,以实现高度的灵活性、强大的配置功能和高性能。由于该新型器件的可编程逻辑部分基于赛灵思28nm7系列FPGA,因此该系列产品的名称中添加了“7000”,以保持与7系列FPGA的一致性,同时也方便日后

ZYNQ7000 #3 - Linux环境下在用户空间使用AXI-DMA进行传输

本文使用Petalinux搭建相关linux环境,在vivado中搭建了一个简单的PS -> AXI-DMA -> AXI-FIFO -> AXI-DMA -> PS的测试环路。使用了国外开源的 xilinx_axidma 操作库,完成了用户空间上的AXI-DMA传输。使用库相对来说更加方便容易上手,不需要过多的了解linux设备驱动中如何调用DMA进行传输 目录 0 - 引言 1 - 准备

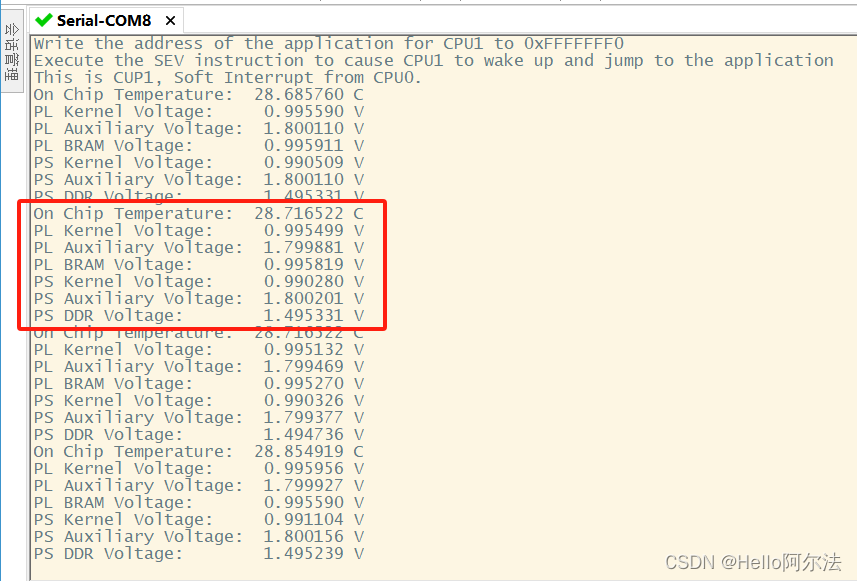

【ZYNQ】ZYNQ7000 XADC 及其驱动示例

XADC 简介 ZYNQ SoC 的 XADC 模块包括两个 12 位的模数转换器,转换速率可以达到 1MSPS(每秒一百万次采样)。它带有片上温度和电压传感器,可以测量芯片工作时的温度和供电电压。 在 7 系列的 FPGA 中,XADC 提供了 JTAG 和 DRP(dynamic reconfiguration port)接口,用于访问其内部的状态和控制寄存器。在 ZYNQ-7000 So

基于Zynq7000平台VxWorks6.9开发应用——SMP多核任务篇

前言 本篇文章主要讲解在Xilinx ZedBoard上开发基于VxWorks6.9 SMP架构的多核任务调度,创建两个任务,并分别指定运行在Zynq7000上的两个CortexA9核上,研究多核CPU根据使用场景进行最优化任务部署。本文力求讲述清楚SMP基本概念,以及系统适配SMP模式的要求,SMP模式多任务运行在CPU实现方法,并配套完整的演示软件和相关代码进行验证。下面将从

Xilinx zynq7000移植Mjpg_streamer

PC-Linux 版本:Ubuntu 14.04 Arm-Linux 内核版本:Linux version 3.17.0-xilinx (ubuntu@ubuntu) (gcc version 4.6.3 (Sourcery CodeBench Lite 2012.03-79) ) #29 SMP PREEMPT Sat Sep 29 19:26:22 PDT 2018 Jpeg版