本文主要是介绍FPGA系统性学习笔记连载_Day4 Xilinx ZYNQ7000系列 PS、PL、AXI 、启动流程基本概念篇,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

四、ZYNQ 芯片内部用硬件实现了 AXI 总线协议,包括 9 个物理接口,分别为 AXI-GP0~AXIGP3,AXI-HP0~AXI-HP3,AXI-ACP 接口。

1、AXI_ACP 接口,是 ARM 多核架构下定义的一种接口,中文翻译为加速器一致性端口,用来管理 DMA 之类的不带缓存的 AXI 外设,PS 端是 Slave 接口。

2、AXI_HP 接口,是高性能/带宽的 AXI3.0 标准的接口,总共有四个,PL 模块作为主设备连接。主要用于 PL 访问 PS 上的存储器(DDR 和 On-Chip RAM)

3、AXI_GP 接口,是通用的 AXI 接口,总共有四个,包括两个 32 位主设备接口和两个 32 位从设备接口

一、ZYNQ基本结构

ZYNQ7000系列分为 Artix-7 Kintex-7 Virtex-7,

二、ZYNQ7020 分为PS端、PL端

PS: 处理系统 (Processing System) , 就是与 FPGA 无关的 ARM 的 SOC 的部分。

PL: 可编程逻辑 (Progarmmable Logic), 就是 FPGA 部分。

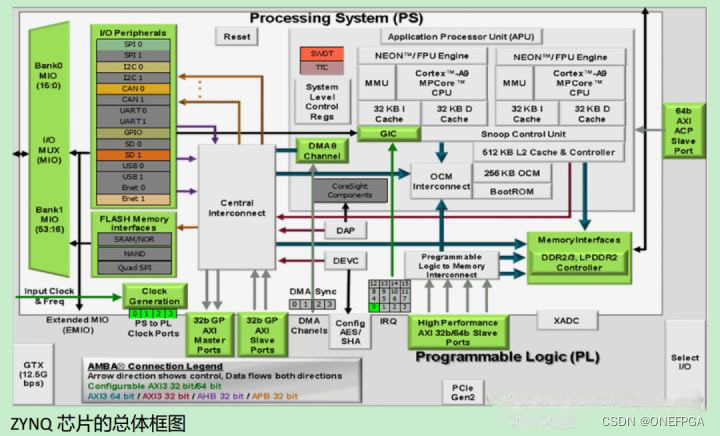

ZYNQ7020的整体架构如下图所示

Zynq 就是两大功能块,PS 部分和 PL 部分, 说白了,就是 ARM 的 SOC 部分,和 FPGA部分。其中,PS 集成了两个 ARM Cortex™-A9 处理器,AMBA®互连,内部存储器,外部储器接口和外设。这些外设主要包括 USB 总线接口,以太网接口,SD/SDIO 接口,I2C 总线接口,CAN 总线接口,UART 接口,GPIO 等。

三、PS 和 PL 互联技术

3.1、ZYNQ 作为首款将高性能 ARM Cortex-A9 系列处理器与高性能 FPGA 在单芯片内紧密结合的产品,为了实现 ARM 处理器和 FPGA 之间的高速通信和数据交互

3.2、发挥 ARM 处理器和 FPGA的性能优势,需要设计高效的片内高性能处理器与 FPGA 之间的互联通路。 本节,我们就将主要介绍 PS 和 PL 的连接,让用户了解 PS 和 PL 之间连接的技术。

3.3、在具体设计中我们往往不需要在连接这个地方做太多工作,我们加入 IP 核以后, 系统会自动使用 AXI 接口将我们的 IP 核与处理器连接起来,我们只需要再做一点补充就可以了。

AXI 全称 Adva

这篇关于FPGA系统性学习笔记连载_Day4 Xilinx ZYNQ7000系列 PS、PL、AXI 、启动流程基本概念篇的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!