oserdese2专题

ZYNQ7000学习——OSERDESE2原语学习

ZYNQ学习——OSERDESE2原语 OSERDESE2原语端口 OSERDESE2 Attributes 时钟 CLK:高速串行时钟。 CLKDIV:并行时钟,用于并串转换;由CLK分频而来。 二者需相位相同。 唯一有效的时钟分配方式: 1、CLK driven by BUFIO, CLKDIV driven by BUFR; 2、CLK and CLKDIV driven

FPGA OSERDESE2

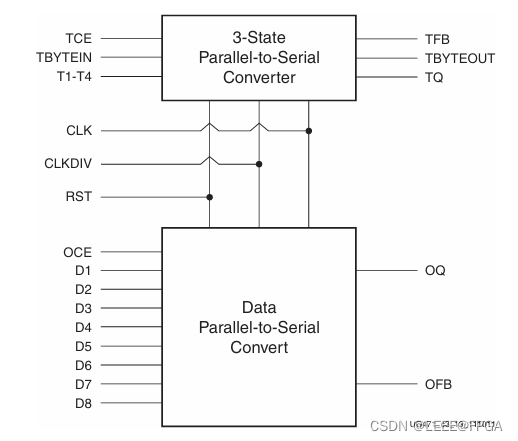

Output Parallel-to-Serial Logic Resources (OSERDESE2) OSERDESE2 在Xilinx 7 系列器件是一款专用的并行至串行转换器,具有特定的时钟和逻辑资源,旨在促进高速源同步接口的实现。每个OSERDESE2模块都包括一个专用的数据串行器和 3 状态控制。数据和 3 态串行器都可以在 SDR 和 DDR 模式下进行配置。数据序列化最高可达

Xilinx LVDS Output——OSERDESE2

Xilinx LVDS Output——OSERDESE2 首先,需要阅读官方提供的使用手册:ug471_7Series_SelectIO.pdf ,Page161 ~ Page173; 先这么理解 LVDS输出,目的是将并行数据,变成时钟频率比较高的串行输出; 可以拆分为两部分: 将串行数据的clock进行倍频;将数据排列成倍频之后要输出的顺序;接输出端口,xdc约束成LVDS输出的电

基于FPGA的HDMI编码模块设计——OSERDESE2

前文通过ODDR实现了HDMI数据编码的单沿与双沿采样的转换,如下图1所示: 图1 ODDR实现单沿转双沿 上图先通过拼接逻辑和并串转换,将10位并行数据先转换为2路串行数据,然后通过ODDR将两路串行的单沿数据转换为1路双沿采样的串行数据。Xilinx还存在一个原语,可以直接将并行的单沿数据转换为串行的双沿采样数据,与ODDR复用相同的硬件资源OLOGIC,就是OSERD