本文主要是介绍【SelectIO】bitslice原语学习记录,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

在Ultrascale (plus)系列上的FPGA中,Xilinx引入了bitslice硬核,它取代了7系列上的IDELAYCTRL/IODELAY/IOSERDES/IODDR系列硬核,用于为HP(High Performance)类型Bank上的IO接口提供串并转化、信号延时、三态控制等功能。Xilinx为bitslice硬核提供了TXRX_BITSLICE/TX_BITSLICE/RX_BITSLICE/BITSLICE_CONTROL/TX_BITSLICE_TRI/RIU_OR这些与bitslice硬核接口一致的原生原语便于用户直接调用例化。同时为了提供向前兼容性,IDELAYCTRL/IODELAY/IOSERDES/IODDR系列原语作为组件原语仍能继续使用,在综合时会被软件综合为bitslice。

使用bitslice原生原语的优势在于其能够对位于一个字节组上的接口进行批量控制,这对于存储控制器(如DDR)的接口信号时序的优化十分有效。此外bitslice在接收侧增加了一个异步FIFO,便于用户逻辑通过用户时钟读取数据。

在Vivado的综合/实现设计界面,选择package pin选项卡能够看到每个HP bank中字节组的使用情况及相应接口的特殊功能(DBC,QBC,GC)。

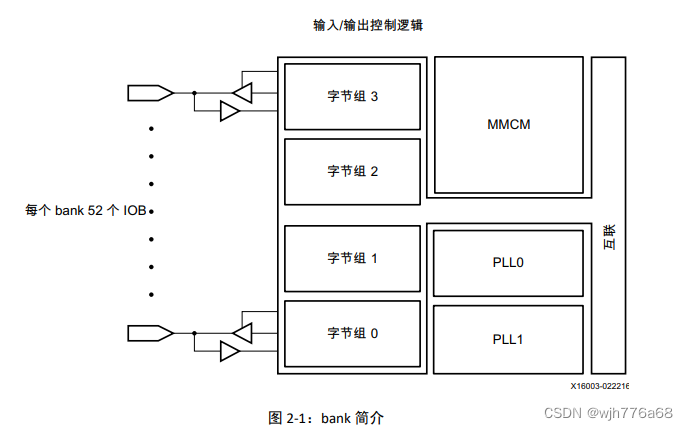

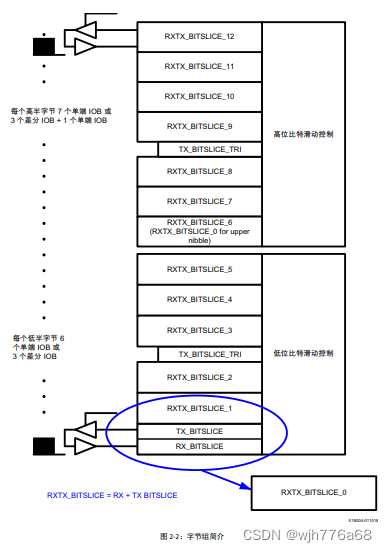

下面两张图展示了一个HP bank的引脚情况,大多数bank均具有52个输入输出引脚,对应52个引脚缓冲(IOB),分为四个字节组(每个字节组具有13个IOB),每个字节组又分为两个半字节组(高半字节组、低半字节组),高半字节组具有7个IOB,低半字节组具有6个IOB。每个半字节的最低2位可作为半字节组数据捕获时钟,在需要时能够对同一半字节组的其他引脚的数据进行采样。此外一些具有特殊功能的引脚也能作为数据捕获时钟使用:DBC引脚,能够作为同一字节组的数据捕获时钟进行采样;QBC引脚,能够作为整个bank的数据捕获时钟进行采样;GC引脚,能够作为bank中MMCM/PLL的输入时钟,进而为用户逻辑提供用户时钟。

HP Bank每个输入输出引脚经过对应的输入输出引脚缓冲后连接到对应的一个TXRX_BITSLICE硬核上,每个半字节组的TXRX_BITSLICE由同一个TX_BITSLICE_TRI和BITSLICE_CONTROL控制,TX_BITSLICE_TRI可视作一个仅向其他TX_BITSLICE三态输出接口输出的特殊TX_BITSLICE,也受BITSLICE_CONTROL的控制。此外每个BITSLICE_CONTROL均具有RIU(寄存器接口单元)接口,能够通过类似ram读写的方式控制BITSLICE_CONTROL中的属性(复位、延时、时钟等),进而间接控制TXRX_BITSLICE。同时,Ultrascale系列提供了RIU_OR硬核能够通过地址划分的方式对位于同一字节组的两个BITSLICE_CONTROL进行统一控制。

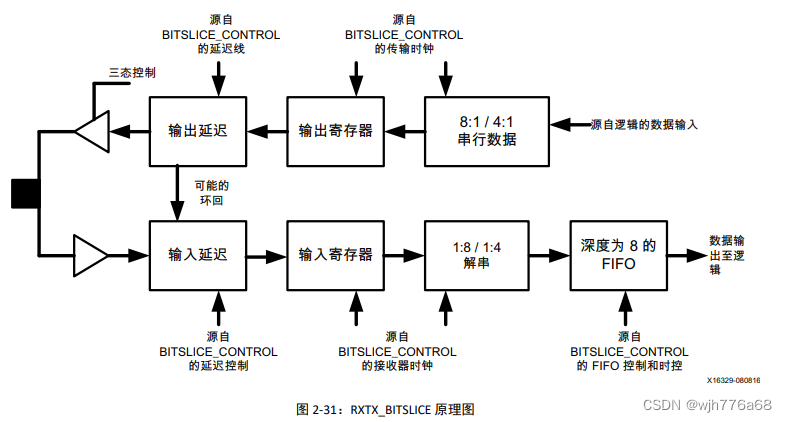

下图展示了RXTX_BITSLICE的逻辑结构,它可分为下半部分的接收逻辑(RX_BITSLICE)和上半部分的发送逻辑(TX_BITSLICE)。在端口只用于接收或发送的单一用途时,TXRX_BITSLICE可进一步替换为RX_BITSLICE或TX_BITSLICE。在这种情况下,RX_BITSLICE可以借用TX_BITSLICE中的延时线从而实现更长时间的延时。

- 使用bitslice需要注意复位顺序,在初始化未完成前功能可能有误。

- MMCM与PLL的输入时钟、反馈时钟和输出时钟存在范围限制需要考虑。PLL的VCO在750-1500MHz

- 多个pll输出时钟相位对齐需要保证输入时钟相同,且不能进行DIV,即CLKOUT_DIV=1

这里举例说明了bitslice的复位过程,同时利用bitslice进行了简单的发送和接收过程,已通过仿真和实现。

- dut_top_tb.v

`timescale 1ns / 1ps

//

// Company:

// Engineer: wjh776a68

//

// Create Date: 01/27/2024 10:38:55 PM

// Design Name:

// Module Name: dut_top_tb

// Project Name:

// Target Devices: xcvu37p

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//module dut_top_tb();wire dm_dbi_n;wire [7:0] dq;wire dqs_t;wire dqs_c;logic clk_n, clk_p;assign clk_n = ~clk_p;initial beginclk_p = 0;forever #5 clk_p = ~clk_p;endinitial beginrepeat(4) @(posedge dqs_t);#100;force dqs_t = 0;force dqs_c = 1;

// #100;#(0.75 / 2);force dqs_t = 1;force dqs_c = 0;force dm_dbi_n = 1;force dq = 8'b00010110;#(0.75 / 2);force dqs_t = 0;force dqs_c = 1;force dm_dbi_n = 0;force dq = 8'b00000000;#(0.75 / 2);force dqs_t = 1;force dqs_c = 0;force dm_dbi_n = 1;force dq = 8'b00010110;#(0.75 / 2);force dqs_t = 0;force dqs_c = 1;force dm_dbi_n = 0;force dq = 8'b00000000;#(0.75 / 2);force dqs_t = 1;force dqs_c = 0;force dm_dbi_n = 1;force dq = 8'b00010110;#(0.75 / 2);force dqs_t = 0;force dqs_c = 1;force dm_dbi_n = 0;force dq = 8'b00000000;#(0.75 / 2);force dqs_t = 1;force dqs_c = 0;force dm_dbi_n = 1;force dq = 8'b00010110;#(0.75 / 2);force dqs_t = 0;force dqs_c = 1;force dm_dbi_n = 0;force dq = 8'b00000000;#(0.75 / 2);force dqs_t = 0;force dqs_c = 1;force dm_dbi_n = 0;force dq = 8'b00000000;#(0.75 / 2);

// force dqs_t = 0;

// force dqs_c = 1;

// #(0.75 / 2);

// #100;release dqs_t;release dqs_c;release dm_dbi_n;release dq;enddut_top dut_top_inst(clk_n,clk_p,dm_dbi_n,dq,dqs_t,dqs_c);

endmodule

- dut_top.v

`timescale 1ns / 1ps

//

// Company:

// Engineer: wjh776a68

//

// Create Date: 01/25/2024 05:20:05 PM

// Design Name:

// Module Name: dut_top

// Project Name:

// Target Devices: xcvu37p

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//module dut_top(input clk_n,input clk_p, // 100MHzinout dm_dbi_n,inout [7:0] dq,inout dqs_t,inout dqs_c

);wire clk_I; // 100MHzwire mmcm_clk_I, mmcm_clk_o_I; // 100MHzwire mmcm_clk_locked;wire pll_clk_I; // 1333.333MHzwire pll_clk_locked;wire pll_clkfbout;reg pll_phyclk_en = 1'b0;wire usr_clk_p, usr_clk_n; // 333.333MHzwire riu_clk_p, riu_clk_n; // 250MHzreg clk_rst = 1;//, mmcm_clk_rst = 1, pll_clk_rst = 1;(* srl_style = "srl_reg" *) reg [31:0] clk_rst_slr32 = {32{1'b1}};(* srl_style = "srl_reg" *) reg [31:0] pll_clk_rst_slr32 = {32{1'b1}};wire mmcm_clk_rst = clk_rst_slr32[31];wire pll_clk_rst = pll_clk_rst_slr32[31];wire itf_rst_done; // byte initialization finishalways @(posedge clk_I) beginclk_rst_slr32 <= {clk_rst_slr32[30:0], clk_rst}; clk_rst <= 1'b0;endalways @(posedge clk_I) beginif (mmcm_clk_locked) begin

// pll_clk_rst <= 1'b0;pll_clk_rst_slr32 <= {pll_clk_rst_slr32[30:0], 1'b0}; end else begin

// pll_clk_rst <= 1'b1;pll_clk_rst_slr32 <= {32{1'b1}};endendIBUFDS IBUFDS_inst (.O(clk_I), // 1-bit output: Buffer output.I(clk_p), // 1-bit input: Diff_p buffer input (connect directly to top-level port).IB(clk_n) // 1-bit input: Diff_n buffer input (connect directly to top-level port)); MMCME4_BASE #(.BANDWIDTH("OPTIMIZED"), // Jitter programming.CLKFBOUT_MULT_F(10.0), // Multiply value for all CLKOUT.CLKFBOUT_PHASE(0.0), // Phase offset in degrees of CLKFB.CLKIN1_PERIOD(10.0), // Input clock period in ns to ps resolution (i.e., 33.333 is 30 MHz)..CLKOUT0_DIVIDE_F(2.0), // Divide amount for CLKOUT0.CLKOUT0_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT0.CLKOUT0_PHASE(0.0), // Phase offset for CLKOUT0.CLKOUT1_DIVIDE(1), // Divide amount for CLKOUT (1-128).CLKOUT1_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT1_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT2_DIVIDE(1), // Divide amount for CLKOUT (1-128).CLKOUT2_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT2_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT3_DIVIDE(1), // Divide amount for CLKOUT (1-128).CLKOUT3_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT3_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT4_CASCADE("FALSE"), // Divide amount for CLKOUT (1-128).CLKOUT4_DIVIDE(1), // Divide amount for CLKOUT (1-128).CLKOUT4_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT4_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT5_DIVIDE(1), // Divide amount for CLKOUT (1-128).CLKOUT5_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT5_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT6_DIVIDE(1), // Divide amount for CLKOUT (1-128).CLKOUT6_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT6_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000)..DIVCLK_DIVIDE(1), // Master division value.IS_CLKFBIN_INVERTED(1'b0), // Optional inversion for CLKFBIN.IS_CLKIN1_INVERTED(1'b0), // Optional inversion for CLKIN1.IS_PWRDWN_INVERTED(1'b0), // Optional inversion for PWRDWN.IS_RST_INVERTED(1'b0), // Optional inversion for RST.REF_JITTER1(0.0), // Reference input jitter in UI (0.000-0.999)..STARTUP_WAIT("FALSE") // Delays DONE until MMCM is locked)MMCME4_BASE_inst ( // 100MHz to 1000MHz(VCO) -> 500MHz.CLKFBOUT(), // 1-bit output: Feedback clock pin to the MMCM.CLKFBOUTB(), // 1-bit output: Inverted CLKFBOUT.CLKOUT0(mmcm_clk_o_I), // 1-bit output: CLKOUT0.CLKOUT0B(), // 1-bit output: Inverted CLKOUT0.CLKOUT1(), // 1-bit output: CLKOUT1.CLKOUT1B(), // 1-bit output: Inverted CLKOUT1.CLKOUT2(), // 1-bit output: CLKOUT2.CLKOUT2B(), // 1-bit output: Inverted CLKOUT2.CLKOUT3(), // 1-bit output: CLKOUT3.CLKOUT3B(), // 1-bit output: Inverted CLKOUT3.CLKOUT4(), // 1-bit output: CLKOUT4.CLKOUT5(), // 1-bit output: CLKOUT5.CLKOUT6(), // 1-bit output: CLKOUT6.LOCKED(mmcm_clk_locked), // 1-bit output: LOCK.CLKFBIN(clk_I), // 1-bit input: Feedback clock pin to the MMCM.CLKIN1(clk_I), // 1-bit input: Primary clock.PWRDWN(1'b0), // 1-bit input: Power-down.RST(mmcm_clk_rst) // 1-bit input: Reset); BUFGCE #(.CE_TYPE("SYNC"), // ASYNC, HARDSYNC, SYNC.IS_CE_INVERTED(1'b0), // Programmable inversion on CE.IS_I_INVERTED(1'b0), // Programmable inversion on I.SIM_DEVICE("ULTRASCALE_PLUS") // ULTRASCALE, ULTRASCALE_PLUS)BUFGCE_inst (.O(mmcm_clk_I), // 1-bit output: Buffer.CE(mmcm_clk_locked), // 1-bit input: Buffer enable.I(mmcm_clk_o_I) // 1-bit input: Buffer);PLLE4_BASE #(.CLKFBOUT_MULT(8), // Multiply value for all CLKOUT.CLKFBOUT_PHASE(0.0), // Phase offset in degrees of CLKFB.CLKIN_PERIOD(2.0), // Input clock period in ns to ps resolution (i.e., 33.333 is 30 MHz)..CLKOUT0_DIVIDE(4), // Divide amount for CLKOUT0.CLKOUT0_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT0.CLKOUT0_PHASE(0.0), // Phase offset for CLKOUT0.CLKOUT1_DIVIDE(8), // Divide amount for CLKOUT1.CLKOUT1_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT1.CLKOUT1_PHASE(0.0), // Phase offset for CLKOUT1.CLKOUTPHY_MODE("VCO_2X"), // Frequency of the CLKOUTPHY.DIVCLK_DIVIDE(3), // Master division value.IS_CLKFBIN_INVERTED(1'b0), // Optional inversion for CLKFBIN.IS_CLKIN_INVERTED(1'b0), // Optional inversion for CLKIN.IS_PWRDWN_INVERTED(1'b0), // Optional inversion for PWRDWN.IS_RST_INVERTED(1'b0), // Optional inversion for RST.REF_JITTER(0.0), // Reference input jitter in UI.STARTUP_WAIT("FALSE") // Delays DONE until PLL is locked)PLLE4_BASE_inst ( // 500MHz to 2666.6MHz (PHY) and 1333.3/4 MHz (usr_clk).CLKFBOUT(pll_clkfbout), // 1-bit output: Feedback clock.CLKOUT0(usr_clk_p), // 1-bit output: General Clock output.CLKOUT0B(usr_clk_n), // 1-bit output: Inverted CLKOUT0.CLKOUT1(riu_clk_p), // 1-bit output: General Clock output 1333.333/8MHz user clock for riu clk(<260MHz).CLKOUT1B(riu_clk_n), // 1-bit output: Inverted CLKOUT1.CLKOUTPHY(pll_clk_I), // 1-bit output: Bitslice clock.LOCKED(pll_clk_locked), // 1-bit output: LOCK.CLKFBIN(pll_clkfbout), // 1-bit input: Feedback clock.CLKIN(mmcm_clk_I), // 1-bit input: Input clock.CLKOUTPHYEN(pll_phyclk_en), // 1-bit input: CLKOUTPHY enable.PWRDWN(1'b0), // 1-bit input: Power-down.RST(pll_clk_rst) // 1-bit input: Reset);(* srl_style = "srl_reg" *) reg [63:0] pll_clk_rst_fin_slr64 = {64{1'b0}};wire pll_clk_rst_fin = pll_clk_rst_fin_slr64[63];always @(posedge mmcm_clk_I) beginif (pll_clk_locked) beginpll_clk_rst_fin_slr64[31:0] <= {pll_clk_rst_fin_slr64[31 - 1 : 0], 1'b1};pll_clk_rst_fin_slr64[63:32] <= {pll_clk_rst_fin_slr64[63 - 1 : 32], pll_clk_rst_fin_slr64[31]};end else beginpll_clk_rst_fin_slr64[31:0] <= {32{1'b0}};pll_clk_rst_fin_slr64[63:32] <= {32{1'b0}};endendlogic delay_rst = 0;logic ctrl_rst = 0;always @(posedge mmcm_clk_I) beginif (pll_clk_rst_fin) beginpll_phyclk_en <= 1'b1;end else beginpll_phyclk_en <= 1'b0;endendalways @(posedge mmcm_clk_I) beginif (pll_clk_locked) begindelay_rst <= 1'b0;ctrl_rst <= 1'b0;end else begindelay_rst <= 1'b1;ctrl_rst <= 1'b1;endendlogic [3:0] lo_TRI_TBYTE_IN = 0;logic [3:0] hi_TRI_TBYTE_IN = 0;reg [3:0] lo_PHY_RDEN = 4'b0000, hi_PHY_RDEN = 4'b0000;logic [7:0] dm_dbi_n_o_I = 0;logic dm_dbi_n_FIFO_EMPTY;logic dm_dbi_n_FIFO_RD_CLK;logic dm_dbi_n_FIFO_RD_EN = 0;logic [7:0] dq_o_I[7:0] = '{0, 0, 0, 0, 0, 0, 0, 0};logic dq_FIFO_EMPTY[7:0];logic dq_FIFO_RD_CLK[7:0];logic dq_FIFO_RD_EN[7:0] = '{0, 0, 0, 0, 0, 0, 0, 0};logic [7:0] dqs_o_I = 0;logic dqs_FIFO_EMPTY;logic dqs_FIFO_RD_CLK;logic dqs_FIFO_RD_EN = 0;logic [7:0] dm_dbi_n_i_I;logic [7:0] dq_i_I[7:0];logic [7:0] dqs_i_I;dut #(.CLK_FREQ(2666.666) // 4 * 333.333 * 2) dut_inst (.pll_clk(pll_clk_I),.riu_clk(riu_clk_p),.delay_rst(delay_rst),.ctrl_rst(ctrl_rst),.itf_rst_done(itf_rst_done),.dm_dbi_n(dm_dbi_n),.dq(dq),.dqs_t(dqs_t),.dqs_c(dqs_c),.lo_TRI_TBYTE_IN(lo_TRI_TBYTE_IN),.hi_TRI_TBYTE_IN(hi_TRI_TBYTE_IN), .lo_PHY_RDEN(lo_PHY_RDEN),.hi_PHY_RDEN(hi_PHY_RDEN),.dm_dbi_n_o_I(dm_dbi_n_o_I),.dm_dbi_n_FIFO_EMPTY(dm_dbi_n_FIFO_EMPTY),.dm_dbi_n_FIFO_RD_CLK(dm_dbi_n_FIFO_RD_CLK),.dm_dbi_n_FIFO_RD_EN(dm_dbi_n_FIFO_RD_EN),.dq_o_I(dq_o_I),.dq_FIFO_EMPTY(dq_FIFO_EMPTY),.dq_FIFO_RD_CLK(dq_FIFO_RD_CLK),.dq_FIFO_RD_EN(dq_FIFO_RD_EN),.dqs_o_I(dqs_o_I),.dqs_FIFO_EMPTY(dqs_FIFO_EMPTY),.dqs_FIFO_RD_CLK(dqs_FIFO_RD_CLK),.dqs_FIFO_RD_EN(dqs_FIFO_RD_EN),.dm_dbi_n_i_I(dm_dbi_n_i_I),.dq_i_I(dq_i_I),.dqs_i_I(dqs_i_I));reg [5:0] cs = 0, ns;reg itf_rst_done_ff = 1'b0, itf_rst_done_ff2 = 1'b0;always @(posedge usr_clk_p) beginitf_rst_done_ff <= itf_rst_done;itf_rst_done_ff2 <= itf_rst_done_ff;if (~itf_rst_done_ff2) begincs <= 0;end else begincs <= ns;endendalways @(*) begincase (cs)0: beginns = 1;end1: beginns = 2;end2: beginns = 3;end3: beginns = 4;end4: beginns = 5;end5: beginns = 6;end6: beginns = 6;end default: beginns = 0;endendcaseendalways @(posedge usr_clk_p) begin // cdccase (ns)0, 1: beginlo_PHY_RDEN <= 4'b0000;hi_PHY_RDEN <= 4'b0000;lo_TRI_TBYTE_IN <= 4'b0000;hi_TRI_TBYTE_IN <= 4'b0000;end2: begindqs_o_I <= 8'b01010101;dq_o_I[0] <= 8'b01010101;dq_o_I[1] <= 8'b01010101;dq_o_I[2] <= 8'b01010101;dq_o_I[3] <= 8'b01010101;dq_o_I[4] <= 8'b01010101;dq_o_I[5] <= 8'b01010101;dq_o_I[6] <= 8'b01010101;dq_o_I[7] <= 8'b01010101;dm_dbi_n_o_I <= 8'b00000000;lo_TRI_TBYTE_IN <= 4'b1111;hi_TRI_TBYTE_IN <= 4'b1111;end3: beginlo_PHY_RDEN <= 4'b1111;hi_PHY_RDEN <= 4'b1111;lo_TRI_TBYTE_IN <= 4'b0000;hi_TRI_TBYTE_IN <= 4'b0000;endendcaseendalways @(*) begindm_dbi_n_FIFO_RD_CLK = usr_clk_p;dqs_FIFO_RD_CLK = usr_clk_p;for (int i = 0; i < 8; i++) begindq_FIFO_RD_CLK[i] = usr_clk_p;endendreg [3:0] rdfifo_cs = 0, rdfifo_ns;always @(posedge usr_clk_p) beginrdfifo_cs <= rdfifo_ns;endalways @(*) begincase (rdfifo_cs)0: beginif (~dq_FIFO_EMPTY[7]) beginrdfifo_ns = 1;end else beginrdfifo_ns = 0;endend1: beginrdfifo_ns = 2;end2: beginrdfifo_ns = 0;enddefault: beginrdfifo_ns = 0;endendcaseend always @(*) beginif (itf_rst_done_ff2) beginfor (int i = 0; i < 8; i++) begindq_FIFO_RD_EN[i] = ~dq_FIFO_EMPTY[7];enddqs_FIFO_RD_EN = ~dq_FIFO_EMPTY[7];dm_dbi_n_FIFO_RD_EN = ~dq_FIFO_EMPTY[7];end else beginfor (int i = 0; i < 8; i++) begindq_FIFO_RD_EN[i] = 0;enddqs_FIFO_RD_EN = 0;dm_dbi_n_FIFO_RD_EN = 0;endendendmodule- dut.v

`timescale 1ns / 1ps

//

// Company:

// Engineer: wjh776a68

//

// Create Date: 01/24/2024 03:36:45 PM

// Design Name:

// Module Name: dut

// Project Name:

// Target Devices: xcvu37p

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//module dut #(parameter CLK_FREQ = 1333.333 // 4 * 333.333

) (input pll_clk,input riu_clk,input delay_rst, // asyncinput ctrl_rst, // asyncoutput reg itf_rst_done, //inout dm_dbi_n,inout [7:0] dq,inout dqs_t,inout dqs_c,input [3:0] lo_TRI_TBYTE_IN, // pll_clk input [3:0] hi_TRI_TBYTE_IN, // pll_clk input [3:0] lo_PHY_RDEN, // pll_clk input [3:0] hi_PHY_RDEN, // pll_clkinput [7:0] dm_dbi_n_o_I,input [7:0] dq_o_I[7:0],input [7:0] dqs_o_I,output [7:0] dm_dbi_n_i_I,output dm_dbi_n_FIFO_EMPTY,input dm_dbi_n_FIFO_RD_CLK,input dm_dbi_n_FIFO_RD_EN,output [7:0] dq_i_I[7:0],output dq_FIFO_EMPTY[7:0],input dq_FIFO_RD_CLK[7:0],input dq_FIFO_RD_EN[7:0],output [7:0] dqs_i_I,output dqs_FIFO_EMPTY,input dqs_FIFO_RD_CLK,input dqs_FIFO_RD_EN

);// wire riu_clk = usr_clk;wire hi_DLY_RDY, lo_DLY_RDY, hi_VTC_RDY, lo_VTC_RDY;reg lo_TBYTE_IN, hi_TBYTE_IN;reg EN_VTC = 1'b0;wire hi_clkout_n, hi_clkout_p, lo_clkout_n, lo_clkout_p;wire [39:0] hi_TRI_BIT_CTRL_OUT, hi_TRI_BIT_CTRL_IN, lo_TRI_BIT_CTRL_OUT, lo_TRI_BIT_CTRL_IN;wire [39:0] dm_dbi_n_TRI_BIT_CTRL_OUT;wire [39:0] dm_dbi_n_TRI_BIT_CTRL_IN;wire [39:0] dm_dbi_n_RX_BIT_CTRL_OUT;wire [39:0] dm_dbi_n_TX_BIT_CTRL_OUT;wire [39:0] dm_dbi_n_RX_BIT_CTRL_IN;wire [39:0] dm_dbi_n_TX_BIT_CTRL_IN;// logic dm_dbi_n_TBYTE_IN;wire [39:0] dq_TRI_BIT_CTRL_OUT[7:0];wire [39:0] dq_TRI_BIT_CTRL_IN[7:0];wire [39:0] dq_RX_BIT_CTRL_OUT[7:0];wire [39:0] dq_TX_BIT_CTRL_OUT[7:0];wire [39:0] dq_RX_BIT_CTRL_IN[7:0];wire [39:0] dq_TX_BIT_CTRL_IN[7:0];// logic dq_TBYTE_IN[7:0];wire [39:0] dqs_TRI_BIT_CTRL_OUT;wire [39:0] dqs_TRI_BIT_CTRL_IN;wire [39:0] dqs_RX_BIT_CTRL_OUT;wire [39:0] dqs_TX_BIT_CTRL_OUT;wire [39:0] dqs_RX_BIT_CTRL_IN;wire [39:0] dqs_TX_BIT_CTRL_IN;// logic dqs_TBYTE_IN;(* ASYNC_REG="true" *) reg hi_DLY_RDY_ff = 1'b0, hi_DLY_RDY_ff2 = 1'b0, lo_DLY_RDY_ff = 1'b0, lo_DLY_RDY_ff2 = 1'b0;reg DLY_RDY_COMB = 1'b0;always @(posedge riu_clk) beginhi_DLY_RDY_ff2 <= hi_DLY_RDY_ff;hi_DLY_RDY_ff <= hi_DLY_RDY; lo_DLY_RDY_ff2 <= lo_DLY_RDY_ff;lo_DLY_RDY_ff <= lo_DLY_RDY;DLY_RDY_COMB <= hi_DLY_RDY_ff2 & lo_DLY_RDY_ff2;if (DLY_RDY_COMB) beginEN_VTC <= 1'b1;end else beginEN_VTC <= 1'b0;endend(* ASYNC_REG="true" *) reg hi_VTC_RDY_ff = 1'b0, hi_VTC_RDY_ff2 = 1'b0, lo_VTC_RDY_ff = 1'b0, lo_VTC_RDY_ff2 = 1'b0;reg VTC_RDY_COMB = 1'b0;always @(posedge riu_clk) beginhi_VTC_RDY_ff2 <= hi_VTC_RDY_ff;hi_VTC_RDY_ff <= hi_VTC_RDY; lo_VTC_RDY_ff2 <= lo_VTC_RDY_ff;lo_VTC_RDY_ff <= lo_VTC_RDY;VTC_RDY_COMB <= hi_VTC_RDY_ff2 & lo_VTC_RDY_ff2;if (VTC_RDY_COMB) beginitf_rst_done <= 1'b1;end else beginitf_rst_done <= 1'b0;endenddq #(.CLK_FREQ(CLK_FREQ)) dm_dbi_n_inst(.dq(dm_dbi_n),// .TRI_BIT_CTRL_OUT(dm_dbi_n_TRI_BIT_CTRL_OUT),// .TRI_BIT_CTRL_IN(dm_dbi_n_TRI_BIT_CTRL_IN),.RX_BIT_CTRL_OUT(dm_dbi_n_RX_BIT_CTRL_OUT), .TX_BIT_CTRL_OUT(dm_dbi_n_TX_BIT_CTRL_OUT), .RX_BIT_CTRL_IN(dm_dbi_n_RX_BIT_CTRL_IN),.TX_BIT_CTRL_IN(dm_dbi_n_TX_BIT_CTRL_IN), .Q(dm_dbi_n_i_I), .D(dm_dbi_n_o_I), .FIFO_EMPTY(dm_dbi_n_FIFO_EMPTY), .FIFO_RD_CLK(dm_dbi_n_FIFO_RD_CLK), .FIFO_RD_EN(dm_dbi_n_FIFO_RD_EN), .TBYTE_IN(lo_TBYTE_IN),// .TRI_TBYTE_IN(dm_dbi_n_TRI_TBYTE_IN).rst(delay_rst));generate for (genvar i = 0; i < 8; i++) beginif (i < 4) begin: lo_halfbytedq #(.CLK_FREQ(CLK_FREQ)) dq_lo_halfbyte_inst(.dq(dq[i]),// .TRI_BIT_CTRL_OUT(dq_TRI_BIT_CTRL_OUT[i]),// .TRI_BIT_CTRL_IN(dq_TRI_BIT_CTRL_IN[i]),.RX_BIT_CTRL_OUT(dq_RX_BIT_CTRL_OUT[i]), .TX_BIT_CTRL_OUT(dq_TX_BIT_CTRL_OUT[i]), .RX_BIT_CTRL_IN(dq_RX_BIT_CTRL_IN[i]),.TX_BIT_CTRL_IN(dq_TX_BIT_CTRL_IN[i]), .Q(dq_i_I[i]), .D(dq_o_I[i]), .FIFO_EMPTY(dq_FIFO_EMPTY[i]), .FIFO_RD_CLK(dq_FIFO_RD_CLK[i]), .FIFO_RD_EN(dq_FIFO_RD_EN[i]), .TBYTE_IN(lo_TBYTE_IN),// .TRI_TBYTE_IN(dq_TRI_TBYTE_IN[i]).rst(delay_rst));end else begin: hi_halfbytedq #(.CLK_FREQ(CLK_FREQ)) hi_halfbyte_inst(.dq(dq[i]),// .TRI_BIT_CTRL_OUT(dq_TRI_BIT_CTRL_OUT[i]),// .TRI_BIT_CTRL_IN(dq_TRI_BIT_CTRL_IN[i]),.RX_BIT_CTRL_OUT(dq_RX_BIT_CTRL_OUT[i]), .TX_BIT_CTRL_OUT(dq_TX_BIT_CTRL_OUT[i]), .RX_BIT_CTRL_IN(dq_RX_BIT_CTRL_IN[i]),.TX_BIT_CTRL_IN(dq_TX_BIT_CTRL_IN[i]), .Q(dq_i_I[i]), .D(dq_o_I[i]), .FIFO_EMPTY(dq_FIFO_EMPTY[i]), .FIFO_RD_CLK(dq_FIFO_RD_CLK[i]), .FIFO_RD_EN(dq_FIFO_RD_EN[i]), .TBYTE_IN(hi_TBYTE_IN),// .TRI_TBYTE_IN(dq_TRI_TBYTE_IN[i]).rst(delay_rst));endend endgeneratedqs #(.CLK_FREQ(CLK_FREQ)) dqs_inst(.dqs_t(dqs_t),.dqs_c(dqs_c),// .TRI_BIT_CTRL_OUT(dqs_TRI_BIT_CTRL_OUT),// .TRI_BIT_CTRL_IN(dqs_TRI_BIT_CTRL_IN),.RX_BIT_CTRL_OUT(dqs_RX_BIT_CTRL_OUT), .TX_BIT_CTRL_OUT(dqs_TX_BIT_CTRL_OUT), .RX_BIT_CTRL_IN(dqs_RX_BIT_CTRL_IN),.TX_BIT_CTRL_IN(dqs_TX_BIT_CTRL_IN), .Q(dqs_i_I), .D(dqs_o_I), .FIFO_EMPTY(dqs_FIFO_EMPTY), .FIFO_RD_CLK(dqs_FIFO_RD_CLK), .FIFO_RD_EN(dqs_FIFO_RD_EN), .TBYTE_IN(hi_TBYTE_IN),// .TRI_TBYTE_IN(dqs_TRI_TBYTE_IN).rst(delay_rst));generate // tri_logicTX_BITSLICE_TRI #(.DATA_WIDTH(8), // Parallel data input width (4-8).DELAY_FORMAT("TIME"), // Units of the DELAY_VALUE (COUNT, TIME).DELAY_TYPE("FIXED"), // Set the type of tap delay line (FIXED, VARIABLE, VAR_LOAD).DELAY_VALUE(0), // Output delay value setting.INIT(1'b1), // Defines initial O value.IS_CLK_INVERTED(1'b0), // Optional inversion for CLK.IS_RST_DLY_INVERTED(1'b0), // Optional inversion for RST_DLY.IS_RST_INVERTED(1'b0), // Optional inversion for RST.OUTPUT_PHASE_90("FALSE"), // Delays the output phase by 90-degrees.REFCLK_FREQUENCY(CLK_FREQ), // Specification of the reference clock frequency in MHz (200.0-2667.0).SIM_DEVICE("ULTRASCALE_PLUS"), // Set the device version (ULTRASCALE, ULTRASCALE_PLUS, ULTRASCALE_PLUS_ES1,// ULTRASCALE_PLUS_ES2).UPDATE_MODE("ASYNC") // Determines when updates to the delay will take effect (ASYNC, MANUAL,// SYNC))TX_BITSLICE_TRI_hi_halfbyte_inst (.BIT_CTRL_OUT(hi_TRI_BIT_CTRL_OUT), // 40-bit output: Output bus to BITSLICE_CONTROL.CNTVALUEOUT(), // 9-bit output: Counter value to device logic.TRI_OUT(hi_TBYTE_IN), // 1-bit output: Output to the TBYTE_IN pins of the bitslices.BIT_CTRL_IN(hi_TRI_BIT_CTRL_IN), // 40-bit input: Input bus from BITSLICE_CONTROL.CE(1'b0), // 1-bit input: Active high enable increment/decrement input.CLK(1'b1), // 1-bit input: Clock input.CNTVALUEIN(9'b0), // 9-bit input: Counter value input.EN_VTC(1'b1), // 1-bit input: Enable to keep stable delay over VT.INC(1'b0), // 1-bit input: Increment the current delay tap setting.LOAD(1'b0), // 1-bit input: Load the CNTVALUEIN tap setting.RST(delay_rst), // 1-bit input: Asynchronous assert, synchronous deassert.RST_DLY(delay_rst) // 1-bit input: Reset the internal DELAY value to DELAY_VALUE);TX_BITSLICE_TRI #(.DATA_WIDTH(8), // Parallel data input width (4-8).DELAY_FORMAT("TIME"), // Units of the DELAY_VALUE (COUNT, TIME).DELAY_TYPE("FIXED"), // Set the type of tap delay line (FIXED, VARIABLE, VAR_LOAD).DELAY_VALUE(0), // Output delay value setting.INIT(1'b1), // Defines initial O value.IS_CLK_INVERTED(1'b0), // Optional inversion for CLK.IS_RST_DLY_INVERTED(1'b0), // Optional inversion for RST_DLY.IS_RST_INVERTED(1'b0), // Optional inversion for RST.OUTPUT_PHASE_90("FALSE"), // Delays the output phase by 90-degrees.REFCLK_FREQUENCY(CLK_FREQ), // Specification of the reference clock frequency in MHz (200.0-2667.0).SIM_DEVICE("ULTRASCALE_PLUS"), // Set the device version (ULTRASCALE, ULTRASCALE_PLUS, ULTRASCALE_PLUS_ES1,// ULTRASCALE_PLUS_ES2).UPDATE_MODE("ASYNC") // Determines when updates to the delay will take effect (ASYNC, MANUAL,// SYNC))TX_BITSLICE_TRI_lo_halfbyte_inst (.BIT_CTRL_OUT(lo_TRI_BIT_CTRL_OUT), // 40-bit output: Output bus to BITSLICE_CONTROL.CNTVALUEOUT(), // 9-bit output: Counter value to device logic.TRI_OUT(lo_TBYTE_IN), // 1-bit output: Output to the TBYTE_IN pins of the bitslices.BIT_CTRL_IN(lo_TRI_BIT_CTRL_IN), // 40-bit input: Input bus from BITSLICE_CONTROL.CE(1'b0), // 1-bit input: Active high enable increment/decrement input.CLK(1'b1), // 1-bit input: Clock input.CNTVALUEIN(9'b0), // 9-bit input: Counter value input.EN_VTC(1'b1), // 1-bit input: Enable to keep stable delay over VT.INC(1'b0), // 1-bit input: Increment the current delay tap setting.LOAD(1'b0), // 1-bit input: Load the CNTVALUEIN tap setting.RST(delay_rst), // 1-bit input: Asynchronous assert, synchronous deassert.RST_DLY(delay_rst) // 1-bit input: Reset the internal DELAY value to DELAY_VALUE);endgenerateBITSLICE_CONTROL #(.DIV_MODE("DIV4"), // Controller DIV2/DIV4 mode (DIV2, DIV4).EN_CLK_TO_EXT_NORTH("DISABLE"), // Enable clock forwarding to north.EN_CLK_TO_EXT_SOUTH("DISABLE"), // Enable clock forwarding to south.EN_DYN_ODLY_MODE("FALSE"), // Enable dynamic output delay mode.EN_OTHER_NCLK("FALSE"), // Select the NCLK from the other BITSLICE_CONTROL in the nibble (FALSE, TRUE).EN_OTHER_PCLK("FALSE"), // Select the PCLK from the other BITSLICE_CONTROL in the nibble (FALSE, TRUE).IDLY_VT_TRACK("TRUE"), // Enable VT tracking for input delays.INV_RXCLK("FALSE"), // Invert clock path from IOB to upper RX bitslice.ODLY_VT_TRACK("TRUE"), // Enable VT tracking for output delays.QDLY_VT_TRACK("TRUE"), // Enable VT tracking for clock delays.READ_IDLE_COUNT(6'h00), // Gap count between read bursts for ODT control counter (0-3f).REFCLK_SRC("PLLCLK"), // Select the input clock for delay control (PLLCLK, REFCLK). REFCLK is only supported for RX_BITSLICE..ROUNDING_FACTOR(16), // Rounding factor in BISC spec (128-8).RXGATE_EXTEND("FALSE"), // Reserved for use by Memory IP. Do Not Change..RX_CLK_PHASE_N("SHIFT_0"), // Shift the Read CLK relative to read DQ during calibration (SHIFT_0, SHIFT_90).RX_CLK_PHASE_P("SHIFT_0"), // Shift the Read CLK relative to read DQ during calibration (SHIFT_0, SHIFT_90).RX_GATING("ENABLE"), // ENABLE/DISABLE read DQS gating.SELF_CALIBRATE("ENABLE"), // Enable BISC of nibble controlled by BITSLICE_CONTROL.SERIAL_MODE("FALSE"), // Put BITSLICE read paths into serial mode (FALSE, TRUE).SIM_DEVICE("ULTRASCALE_PLUS"), // Set the device version (ULTRASCALE, ULTRASCALE_PLUS, ULTRASCALE_PLUS_ES1, ULTRASCALE_PLUS_ES2).TX_GATING("ENABLE") // ENABLE/DISABLE clock gating in WClkgen)BITSLICE_CONTROL_hi_halfbyte_inst (.CLK_TO_EXT_NORTH(), // 1-bit output: Inter-byte clock going to north// BITSLICE_CONTROL.CLK_TO_EXT_SOUTH(), // 1-bit output: Inter-byte clock going to south// BITSLICE_CONTROL.DLY_RDY(hi_DLY_RDY), // 1-bit output: Fixed delay calibration complete.DYN_DCI(), // 7-bit output: Direct control of IOB DCI when using a memory interface .NCLK_NIBBLE_OUT(hi_clkout_n), // 1-bit output: Intra-byte DQS strobes/clock to other control block.PCLK_NIBBLE_OUT(hi_clkout_p), // 1-bit output: Intra-byte DQS strobes/clock to other control block.RIU_RD_DATA(), // 16-bit output: RIU Output Read data to the controller.RIU_VALID(), // 1-bit output: Last data written has been accepted when High.RX_BIT_CTRL_OUT0(dqs_RX_BIT_CTRL_IN), // 40-bit output: Output bus to Bitslice 0.RX_BIT_CTRL_OUT1(), // 40-bit output: Output bus to Bitslice 1.RX_BIT_CTRL_OUT2(dq_RX_BIT_CTRL_IN[4]), // 40-bit output: Output bus to Bitslice 2.RX_BIT_CTRL_OUT3(dq_RX_BIT_CTRL_IN[5]), // 40-bit output: Output bus to Bitslice 3.RX_BIT_CTRL_OUT4(dq_RX_BIT_CTRL_IN[6]), // 40-bit output: Output bus to Bitslice 4.RX_BIT_CTRL_OUT5(dq_RX_BIT_CTRL_IN[7]), // 40-bit output: Output bus to Bitslice 5.RX_BIT_CTRL_OUT6(), // 40-bit output: Output bus to Bitslice 6.TX_BIT_CTRL_OUT0(dqs_TX_BIT_CTRL_IN), // 40-bit output: Output bus to Bitslice 0.TX_BIT_CTRL_OUT1(), // 40-bit output: Output bus to Bitslice 1.TX_BIT_CTRL_OUT2(dq_TX_BIT_CTRL_IN[4]), // 40-bit output: Output bus to Bitslice 2.TX_BIT_CTRL_OUT3(dq_TX_BIT_CTRL_IN[5]), // 40-bit output: Output bus to Bitslice 3.TX_BIT_CTRL_OUT4(dq_TX_BIT_CTRL_IN[6]), // 40-bit output: Output bus to Bitslice 4.TX_BIT_CTRL_OUT5(dq_TX_BIT_CTRL_IN[7]), // 40-bit output: Output bus to Bitslice 5.TX_BIT_CTRL_OUT6(), // 40-bit output: Output bus to Bitslice 6.TX_BIT_CTRL_OUT_TRI(hi_TRI_BIT_CTRL_IN), // 40-bit output: Output bus to 3-state TX_BITSLICE_TRI.VTC_RDY(hi_VTC_RDY), // 1-bit output: PHY calibration is complete.CLK_FROM_EXT(1'b0), // 1-bit input: Inter-byte clock coming from north or south BITSLICE_CONTROL.EN_VTC(EN_VTC), // 1-bit input: Enables voltage and temperature compensation when High.NCLK_NIBBLE_IN(lo_clkout_n), // 1-bit input: Intra-byte DQS strobes from other/clock control block.PCLK_NIBBLE_IN(lo_clkout_p), // 1-bit input: Intra-byte DQS strobes/clock from other control block.PHY_RDCS0(4'b0), // 4-bit input: Rank select.PHY_RDCS1(4'b0), // 4-bit input: Rank select.PHY_RDEN(hi_PHY_RDEN), // 4-bit input: Read burst enable when using a memory interface.PHY_WRCS0(4'b0), // 4-bit input: Rank select.PHY_WRCS1(4'b0), // 4-bit input: Rank select.PLL_CLK(pll_clk), // 1-bit input: PLL clock input.REFCLK(1'b0), // 1-bit input: Frequency reference clock for delay control.RIU_ADDR(6'b0), // 6-bit input: Address input for RIU.RIU_CLK(riu_clk), // 1-bit input: System clock from fabric for RIU access.RIU_NIBBLE_SEL(1'b0), // 1-bit input: Nibble select to enable RIU read/write.RIU_WR_DATA(16'b0), // 16-bit input: RIU Input Write data from the controller.RIU_WR_EN(1'b0), // 1-bit input: Enables write to RIU when High.RST(ctrl_rst), // 1-bit input: Asynchronous global reset.RX_BIT_CTRL_IN0(dqs_RX_BIT_CTRL_OUT), // 40-bit input: Input bus from Bitslice 0.RX_BIT_CTRL_IN1(40'b0), // 40-bit input: Input bus from Bitslice 1.RX_BIT_CTRL_IN2(dq_RX_BIT_CTRL_OUT[4]), // 40-bit input: Input bus from Bitslice 2.RX_BIT_CTRL_IN3(dq_RX_BIT_CTRL_OUT[5]), // 40-bit input: Input bus from Bitslice 3.RX_BIT_CTRL_IN4(dq_RX_BIT_CTRL_OUT[6]), // 40-bit input: Input bus from Bitslice 4.RX_BIT_CTRL_IN5(dq_RX_BIT_CTRL_OUT[7]), // 40-bit input: Input bus from Bitslice 5.RX_BIT_CTRL_IN6(40'b0), // 40-bit input: Input bus from Bitslice 6.TBYTE_IN(hi_TRI_TBYTE_IN), // 4-bit input: Output enable for 3-state control.TX_BIT_CTRL_IN0(dqs_TX_BIT_CTRL_OUT), // 40-bit input: Input bus from Bitslice 0.TX_BIT_CTRL_IN1(40'b0), // 40-bit input: Input bus from Bitslice 1.TX_BIT_CTRL_IN2(dq_TX_BIT_CTRL_OUT[4]), // 40-bit input: Input bus from Bitslice 2.TX_BIT_CTRL_IN3(dq_TX_BIT_CTRL_OUT[5]), // 40-bit input: Input bus from Bitslice 3.TX_BIT_CTRL_IN4(dq_TX_BIT_CTRL_OUT[6]), // 40-bit input: Input bus from Bitslice 4.TX_BIT_CTRL_IN5(dq_TX_BIT_CTRL_OUT[7]), // 40-bit input: Input bus from Bitslice 5.TX_BIT_CTRL_IN6(40'b0), // 40-bit input: Input bus from Bitslice 6.TX_BIT_CTRL_IN_TRI(hi_TRI_BIT_CTRL_OUT) // 40-bit input: Input bus from 3-state TX_BITSLICE_TRI);BITSLICE_CONTROL #(.DIV_MODE("DIV4"), // Controller DIV2/DIV4 mode (DIV2, DIV4).EN_CLK_TO_EXT_NORTH("DISABLE"), // Enable clock forwarding to north.EN_CLK_TO_EXT_SOUTH("DISABLE"), // Enable clock forwarding to south.EN_DYN_ODLY_MODE("FALSE"), // Enable dynamic output delay mode.EN_OTHER_NCLK("TRUE"), // Select the NCLK from the other BITSLICE_CONTROL in the nibble (FALSE, TRUE).EN_OTHER_PCLK("TRUE"), // Select the PCLK from the other BITSLICE_CONTROL in the nibble (FALSE, TRUE).IDLY_VT_TRACK("TRUE"), // Enable VT tracking for input delays.INV_RXCLK("FALSE"), // Invert clock path from IOB to upper RX bitslice.ODLY_VT_TRACK("TRUE"), // Enable VT tracking for output delays.QDLY_VT_TRACK("TRUE"), // Enable VT tracking for clock delays.READ_IDLE_COUNT(6'h00), // Gap count between read bursts for ODT control counter (0-3f).REFCLK_SRC("PLLCLK"), // Select the input clock for delay control (PLLCLK, REFCLK). REFCLK is only supported for RX_BITSLICE..ROUNDING_FACTOR(16), // Rounding factor in BISC spec (128-8).RXGATE_EXTEND("FALSE"), // Reserved for use by Memory IP. Do Not Change..RX_CLK_PHASE_N("SHIFT_0"), // Shift the Read CLK relative to read DQ during calibration (SHIFT_0, SHIFT_90).RX_CLK_PHASE_P("SHIFT_0"), // Shift the Read CLK relative to read DQ during calibration (SHIFT_0, SHIFT_90).RX_GATING("ENABLE"), // ENABLE/DISABLE read DQS gating.SELF_CALIBRATE("ENABLE"), // Enable BISC of nibble controlled by BITSLICE_CONTROL.SERIAL_MODE("FALSE"), // Put BITSLICE read paths into serial mode (FALSE, TRUE).SIM_DEVICE("ULTRASCALE_PLUS"), // Set the device version (ULTRASCALE, ULTRASCALE_PLUS, ULTRASCALE_PLUS_ES1, ULTRASCALE_PLUS_ES2).TX_GATING("ENABLE") // ENABLE/DISABLE clock gating in WClkgen)BITSLICE_CONTROL_lo_halfbyte_inst (.CLK_TO_EXT_NORTH(), // 1-bit output: Inter-byte clock going to north// BITSLICE_CONTROL.CLK_TO_EXT_SOUTH(), // 1-bit output: Inter-byte clock going to south// BITSLICE_CONTROL.DLY_RDY(lo_DLY_RDY), // 1-bit output: Fixed delay calibration complete.DYN_DCI(), // 7-bit output: Direct control of IOB DCI when using a memory interface .NCLK_NIBBLE_OUT(lo_clkout_n), // 1-bit output: Intra-byte DQS strobes/clock to other control block.PCLK_NIBBLE_OUT(lo_clkout_p), // 1-bit output: Intra-byte DQS strobes/clock to other control block.RIU_RD_DATA(), // 16-bit output: RIU Output Read data to the controller.RIU_VALID(), // 1-bit output: Last data written has been accepted when High.RX_BIT_CTRL_OUT0(dm_dbi_n_RX_BIT_CTRL_IN), // 40-bit output: Output bus to Bitslice 0.RX_BIT_CTRL_OUT1(), // 40-bit output: Output bus to Bitslice 1.RX_BIT_CTRL_OUT2(dq_RX_BIT_CTRL_IN[0]), // 40-bit output: Output bus to Bitslice 2.RX_BIT_CTRL_OUT3(dq_RX_BIT_CTRL_IN[1]), // 40-bit output: Output bus to Bitslice 3.RX_BIT_CTRL_OUT4(dq_RX_BIT_CTRL_IN[2]), // 40-bit output: Output bus to Bitslice 4.RX_BIT_CTRL_OUT5(dq_RX_BIT_CTRL_IN[3]), // 40-bit output: Output bus to Bitslice 5.RX_BIT_CTRL_OUT6(), // 40-bit output: Output bus to Bitslice 6.TX_BIT_CTRL_OUT0(dm_dbi_n_TX_BIT_CTRL_IN), // 40-bit output: Output bus to Bitslice 0.TX_BIT_CTRL_OUT1(), // 40-bit output: Output bus to Bitslice 1.TX_BIT_CTRL_OUT2(dq_TX_BIT_CTRL_IN[0]), // 40-bit output: Output bus to Bitslice 2.TX_BIT_CTRL_OUT3(dq_TX_BIT_CTRL_IN[1]), // 40-bit output: Output bus to Bitslice 3.TX_BIT_CTRL_OUT4(dq_TX_BIT_CTRL_IN[2]), // 40-bit output: Output bus to Bitslice 4.TX_BIT_CTRL_OUT5(dq_TX_BIT_CTRL_IN[3]), // 40-bit output: Output bus to Bitslice 5.TX_BIT_CTRL_OUT6(), // 40-bit output: Output bus to Bitslice 6.TX_BIT_CTRL_OUT_TRI(lo_TRI_BIT_CTRL_IN), // 40-bit output: Output bus to 3-state TX_BITSLICE_TRI.VTC_RDY(lo_VTC_RDY), // 1-bit output: PHY calibration is complete.CLK_FROM_EXT(1'b1), // 1-bit input: Inter-byte clock coming from north or south BITSLICE_CONTROL.EN_VTC(EN_VTC), // 1-bit input: Enables voltage and temperature compensation when High.NCLK_NIBBLE_IN(hi_clkout_n), // 1-bit input: Intra-byte DQS strobes from other/clock control block.PCLK_NIBBLE_IN(hi_clkout_p), // 1-bit input: Intra-byte DQS strobes/clock from other control block.PHY_RDCS0(4'b0), // 4-bit input: Rank select.PHY_RDCS1(4'b0), // 4-bit input: Rank select.PHY_RDEN(lo_PHY_RDEN), // 4-bit input: Read burst enable when using a memory interface.PHY_WRCS0(4'b0), // 4-bit input: Rank select.PHY_WRCS1(4'b0), // 4-bit input: Rank select.PLL_CLK(pll_clk), // 1-bit input: PLL clock input.REFCLK(1'b0), // 1-bit input: Frequency reference clock for delay control.RIU_ADDR(6'b0), // 6-bit input: Address input for RIU.RIU_CLK(riu_clk), // 1-bit input: System clock from fabric for RIU access.RIU_NIBBLE_SEL(1'b0), // 1-bit input: Nibble select to enable RIU read/write.RIU_WR_DATA(16'b0), // 16-bit input: RIU Input Write data from the controller.RIU_WR_EN(1'b0), // 1-bit input: Enables write to RIU when High.RST(ctrl_rst), // 1-bit input: Asynchronous global reset.RX_BIT_CTRL_IN0(dm_dbi_n_RX_BIT_CTRL_OUT), // 40-bit input: Input bus from Bitslice 0.RX_BIT_CTRL_IN1(40'b0), // 40-bit input: Input bus from Bitslice 1.RX_BIT_CTRL_IN2(dq_RX_BIT_CTRL_OUT[0]), // 40-bit input: Input bus from Bitslice 2.RX_BIT_CTRL_IN3(dq_RX_BIT_CTRL_OUT[1]), // 40-bit input: Input bus from Bitslice 3.RX_BIT_CTRL_IN4(dq_RX_BIT_CTRL_OUT[2]), // 40-bit input: Input bus from Bitslice 4.RX_BIT_CTRL_IN5(dq_RX_BIT_CTRL_OUT[3]), // 40-bit input: Input bus from Bitslice 5.RX_BIT_CTRL_IN6(40'b0), // 40-bit input: Input bus from Bitslice 6.TBYTE_IN(lo_TRI_TBYTE_IN), // 4-bit input: Output enable for 3-state control.TX_BIT_CTRL_IN0(dm_dbi_n_TX_BIT_CTRL_OUT), // 40-bit input: Input bus from Bitslice 0.TX_BIT_CTRL_IN1(40'b0), // 40-bit input: Input bus from Bitslice 1.TX_BIT_CTRL_IN2(dq_TX_BIT_CTRL_OUT[0]), // 40-bit input: Input bus from Bitslice 2.TX_BIT_CTRL_IN3(dq_TX_BIT_CTRL_OUT[1]), // 40-bit input: Input bus from Bitslice 3.TX_BIT_CTRL_IN4(dq_TX_BIT_CTRL_OUT[2]), // 40-bit input: Input bus from Bitslice 4.TX_BIT_CTRL_IN5(dq_TX_BIT_CTRL_OUT[3]), // 40-bit input: Input bus from Bitslice 5.TX_BIT_CTRL_IN6(40'b0), // 40-bit input: Input bus from Bitslice 6.TX_BIT_CTRL_IN_TRI(lo_TRI_BIT_CTRL_OUT) // 40-bit input: Input bus from 3-state TX_BITSLICE_TRI);

endmodule

- dq.v

`timescale 1ns / 1ps

//

// Company:

// Engineer: wjh776a68

//

// Create Date: 01/29/2024 05:58:32 PM

// Design Name:

// Module Name: dq

// Project Name:

// Target Devices: xcvu37p

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//module dq #(parameter CLK_FREQ = 1333.333

) (inout dq,// output [39:0] TRI_BIT_CTRL_OUT,// input [39:0] TRI_BIT_CTRL_IN,output [39:0] RX_BIT_CTRL_OUT, // outputoutput [39:0] TX_BIT_CTRL_OUT, // outputoutput [7:0] Q, // outputinput [7:0] D, // input -- assoutput FIFO_EMPTY, // outputinput FIFO_RD_CLK, // input -- assinput FIFO_RD_EN, // input -- assinput [39:0] RX_BIT_CTRL_IN, // inputinput [39:0] TX_BIT_CTRL_IN, // inputinput TBYTE_IN, // input// input [3:0] TRI_TBYTE_INinput rst

);logic [8:0] TX_CNTVALUEOUT; // output // internallogic [8:0] RX_CNTVALUEOUT; // output // internallogic O; // output -- ass // internallogic T_OUT; // output -- ass // internallogic DATAIN; // input -- ass // internallogic FIFO_WRCLK_OUT; // output // internallogic T = 1'b0; // inputlogic TX_CE = 1'b0; // input -- asslogic TX_CLK = 1'b1; // input -- asslogic RX_CE = 1'b0; // input -- asslogic RX_CLK = 1'b1; // input -- asslogic [8:0] RX_CNTVALUEIN = 9'b0; // input -- asslogic RX_EN_VTC = 1'b1; // input -- asslogic RX_INC = 1'b0; // input -- asslogic RX_LOAD = 1'b0; // input -- asswire RX_RST = rst; // input -- asswire RX_RST_DLY = rst; // input -- asslogic [8:0] TX_CNTVALUEIN = 9'b0; // input -- asslogic TX_EN_VTC = 1'b1; // input -- asslogic TX_INC = 1'b0; // input -- asslogic TX_LOAD = 1'b0; // input -- asswire TX_RST = rst; // input -- asswire TX_RST_DLY = rst; // input -- assRXTX_BITSLICE #(.ENABLE_PRE_EMPHASIS("FALSE"), // Enable the pre-emphasis.FIFO_SYNC_MODE("FALSE"), // Internal write clock and FIFO_RD_CLK are coming from a common source.INIT(1'b1), // Defines initial O value.IS_RX_CLK_INVERTED(1'b0), // Optional inversion for RX_CLK.IS_RX_RST_DLY_INVERTED(1'b0), // Optional inversion for RX_RST_DLY.IS_RX_RST_INVERTED(1'b0), // Optional inversion for RX_RST.IS_TX_CLK_INVERTED(1'b0), // Optional inversion for TX_CLK.IS_TX_RST_DLY_INVERTED(1'b0), // Optional inversion for TX_RST_DLY.IS_TX_RST_INVERTED(1'b0), // Optional inversion for TX_RST.RX_DATA_TYPE("DATA"), // Defines what the RX input pin is carrying (CLOCK, DATA, DATA_AND_CLOCK,// SERIAL).RX_DATA_WIDTH(8), // Defines the width of the serial-to-parallel converter (4-8).RX_DELAY_FORMAT("TIME"), // Units of the RX DELAY_VALUE (COUNT, TIME).RX_DELAY_TYPE("FIXED"), // Set the type of RX tap delay line (FIXED, VARIABLE, VAR_LOAD).RX_DELAY_VALUE(0), // RX Input delay value setting in ps.RX_REFCLK_FREQUENCY(CLK_FREQ), // Specification of the RX reference clock frequency in MHz (200.0-2667.0).RX_UPDATE_MODE("ASYNC"), // Determines when updates to the RX delay will take effect (ASYNC,// MANUAL, SYNC).SIM_DEVICE("ULTRASCALE_PLUS"), // Set the device version (ULTRASCALE, ULTRASCALE_PLUS,// ULTRASCALE_PLUS_ES1, ULTRASCALE_PLUS_ES2).TBYTE_CTL("TBYTE_IN"), // Select between T and TBYTE_IN inputs.TX_DATA_WIDTH(8), // Parallel data input width (4-8).TX_DELAY_FORMAT("TIME"), // Units of the TX DELAY_VALUE (COUNT, TIME).TX_DELAY_TYPE("FIXED"), // Set the type of TX tap delay line (FIXED, VARIABLE, VAR_LOAD).TX_DELAY_VALUE(0), // TX Input delay value setting in ps.TX_OUTPUT_PHASE_90("FALSE"), // Delays the output phase by 90-degrees.TX_REFCLK_FREQUENCY(CLK_FREQ), // Specification of the TX reference clock frequency in MHz (200.0-2667.0).TX_UPDATE_MODE("ASYNC") // Determines when updates to the delay will take effect (ASYNC, MANUAL,// SYNC))RXTX_BITSLICE_dq_inst (.FIFO_EMPTY(FIFO_EMPTY), // 1-bit output: FIFO empty flag.FIFO_WRCLK_OUT(FIFO_WRCLK_OUT), // 1-bit output: FIFO source synchronous write clock out to the device// logic (currently unsupported, do not connect).O(O), // 1-bit output: Serialized output going to output buffer.Q(Q), // 8-bit output: Registered output data from FIFO.RX_BIT_CTRL_OUT(RX_BIT_CTRL_OUT), // 40-bit output: RX Output bus to BITSLICE_CONTROL.RX_CNTVALUEOUT(RX_CNTVALUEOUT), // 9-bit output: RX Counter value from device logic.TX_BIT_CTRL_OUT(TX_BIT_CTRL_OUT), // 40-bit output: Output bus to BITSLICE_CONTROL for TX.TX_CNTVALUEOUT(TX_CNTVALUEOUT), // 9-bit output: TX Counter value to device logic.T_OUT(T_OUT), // 1-bit output: Byte group 3-state output.D(D), // 8-bit input: Data from device logic.DATAIN(DATAIN), // 1-bit input: Input signal from IOBUF.FIFO_RD_CLK(FIFO_RD_CLK), // 1-bit input: FIFO read clock.FIFO_RD_EN(FIFO_RD_EN), // 1-bit input: FIFO read enable.RX_BIT_CTRL_IN(RX_BIT_CTRL_IN), // 40-bit input: RX Input bus from BITSLICE_CONTROL.RX_CE(RX_CE), // 1-bit input: Clock enable for IDELAY.RX_CLK(RX_CLK), // 1-bit input: RX Clock used to sample LOAD, CE, INC.RX_CNTVALUEIN(RX_CNTVALUEIN), // 9-bit input: RX Counter value from device logic.RX_EN_VTC(RX_EN_VTC), // 1-bit input: RX Enable to keep stable delay over VT.RX_INC(RX_INC), // 1-bit input: RX Increment the current delay tap setting.RX_LOAD(RX_LOAD), // 1-bit input: RX Load the CNTVALUEIN tap setting.RX_RST(RX_RST), // 1-bit input: RX Asynchronous assert, synchronous deassert for// RXTX_BITSLICE ISERDES.RX_RST_DLY(RX_RST_DLY), // 1-bit input: RX Reset the internal DELAY value to DELAY_VALUE.T(T), // 1-bit input: Legacy T byte input from device logic.TBYTE_IN(TBYTE_IN), // 1-bit input: Byte group 3-state input from TX_BITSLICE_TRI.TX_BIT_CTRL_IN(TX_BIT_CTRL_IN), // 40-bit input: TX Input bus from BITSLICE_CONTROL.TX_CE(TX_CE), // 1-bit input: Clock enable for ODELAY.TX_CLK(TX_CLK), // 1-bit input: TX Clock used to sample LOAD, CE, INC.TX_CNTVALUEIN(TX_CNTVALUEIN), // 9-bit input: TX Counter value from device logic.TX_EN_VTC(TX_EN_VTC), // 1-bit input: TX Enable to keep stable delay over VT.TX_INC(TX_INC), // 1-bit input: TX Increment the current delay tap setting.TX_LOAD(TX_LOAD), // 1-bit input: TX Load the CNTVALUEIN tap setting.TX_RST(TX_RST), // 1-bit input: TX Asynchronous assert, synchronous deassert for// RXTX_BITSLICE OSERDES.TX_RST_DLY(TX_RST_DLY) // 1-bit input: TX Reset the internal DELAY value to DELAY_VALUE);IOBUF IOBUF_dqs_inst (.O(DATAIN), // Buffer output.IO(dq), // Diff_p inout (connect directly to top-level port).I(O), // Buffer input.T(T_OUT) // 3-state enable input, high=input, low=output);endmodule

- dqs.v

`timescale 1ns / 1ps

//

// Company:

// Engineer: wjh776a68

//

// Create Date: 01/29/2024 05:58:32 PM

// Design Name:

// Module Name: dqs

// Project Name:

// Target Devices: xcvu37p

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//module dqs #(parameter CLK_FREQ = 1333.333

) (inout dqs_t,inout dqs_c,// output [39:0] TRI_BIT_CTRL_OUT,// input [39:0] TRI_BIT_CTRL_IN,output [39:0] RX_BIT_CTRL_OUT, // outputoutput [39:0] TX_BIT_CTRL_OUT, // outputoutput [7:0] Q, // outputinput [7:0] D, // input -- assoutput FIFO_EMPTY, // outputinput FIFO_RD_CLK, // input -- assinput FIFO_RD_EN, // input -- assinput [39:0] RX_BIT_CTRL_IN, // inputinput [39:0] TX_BIT_CTRL_IN, // inputinput TBYTE_IN, // input// input [3:0] TRI_TBYTE_INinput rst

);logic [8:0] TX_CNTVALUEOUT; // output // internallogic [8:0] RX_CNTVALUEOUT; // output // internallogic O; // output -- ass // internallogic T_OUT; // output -- ass // internallogic DATAIN; // input -- ass // internallogic FIFO_WRCLK_OUT; // output // internallogic T = 1'b0; // inputlogic TX_CE = 1'b0; // input -- asslogic TX_CLK = 1'b1; // input -- asslogic RX_CE = 1'b0; // input -- asslogic RX_CLK = 1'b1; // input -- asslogic [8:0] RX_CNTVALUEIN = 9'b0; // input -- asslogic RX_EN_VTC = 1'b1; // input -- asslogic RX_INC = 1'b0; // input -- asslogic RX_LOAD = 1'b0; // input -- asswire RX_RST = rst; // input -- asswire RX_RST_DLY = rst; // input -- asslogic [8:0] TX_CNTVALUEIN = 9'b0; // input -- asslogic TX_EN_VTC = 1'b1; // input -- asslogic TX_INC = 1'b0; // input -- asslogic TX_LOAD = 1'b0; // input -- asswire TX_RST = rst; // input -- asswire TX_RST_DLY = rst; // input -- assRXTX_BITSLICE #(.ENABLE_PRE_EMPHASIS("FALSE"), // Enable the pre-emphasis.FIFO_SYNC_MODE("FALSE"), // Internal write clock and FIFO_RD_CLK are coming from a common source.INIT(1'b1), // Defines initial O value.IS_RX_CLK_INVERTED(1'b0), // Optional inversion for RX_CLK.IS_RX_RST_DLY_INVERTED(1'b0), // Optional inversion for RX_RST_DLY.IS_RX_RST_INVERTED(1'b0), // Optional inversion for RX_RST.IS_TX_CLK_INVERTED(1'b0), // Optional inversion for TX_CLK.IS_TX_RST_DLY_INVERTED(1'b0), // Optional inversion for TX_RST_DLY.IS_TX_RST_INVERTED(1'b0), // Optional inversion for TX_RST.RX_DATA_TYPE("DATA_AND_CLOCK"), // Defines what the RX input pin is carrying (CLOCK, DATA, DATA_AND_CLOCK,// SERIAL).RX_DATA_WIDTH(8), // Defines the width of the serial-to-parallel converter (4-8).RX_DELAY_FORMAT("TIME"), // Units of the RX DELAY_VALUE (COUNT, TIME).RX_DELAY_TYPE("FIXED"), // Set the type of RX tap delay line (FIXED, VARIABLE, VAR_LOAD).RX_DELAY_VALUE(0), // RX Input delay value setting in ps.RX_REFCLK_FREQUENCY(CLK_FREQ), // Specification of the RX reference clock frequency in MHz (200.0-2667.0).RX_UPDATE_MODE("ASYNC"), // Determines when updates to the RX delay will take effect (ASYNC,// MANUAL, SYNC).SIM_DEVICE("ULTRASCALE_PLUS"), // Set the device version (ULTRASCALE, ULTRASCALE_PLUS,// ULTRASCALE_PLUS_ES1, ULTRASCALE_PLUS_ES2).TBYTE_CTL("TBYTE_IN"), // Select between T and TBYTE_IN inputs.TX_DATA_WIDTH(8), // Parallel data input width (4-8).TX_DELAY_FORMAT("TIME"), // Units of the TX DELAY_VALUE (COUNT, TIME).TX_DELAY_TYPE("FIXED"), // Set the type of TX tap delay line (FIXED, VARIABLE, VAR_LOAD).TX_DELAY_VALUE(0), // TX Input delay value setting in ps.TX_OUTPUT_PHASE_90("FALSE"), // Delays the output phase by 90-degrees.TX_REFCLK_FREQUENCY(CLK_FREQ), // Specification of the TX reference clock frequency in MHz (200.0-2667.0).TX_UPDATE_MODE("ASYNC") // Determines when updates to the delay will take effect (ASYNC, MANUAL,// SYNC))RXTX_BITSLICE_dqs_inst (.FIFO_EMPTY(FIFO_EMPTY), // 1-bit output: FIFO empty flag.FIFO_WRCLK_OUT(FIFO_WRCLK_OUT), // 1-bit output: FIFO source synchronous write clock out to the device// logic (currently unsupported, do not connect).O(O), // 1-bit output: Serialized output going to output buffer.Q(Q), // 8-bit output: Registered output data from FIFO.RX_BIT_CTRL_OUT(RX_BIT_CTRL_OUT), // 40-bit output: RX Output bus to BITSLICE_CONTROL.RX_CNTVALUEOUT(RX_CNTVALUEOUT), // 9-bit output: RX Counter value from device logic.TX_BIT_CTRL_OUT(TX_BIT_CTRL_OUT), // 40-bit output: Output bus to BITSLICE_CONTROL for TX.TX_CNTVALUEOUT(TX_CNTVALUEOUT), // 9-bit output: TX Counter value to device logic.T_OUT(T_OUT), // 1-bit output: Byte group 3-state output.D(D), // 8-bit input: Data from device logic.DATAIN(DATAIN), // 1-bit input: Input signal from IOBUF.FIFO_RD_CLK(FIFO_RD_CLK), // 1-bit input: FIFO read clock.FIFO_RD_EN(FIFO_RD_EN), // 1-bit input: FIFO read enable.RX_BIT_CTRL_IN(RX_BIT_CTRL_IN), // 40-bit input: RX Input bus from BITSLICE_CONTROL.RX_CE(RX_CE), // 1-bit input: Clock enable for IDELAY.RX_CLK(RX_CLK), // 1-bit input: RX Clock used to sample LOAD, CE, INC.RX_CNTVALUEIN(RX_CNTVALUEIN), // 9-bit input: RX Counter value from device logic.RX_EN_VTC(RX_EN_VTC), // 1-bit input: RX Enable to keep stable delay over VT.RX_INC(RX_INC), // 1-bit input: RX Increment the current delay tap setting.RX_LOAD(RX_LOAD), // 1-bit input: RX Load the CNTVALUEIN tap setting.RX_RST(RX_RST), // 1-bit input: RX Asynchronous assert, synchronous deassert for// RXTX_BITSLICE ISERDES.RX_RST_DLY(RX_RST_DLY), // 1-bit input: RX Reset the internal DELAY value to DELAY_VALUE.T(T), // 1-bit input: Legacy T byte input from device logic.TBYTE_IN(TBYTE_IN), // 1-bit input: Byte group 3-state input from TX_BITSLICE_TRI.TX_BIT_CTRL_IN(TX_BIT_CTRL_IN), // 40-bit input: TX Input bus from BITSLICE_CONTROL.TX_CE(TX_CE), // 1-bit input: Clock enable for ODELAY.TX_CLK(TX_CLK), // 1-bit input: TX Clock used to sample LOAD, CE, INC.TX_CNTVALUEIN(TX_CNTVALUEIN), // 9-bit input: TX Counter value from device logic.TX_EN_VTC(TX_EN_VTC), // 1-bit input: TX Enable to keep stable delay over VT.TX_INC(TX_INC), // 1-bit input: TX Increment the current delay tap setting.TX_LOAD(TX_LOAD), // 1-bit input: TX Load the CNTVALUEIN tap setting.TX_RST(TX_RST), // 1-bit input: TX Asynchronous assert, synchronous deassert for// RXTX_BITSLICE OSERDES.TX_RST_DLY(TX_RST_DLY) // 1-bit input: TX Reset the internal DELAY value to DELAY_VALUE);IOBUFDS #(.DIFF_TERM("FALSE"), // Differential Termination ("TRUE"/"FALSE").IBUF_LOW_PWR("TRUE"), // Low Power - "TRUE", High Performance = "FALSE" .IOSTANDARD("LVDS"), // Specify the I/O standard.SLEW("SLOW") // Specify the output slew rate) IOBUFDS_dqs_inst (.O(DATAIN), // Buffer output.IO(dqs_t), // Diff_p inout (connect directly to top-level port).IOB(dqs_c), // Diff_n inout (connect directly to top-level port).I(O), // Buffer input.T(T_OUT) // 3-state enable input, high=input, low=output);endmodule

参考文献:

UltraScale 架构 SelectIO 资源 (ug571)

这篇关于【SelectIO】bitslice原语学习记录的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!