selectio专题

UltraScale 架构 SelectIO 资源之IODELAY与IOSERDES仿真与使用

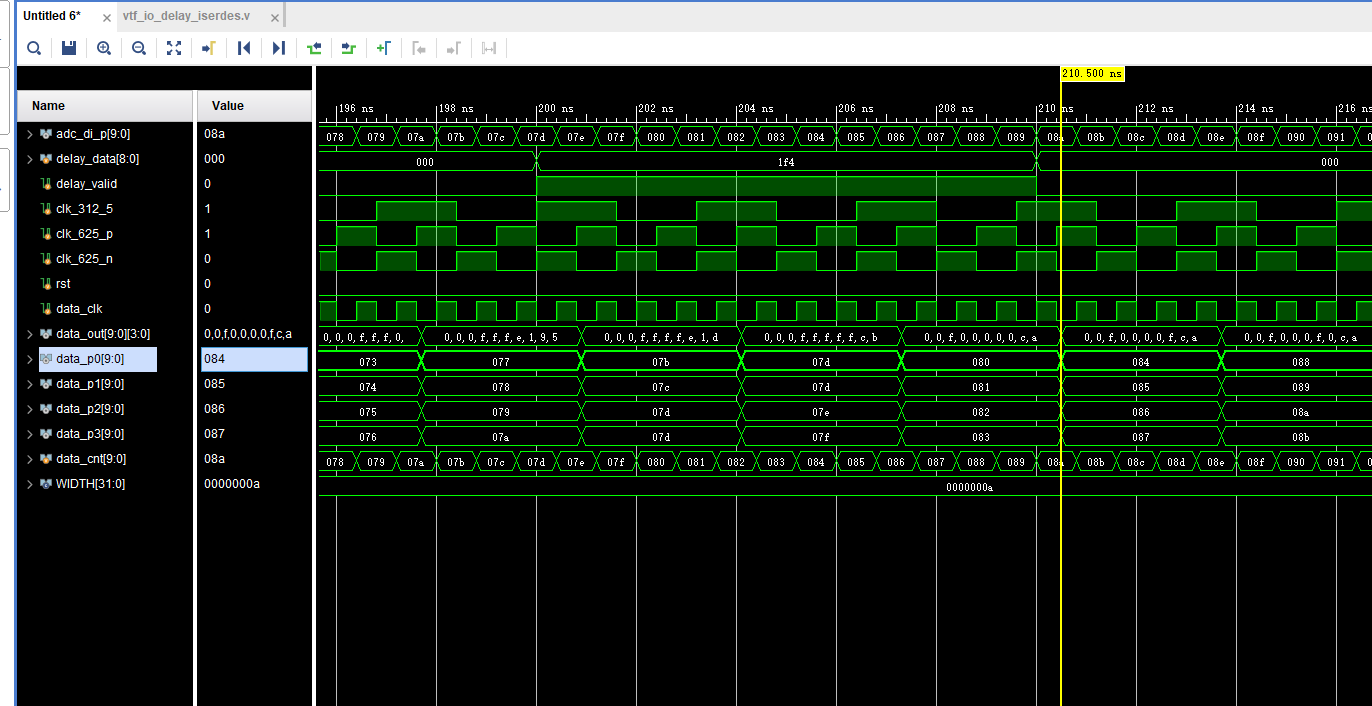

平台:vivado2018.3 具体内容见ug571-ultrascale-selectio IDELAYE3 在调试超高速信号的时候,需要使用iodelay+iserdes来调试校准输入信号。例如外部某ADC采样率为5GHZ,外部ADC使用2.5GHZ的时钟去采集输入信号。为了实现采集,adc芯片使用了4个1.25ghz采样率的小ADC来采集。但是由于FPGA的工艺,在FPGA内部无法

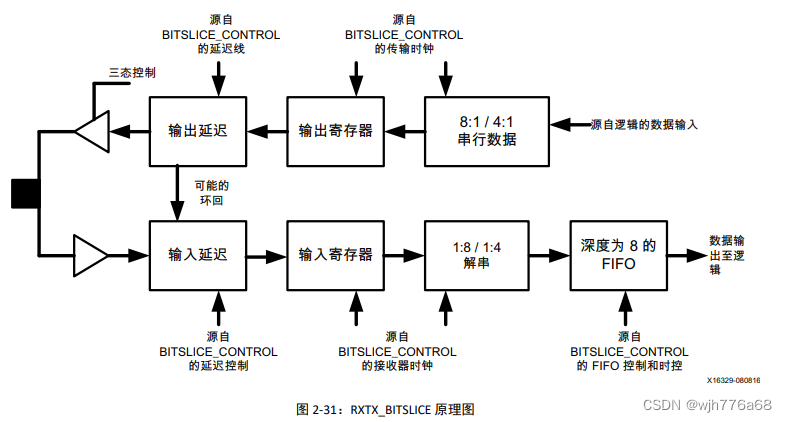

【SelectIO】bitslice原语学习记录

基本概念 在Ultrascale (plus)系列上的FPGA中,Xilinx引入了bitslice硬核,它取代了7系列上的IDELAYCTRL/IODELAY/IOSERDES/IODDR系列硬核,用于为HP(High Performance)类型Bank上的IO接口提供串并转化、信号延时、三态控制等功能。Xilinx为bitslice硬核提供了TXRX_BITSLICE/TX_BIT

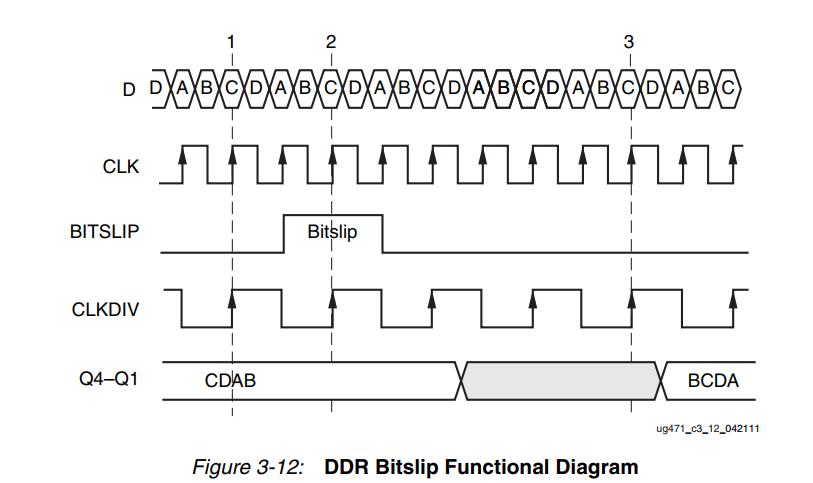

FPGA - 7系列 FPGA内部结构之SelectIO -07- 高级逻辑资源之ISERDESE2

前言 本文节选UG471的第三章,进行整理翻译,用于介绍SelectIO资源内部的ISERDESE2资源。输入串并转换器 (ISERDESE2) 和输出并串转换器 (OSERDESE2) 支持非常快的 I/O 数据速率,并允许内部逻辑运行速度降低 8 倍 比 I/O。 输入串并逻辑资源 (ISERDESE2)简介 7 系列 FPGA 中的 ISERDESE2 是专用的串并转换器,具有特定的时