uvm专题

UVM:callback机制的意义和用法

1. 作用 Callback机制在UVM验证平台,最大用处就是为了提高验证平台的可重用性。在不创建复杂的OOP层次结构前提下,针对组件中的某些行为,在其之前后之后,内置一些函数,增加或者修改UVM组件的操作,增加新的功能,从而实现一个环境多个用例。此外还可以通过Callback机制构建异常的测试用例。 2. 使用步骤 (1)在UVM组件中内嵌callback函

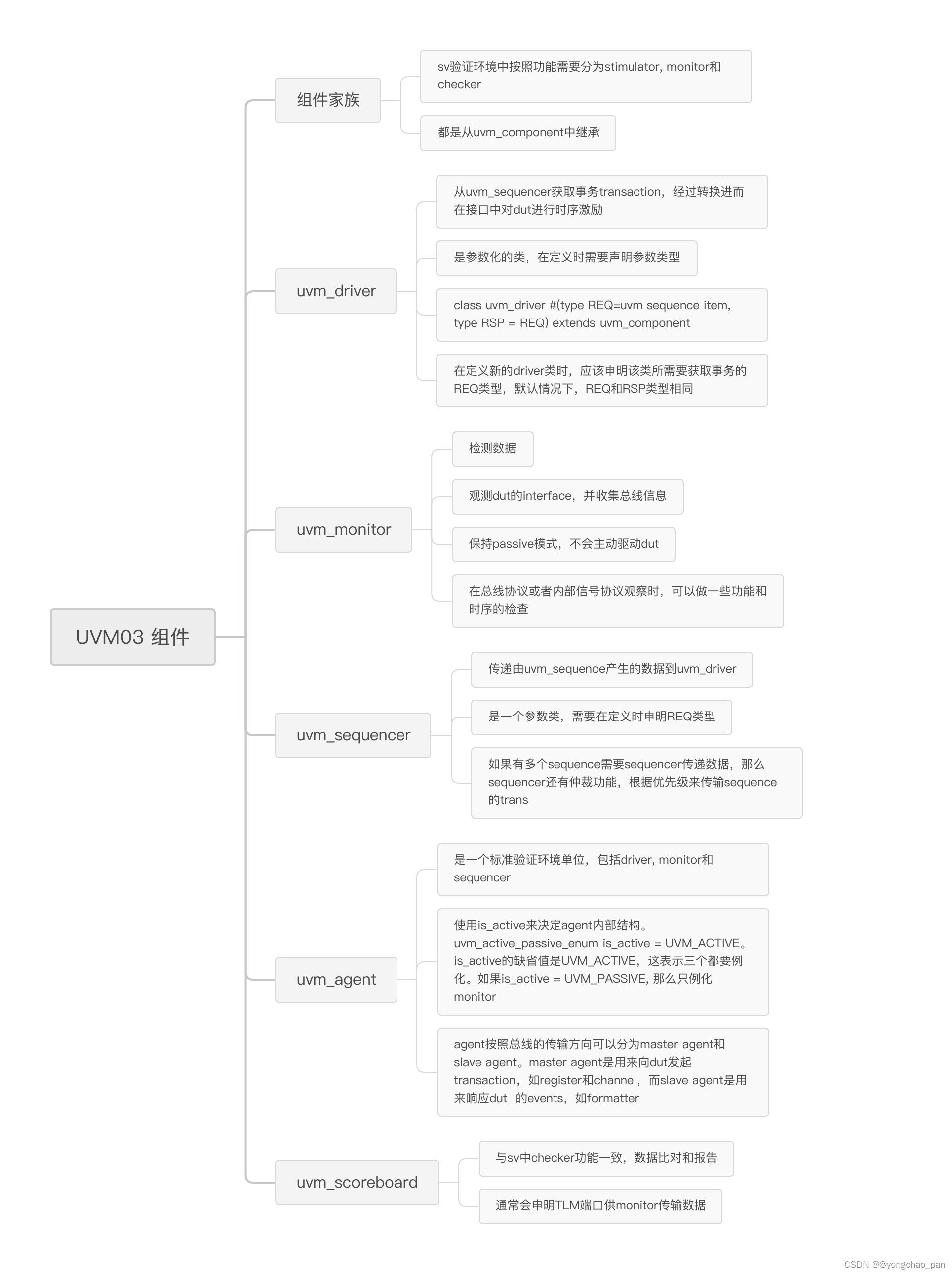

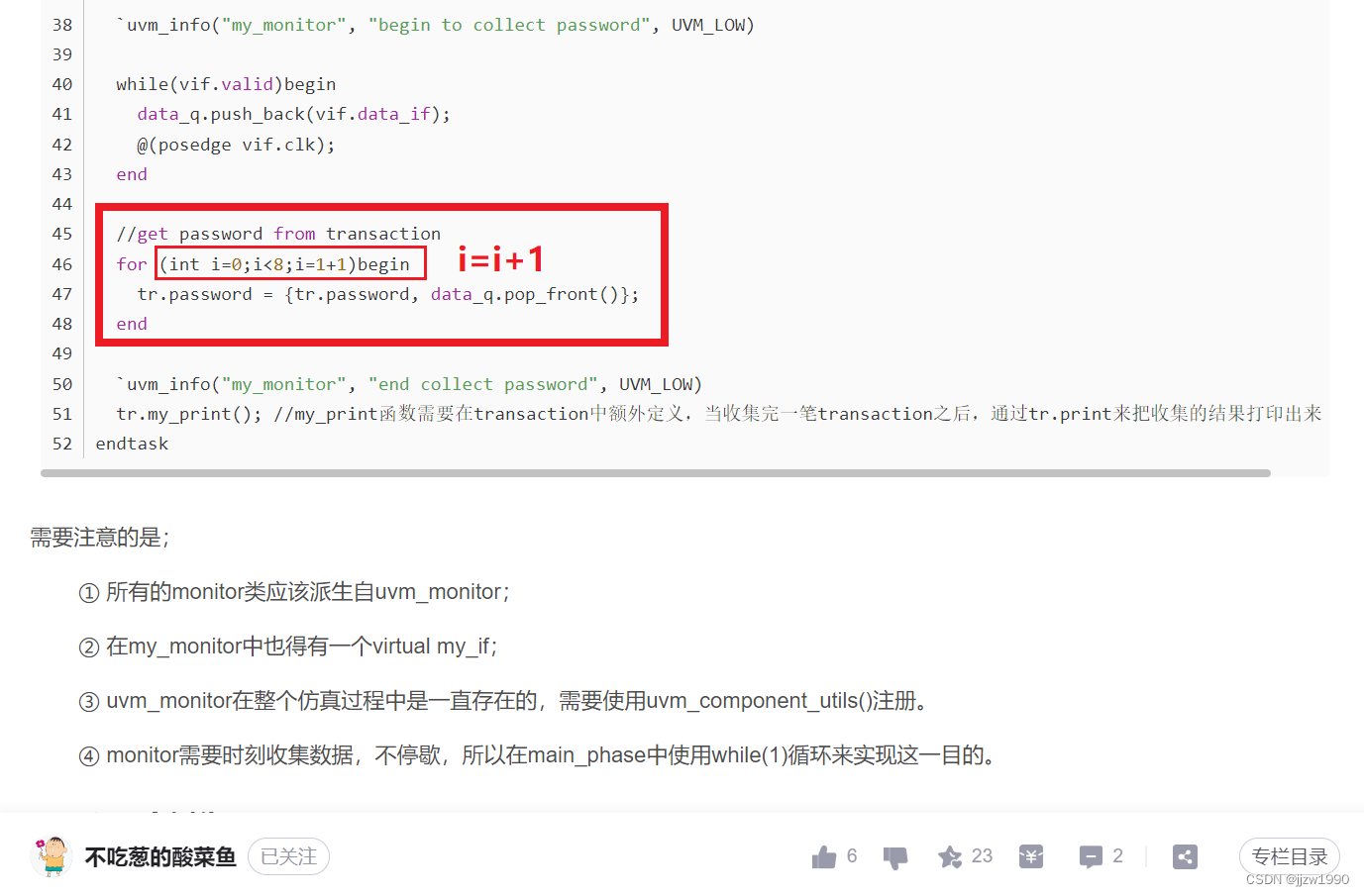

[UVM]6.component driver monitor sequencer agent scoreboard env test

1.知识点回顾 (1)component需要有parent,因为参加构成组件,所以需要(继承); (2)object与component之间间隔report_object。 2.组件家族 (1)构建寄存器模型 :uvm_reg_predictor;激励器:driver/random_stimulus/sequencer_base/sequencer;监测器:monitor;

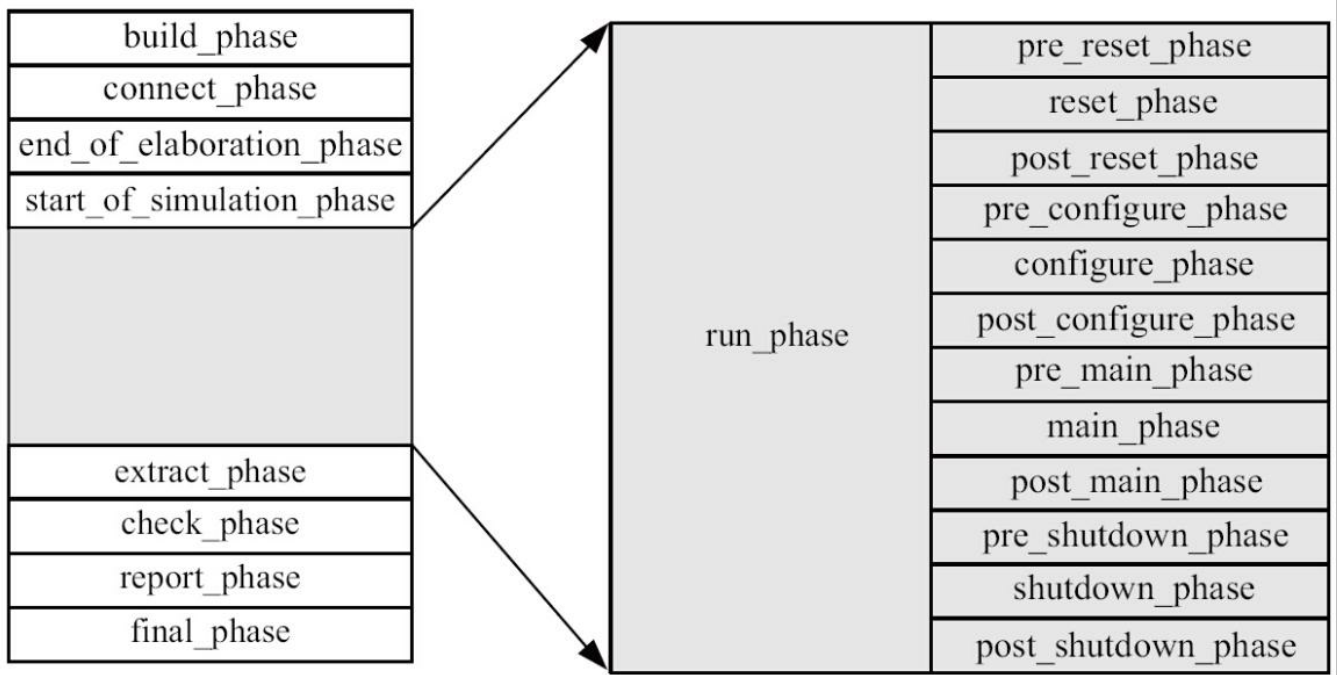

数字验证:一文弄懂UVM的phase机制

1. 9大phase 1.1 整体介绍 uvm中的phase共有9种,按照是否消耗仿真时间可以分为function phase和task phase。其中只有run_phase是耗时的,给DUT施加激励和检测输出也是在这个phase里完成的。 UVM整体框架的运行都是从tb中的一句run_test("my_test")开始 ,那么在这句程序背后发生了什么呢

UVM中的TLM(事务级建模)通信(2)

上一篇介绍了UVM中利用TLM进行的一对一通信:UVM中的TLM(事务级建模)通信(1)-CSDN博客,除此之外,UVM还有两种特殊的端口:analysis_port和analysis_export,用于完成一对多的通信。 1.analysis端口 这两种端口同样也是用于传递transaction,他们与put,get的区别是: (1)一个analysis

UVM寄存器模型使用方法

1.寄存器表格 地址 寄存器名字 域名(一个寄存器可包括多个域,域的位宽可不连续) 属性(常用:RO/RW/W1C/W1S/WC) 域位宽 域描述 注:一张完善的寄存器表格是生成寄存器模型的关键 2.根据寄存器表格生产寄存器模型 3.寄存器模型在顶层reg_base_test.sv中例化; 4.编写自定义适配器adapter.sv,主要用于将自定义trans和reg_seque

【IC验证】UVM实验lab03

1. TLM端口的创建、例化与使用 创建: uvm_get_blocking_port #(fmt_trans) mon_bp_port; 例化: function new(string name = "mcdf_refmod", uvm_component parent);super.new(name, parent);fmt_trans = new("fmt_trans", this)

利用Systemverilog+UVM搭建SOC及ASIC的RTL验证环境

在集成电路设计的复杂世界中,验证环节是确保设计满足预期功能和性能要求的关键步骤。随着系统级芯片(SOC)和特定应用集成电路(ASIC)的规模和复杂性不断增加,传统的验证方法已经难以满足高效、准确的验证需求。因此,采用先进的验证方法学和工具变得尤为重要。 SystemVerilog(SV)和通用验证方法学(UVM)作为当前硬件验证领域的两大支柱,提供了一套完整的框架和工具,用于构建可扩展、可重用的

`uvm_component_utils

功能意义用法 功能意义 这是一个宏,而且是无参数的宏。作用是注册新类。 之所以用`uvm_component_utils , 目的是为了兼容各种仿真工具。 类似的宏,还有`uvm_object_utils。 用法 class mycomp extends uvm_component;`uvm_component_utils(mycomp);...endclass

uvm_config_db

功能意义命令解析 class hierarchyclass定义methods getsetexistswait_modified 细节注意参考文档 理解仍深入不下去,还需要不断学习uvm和systemverilog的知识。 放在这里,以备以后的提升吧。 功能意义 uvm_config_db#(T) 是一个类,用于配置uvm_component实例的资源;uvm_config

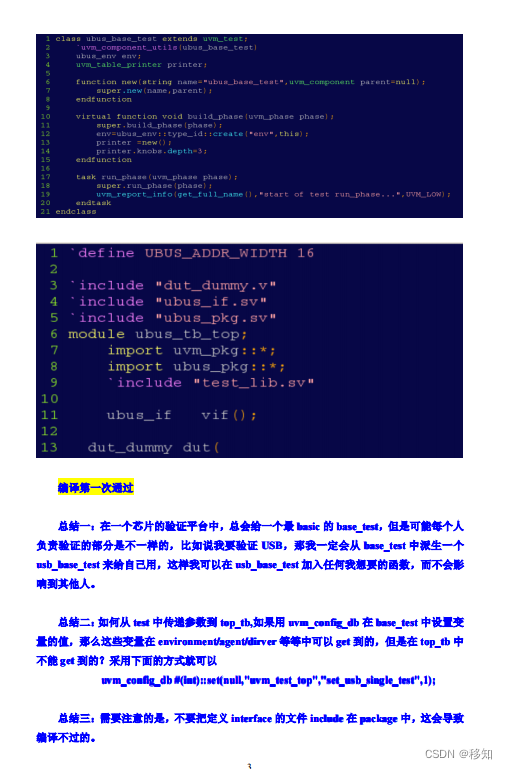

《UVM实战》,一个简单实例的源代码理解

uvm树形结构图uvm验证平台uvm启动过程源代码理解top_tbv uvm树形结构图 uvm验证平台 uvm启动过程 源代码理解:top_tb.v `timescale 1ns/1ps/** 1. uvm package. include all uvm classes and macros.* 2. uvm systemverilog 固定写法。*/`

UVM寄存器模型——手写Ralf问题debug

寄存器模型是UVM中至关重要的一部分,如果没有寄存器模型,那么验证平台对于DUT内寄存器的访问方式将十分有限,对DUT运行状态的把控也会变得更为复杂。 在验证过程中,scoreboard或者其他验证组件经常需要了解当前时间某个寄存器的值,以此来调控激励的输入或者进行数据的比对。如果不使用寄存器模型,那只能够通过启动sequence的方式,给DUT的交互端口特定的地址和操作信号,获取寄存器

《从零开始,搭建一个简单的UVM验证平台》实操

最近的工作中需要用UVM平台去仿真软件同事写的C程序,虽然只要用EDA同事已经搭好的UVM平台稍微改改就行,但对于我这种从未接触过UVM甚至都没用过System Verilog的纯FPGA工程师来说还是很有难度的,因为我对这方面一点概念都没有。 基于此,想着边用边学,就在网上找了一些资料学习。看到了下面这篇文章: 从零开始,搭建一个简单的UVM验证平台(一) 看着还是挺简单的,但亲自动手去做

芯片验证 | UVM的phase机制

最近在尝试搭建UVM的环境,作为一个入门新手,关于phase的概念不是很清晰,这里记录一下。 看了蛮多的Blog,内容都很不错。最后还是打开了白皮书,书的内容更加的全面。以下内容全部来自白皮书。 phase机制 1 task phase与function phase UVM中的phase,按照其是否消耗仿真时间($time打印出的时间)的特性,可以分成两大类, 一类是function

24届数字IC验证——SV+UVM基础知识汇总(九)

文章目录 前言57、module和program区别58、仿真调度区域59、fork-join、fork-join_none和fork-join_any的区别(经常问)60、D触发器输入高阻,输出是什么61、recovery time和removal time62、设置仿真退出时间62、$ time和$ realtime区别63、选择验证的原因(常问)64、验证工程师需要具有的品质65、FP

24届数字IC验证——SV+UVM基础知识汇总(四)

文章目录 前言16、约束的类型、solve…before(1)内嵌约束和class里面的约束有何区别(2)solve…before和if-else区别 17、断言(1)intersect、and、or、throughout、within区别(2)within和throughout的区别(3)并发断言主要组成有哪几个层次(4)如何检测随机化是否成功(5)什么时候随机失败(6)$rose和pos

【System Verilog and UVM基础入门21】get_type_name和get_full_name学习

从小父亲就教育我,要做一个对社会有用的人! virtual function string get_full_name () 对于uvm_component,get_type_name()打印出来的就是当前类的名称!想想为什么,要在代码前面加上get_type_name()它呢?

uvm中的回调函数,也就是callback methods有什么作用?使用场景是什么?

在UVM(Universal Verification Methodology)中,回调(Callback)是一种非常强大的机制,允许用户在不修改现有代码的情况下向类的行为中插入额外的逻辑。UVM回调是通过UVM的回调类实现的,这允许用户扩展和定制组件的行为。 作用: UVM回调的主要作用是提高了代码的可复用性和灵活性。你可以在不改变原有验证组件(如驱动器、监视器、得分板等)的代码的情况下,插

UVM: 1_UVM历史等介绍

1验证语言 1.1. Verilog 1)起源于20世纪80年代中期,1995年成为IEEE standard,即 IEEE Standard 1364 — 1995. 2)后续版本2001年推出。 3)最新标准2005年推出,即 IEEE Standard 1364 — 2005. 1.2Systemverilog 1)起源于2002年。 2)2004年发行。基于Accell

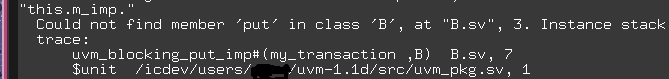

UVM:4.2.2 UVM中的 IMP

1.除了PORT 和 EXPORT外,还有第三种端口:IMP。它才是UVM 的精髓,承担UVM 中TLM的大部分代码实现。源码: 1)和之前的15 种PORT 和EXPORT一一对应。 2)IMP 不能发起操作,只作为终点,被动承担者。 3)PORT,EXPORT,IMP 优先级从高到低。PORT 可以直接连接到IMP。 4)第一个参数是传输类型。第二个参数是“在哪个compon

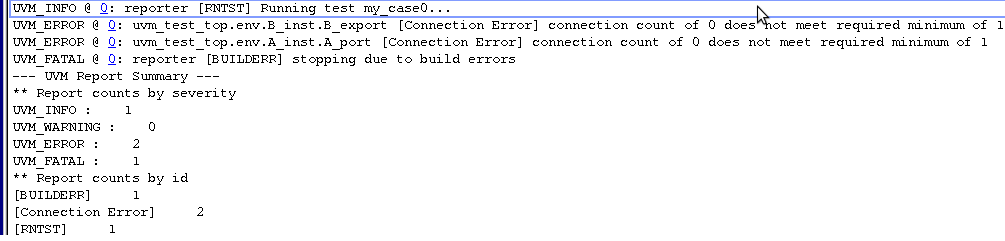

UVM:4.2.1 PORT 与 EXPORT 的连接

1.使用connect 函数建立连接:A.port.connect(B.export)。不能写成B.export.connect(A.port),因为A是发起者,B是接受者。 2.A 的代码: uvm_blocking_put_port 的源码: min_size 和max_size是必须连接到这个PORT的下级端口数量的最小值和最大值,即此PORT 应该调用的con

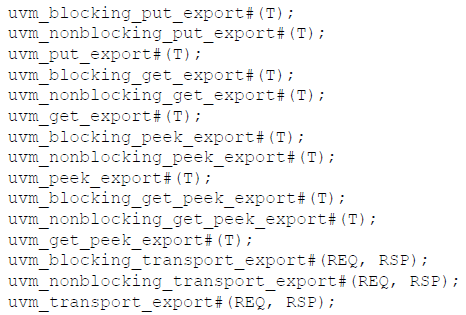

UVM:4.1.3 UVM 中的PORT 与 EXPORT

1.UVM 中常用的PORT有: 总结到一起: 1)put,get,transport 都是3个。 2)peek与get 类似,都是主动获取数据。是有区别的。。。 3)get_peek结合了get 和peek 的功能。 4)前12个的参数就是PORT中的数据类型,后3个是request的类型和response的类型。 5)如果没有指定是否阻塞,则都可以当。(都可

UVM:4.1.2 TLM定义

1.UVM 提供了TLM1.0 和TLM2.0。后者在前者基础上扩展。这里只讲TLM1.0。 1)put操作:发起者A 给B 发transaction。A是port,B的EXPORT。 2)get操作:A向B索取一个transaction。A还是port,B还的EXPORT。 2.1)PORT 和EXPORT体现的是控制流,而不是数据流。 2.2)发起者是PORT,被动接受者是EXP

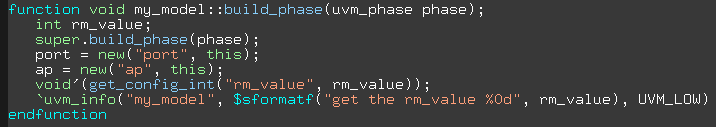

UVM:3.5.9 set_config 与 get_config

UVM1.2 已彻底废除这两个函数,永远消失了。。。。 随便写写: 1. 用set_config_int来代替uvm_config_db#(int): 2.my_model中使用get_config_int来获取参数值: 3.可以新旧交叉使用。旧的还有string 和 object。新的强大之处不止旧的3种。

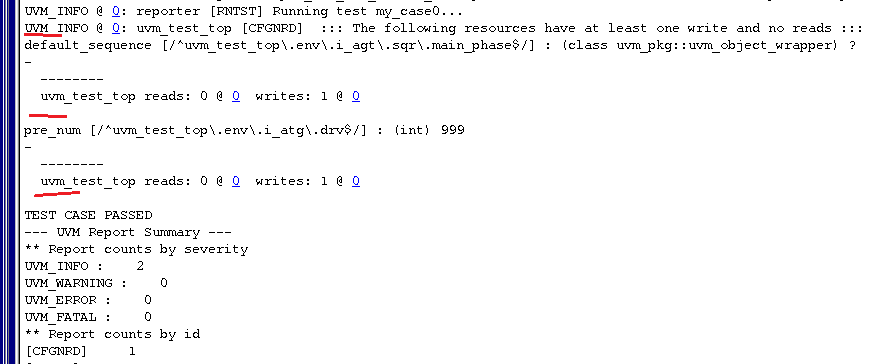

UVM:3.5.8 check_config_usage

1.假如在set 的时候,不小心把第二个参数 i_agt 写出i_atg,UVM 不会提示任何错误。 2UVM 提供了check_config_usage,它会显示出,截止到此函数被调用是有哪些是被设置过,但是没有被获取的。 3.由于config_db 的set 和get 是在build_phase执行,check_config_usage 一般在connect_phase 被调用,之后的ph

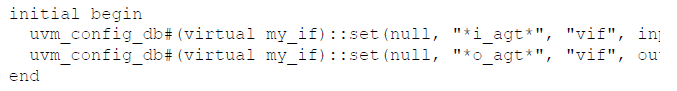

UVM:3.5.7 config_db 机制对通配符的支持

config_db::set时,第二个参数都是完整的路径。还可以用通配符*: 之前: 可以把前两个set 合并为一个set: 可以进一步简化为: 不推荐使用通配符,容易产生交互问题。

![[UVM]6.component driver monitor sequencer agent scoreboard env test](https://i-blog.csdnimg.cn/direct/d6155f8e9cb5494582087a4fa47916e2.png)