本文主要是介绍UVM:4.2.2 UVM中的 IMP,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

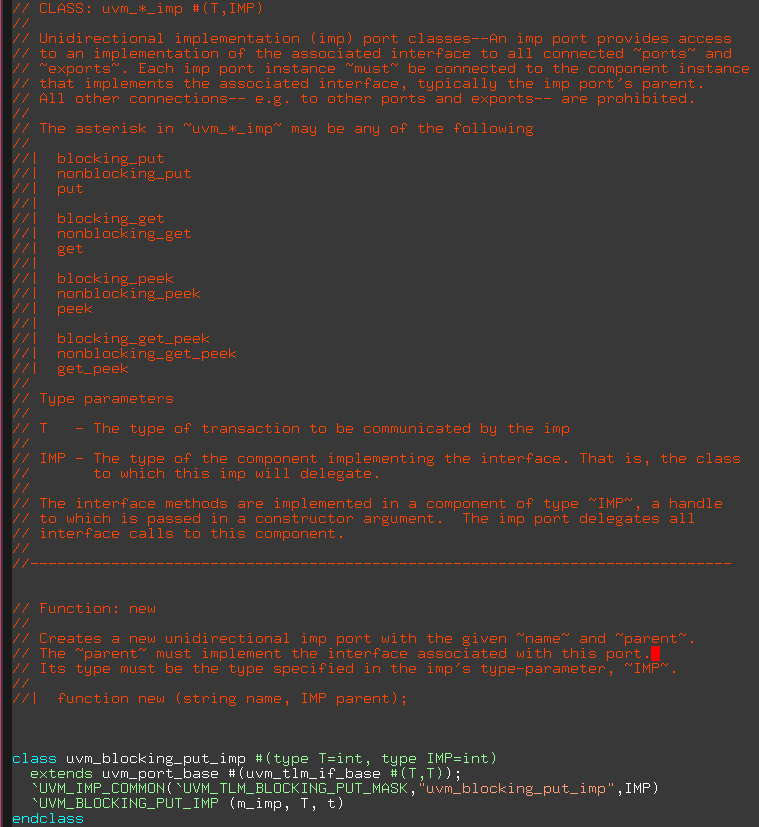

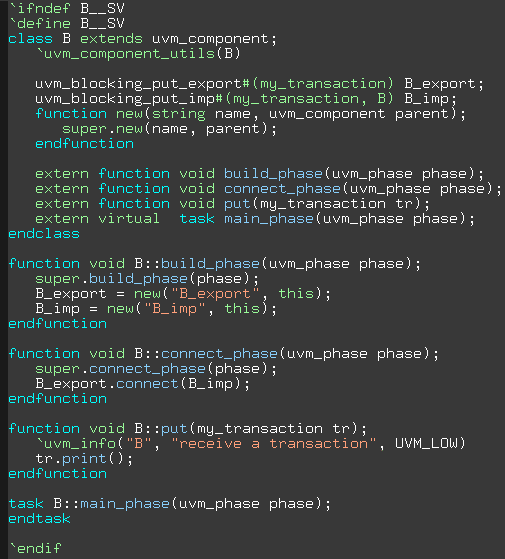

1.除了PORT 和 EXPORT外,还有第三种端口:IMP。它才是UVM 的精髓,承担UVM 中TLM的大部分代码实现。源码:

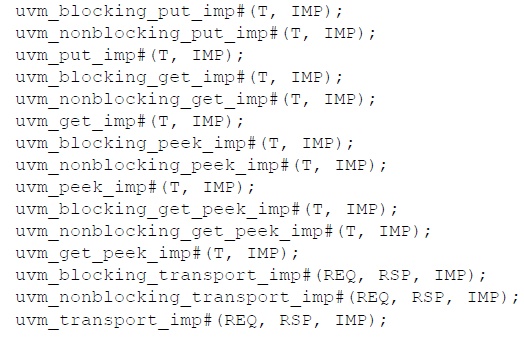

1)和之前的15 种PORT 和EXPORT一一对应。

2)IMP 不能发起操作,只作为终点,被动承担者。

3)PORT,EXPORT,IMP 优先级从高到低。PORT 可以直接连接到IMP。

4)第一个参数是传输类型。第二个参数是“在哪个component”。

2.实现过程:

1)A.A_port.put(transaction)调用B.B_export 的put。

2)B.B_export 的put(transaction)又会调用B.B_imp 的put(transaction)。

3)B_imp.put最终会调用B 的相关任务,如B.put(transaction)。

4)所以关于A_port 的操作最终会落到B.put 这个任务上。

5)是属于B 的一个任务,与A 无关,与A 的PORT 无关,也与B 的EXPORT 和IMP 无关。

6)最终要B component 实现接口的操作。所以每个IMP 都要和一个component 对应。

3.A:

B:

env:和上一次一样

仿真通过。

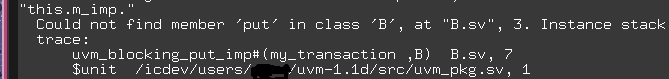

4.把B 中的put 删掉:

报错了。

这篇关于UVM:4.2.2 UVM中的 IMP的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!

![[UVM]6.component driver monitor sequencer agent scoreboard env test](https://i-blog.csdnimg.cn/direct/d6155f8e9cb5494582087a4fa47916e2.png)