sdc专题

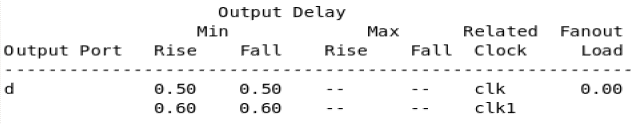

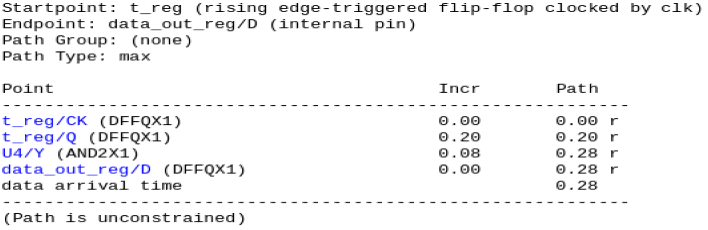

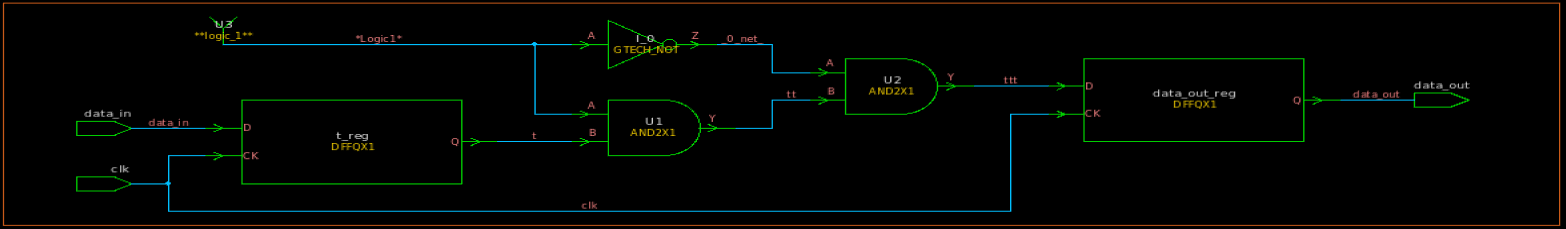

静态时序分析:SDC约束命令set_output_delay详解

相关阅读 静态时序分析https://blog.csdn.net/weixin_45791458/category_12567571.html?spm=1001.2014.3001.5482 目录 指定延迟值 指定端口、引脚列表 指定参考时钟 简单使用 指定时钟下降沿 指定参考端口、引脚 包含源、网络延迟 指定电平敏感 指定上升、下降沿 指定最大、最小条件 指定不覆盖

静态时序分析:SDC约束命令set_disable_timing详解

静态时序分析https://blog.csdn.net/weixin_45791458/category_12567571.html 目录 指定对象列表 指定源、目的引脚 指定恢复 简单使用 写在最后 上一章中,我们学习了如何使用set_case_analysis模式分析命令,它通过指定某个端口或引脚为固定值,从而使设计中的一些时序弧失效。本章将学习set_d

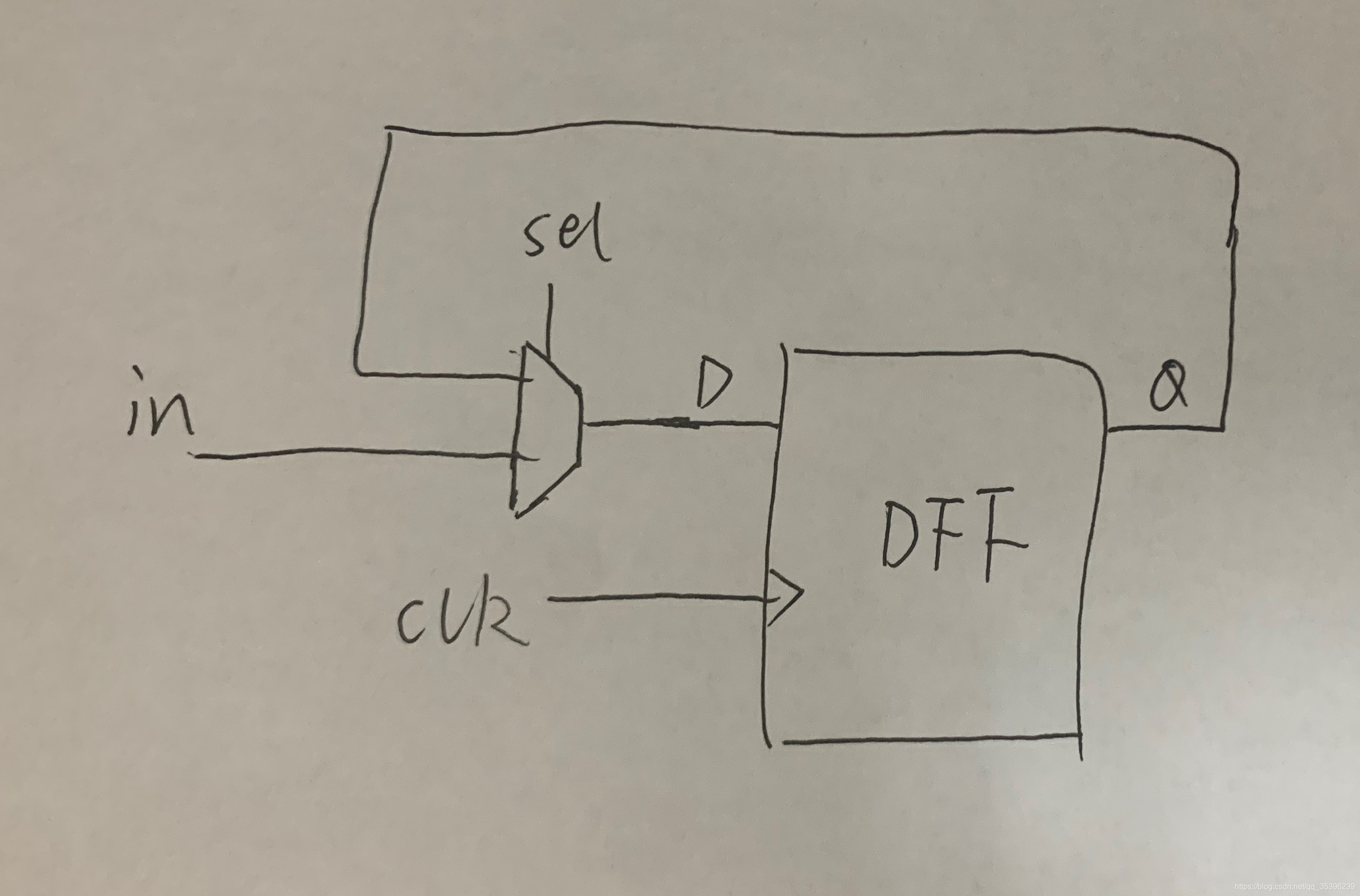

静态时序分析:SDC约束命令set_case_analysis详解

相关阅读 静态时序分析https://blog.csdn.net/weixin_45791458/category_12567571.html?spm=1001.2014.3001.5482 目录 指定值 指定端口/引脚列表 简单使用 set_case_analysis命令用于对电路进行特定模式的设定,例如对于一个工作在正常模式下的芯片,其扫描触发器的测试引脚应

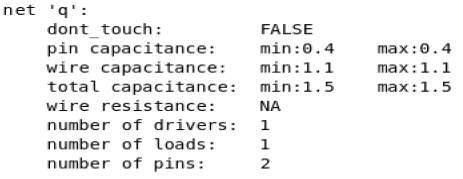

静态时序分析:SDC约束命令set_load详解

相关阅读 静态时序分析https://blog.csdn.net/weixin_45791458/category_12567571.html?spm=1001.2014.3001.5482 set_load命令用于指定端口(port)或线网(net)的负载电容,该指令的BNF范式(有关BNF范式,可以参考以往文章)为: set_loadvalue object_list

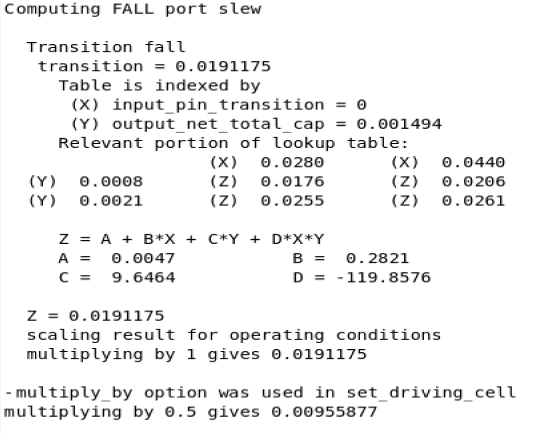

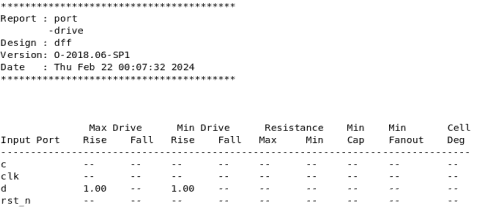

静态时序分析:SDC约束命令set_driving_cell详解

相关阅读 静态时序分析https://blog.csdn.net/weixin_45791458/category_12567571.html?spm=1001.2014.3001.5482 在上文中,我们不建议使用set_drive命令而是使用set_driving_cell命令,这是一个描述输入端口驱动能力更精确的方法。因为大多数情况下,只有库单元的设计者熟悉单元门内部

静态时序分析:SDC约束命令set_drive详解

相关阅读 静态时序分析https://blog.csdn.net/weixin_45791458/category_12567571.html 本章将讨论使用set_drive命令,它用于对输入端口的驱动能力建模。首先需要说明的是,默认情况下,DC在STA时默认输入端口的转换时间是0,这对于大多数情况来说过于理想。 set_drive命令设置了驱动端口的上

存储系统如何规避数据静默错误SDC?

存储系统规避数据静默错误(Silent Data Corruption, SDC)是一项复杂且关键的任务,涉及多个层次的技术和策略。数据静默错误是指在存储或传输过程中发生的错误,这些错误未被检测出来,因此无法立即纠正,可能导致数据不一致、损坏或丢失。以下是几种主要的规避策略: 端到端数据保护: 在整个I/O路径上(从主机内存到磁盘介质),附加并验证校验信息,如CRC(循环冗余校验)、EC

静态时序分析:SDC约束命令set_clock_transition详解

相关阅读 静态时序分析https://blog.csdn.net/weixin_45791458/category_12567571.html?spm=1001.2014.3001.5482 在静态时序分析:SDC约束命令create_clock详解一文的最后,我们谈到了针对理想(ideal)时钟,可以使用set_clock_transition命令直接指定理想时钟到达各触

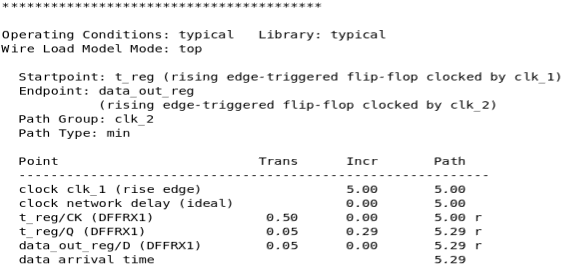

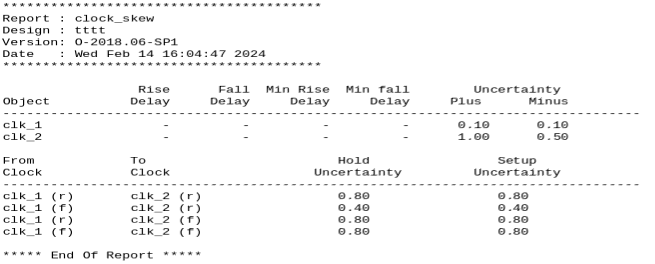

静态时序分析:SDC约束命令set_clock_uncertainty

相关阅读 静态时序分析https://blog.csdn.net/weixin_45791458/category_12567571.html?spm=1001.2014.3001.5482 set_clock_uncertainty是用来指定设计中时钟周期的不确定性,不确定性指的是对那些会对时钟周期造成的负面影响。这些不确定性可能来源于时钟抖动(clock jitter)

vivado 不支持的SDC命令

不支持以下SDC命令。 • set_clock_gating_check • set_clock_transition • set_ideal_latency • set_ideal_network • set_ideal_transition • set_max_fanout • set_drive • se

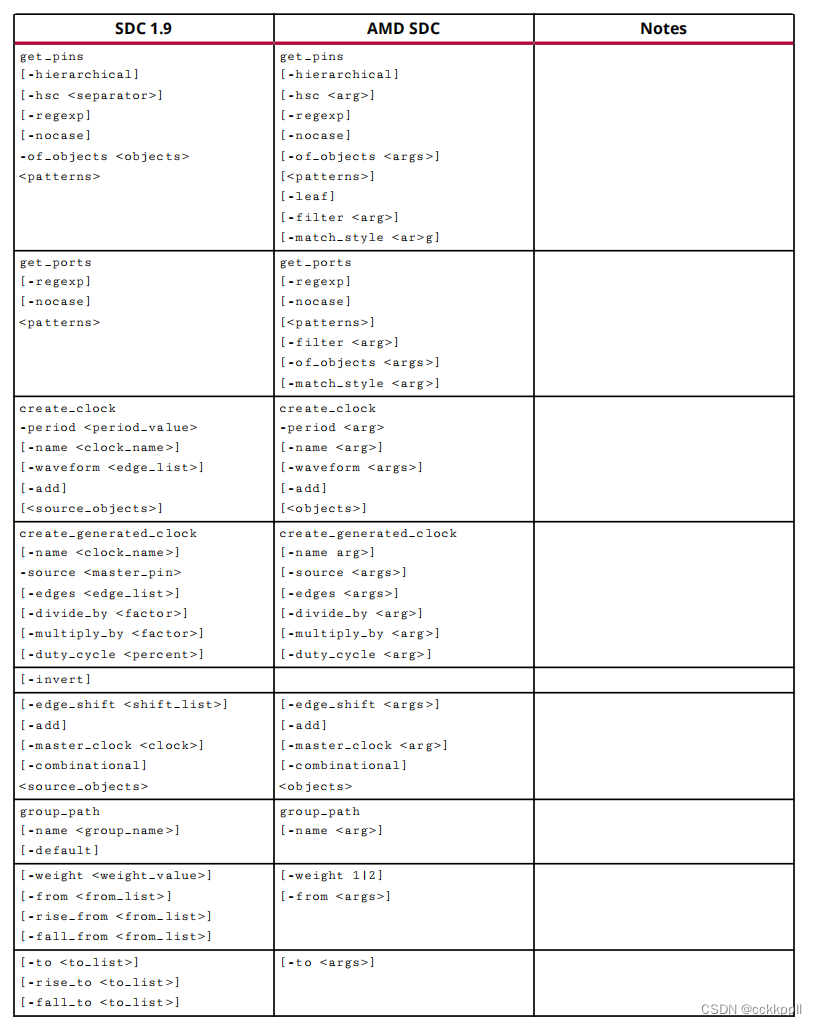

vivado 支持的XDC和SDC命令

支持的XDC和SDC命令 本附录讨论了支持的Xilinx设计约束(XDC)和Synopsys设计AMD Vivado中的约束(SDC)命令™ 集成设计环境(IDE)。 XDC文件中的有效命令 支持的SDC命令 注意:由于所有AMD Tcl命令都支持-quiet和-verbose选项,因此下表没有列出它们。

ExaGrid入围SDC Awards 2019

该公司获“年度最佳备份存储创新”提名 马萨诸塞州马尔堡--(美国商业资讯)--智能超融合备份存储器领域的领先供应商ExaGrid®今日宣布,该公司已入围“2019年存储、数字化和云大奖”(SDC Awards 2019)。SDC大奖是Angel Business Communications' IT奖的新名称,其坚定地致力于表彰和奖励在构成数字化转型基础的产品和服务方面取得的成功。ExaG

Splashtop 荣获 SDC“年度安全供应商”奖

2023年12月5日 荷兰阿姆斯特丹 Splashtop 是随处办公环境改革的先驱,在伦敦举办的第14届 SDC 颁奖典礼上荣获“年度安全供应商”奖,我们对此感到十分自豪。荣获这一知名奖项凸显了 Splashtop 致力于通过企业级加密和基于权限的访问保护不同规模组织的决心。 自2006年创立以来,Splashtop 始终致力于提供尖端的远程访问和支持技术,使用户能够随处访问设备、应用和文

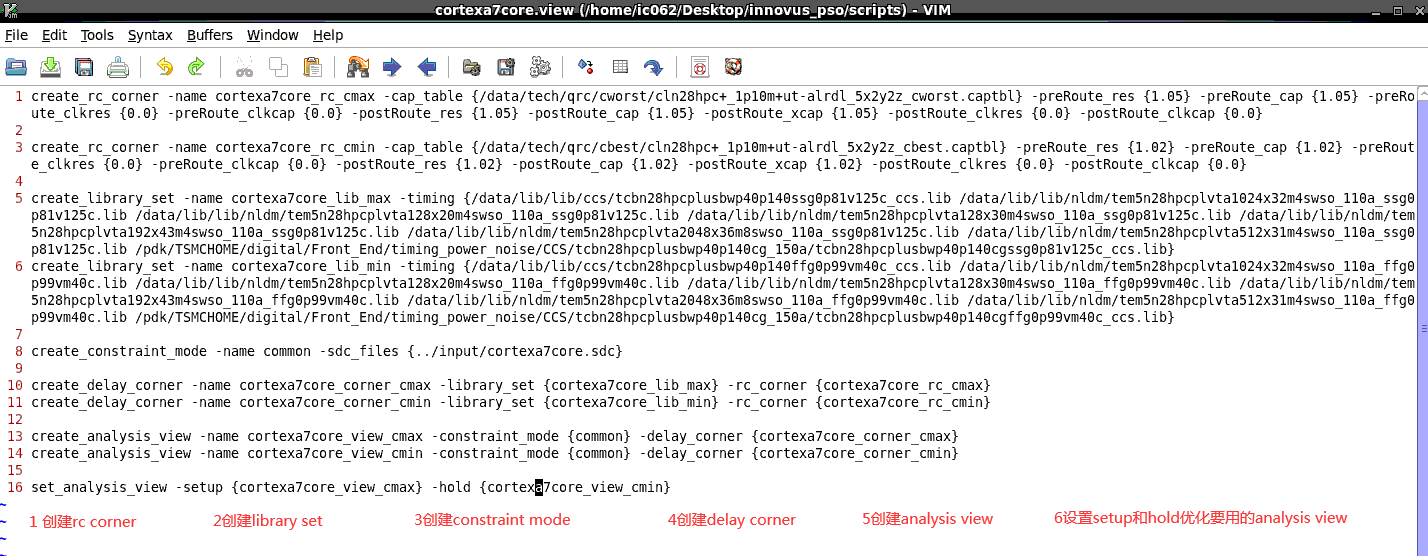

数字后端A7core项目记录1.1SDC文件、MMMC文件和lef文件

在上一篇当中,我们主要介绍了Innnvus数据导入工作,其中出现了SDC文件,MMMC文件和lef文件。 在本节进行介绍,看看各个文件当中都包含什么 上图便是SDC文件内容,这个文件是前端搞好了给我们的 时钟约束sdc主要内容如下: a.timing相关基本单位设置,kohm是千欧姆的意思 b.max_fanout,max_transition设定 c.设置模块端口port的驱动(

SDC文件常用时序约束语句

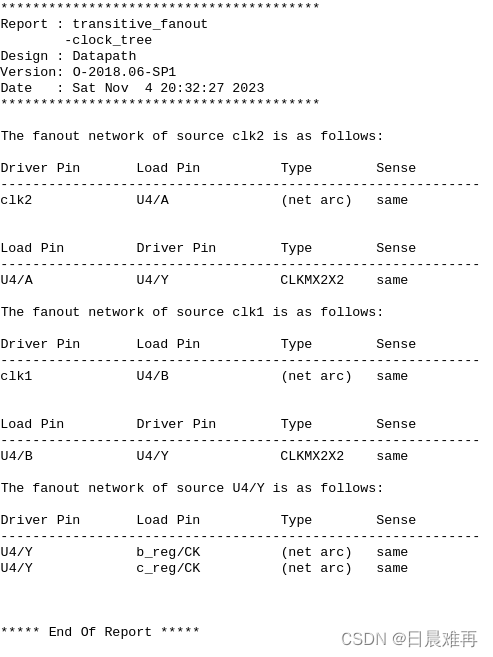

SDC可以帮助工具进行静态时序分析。在SDC中首先需要创建时钟以及时钟间对应的关系,需要注意的是,时钟间的关系(同步还是异步),并不是由时钟间本身的关系决定的,而是由SDC文件的约束决定的。即使是两个同频同相的时钟,SDC也可以将其设为异步时钟,这样工具就不会将这两个时钟作为同步时钟来进行STA分析,布线时无需考虑这两个时钟下的信号交互时所需的建立时间和保持时间;在这种情况下,这两个时钟下的信号进

SDC RPC到Kafka

SDC RPC 到卡夫卡(已弃用) 从一个或多个 SDC RPC 目标读取数据,并将其立即写入卡夫卡。在 SDC RPC 目标管道中使用 SDC RPC 到卡夫卡源。但是,到 Kafka 源的 SDC RPC 现已弃用,并将在将来的版本中被删除。我们建议使用 SDC RPC 源。 如果有多个 SDC RPC 源管道,其中包含要写入卡夫卡而无需额外处理的数据,请使用 SDC RPC 到卡夫卡源。

sdc约束设计:set_ideal_network

1、set_ideal_network 将设计中的一组端口或管脚标记为理想网络。使得目标的电阻电容都是0,而且cell和net都会dont_touch(综合不做任何优化),都是0延迟。比dont_touch更野蛮,ideal_network不再计算延迟。 设置ideal_network,免除时序相关的分析和优化、取消相关约束(Design Rule Constaints,比如ma

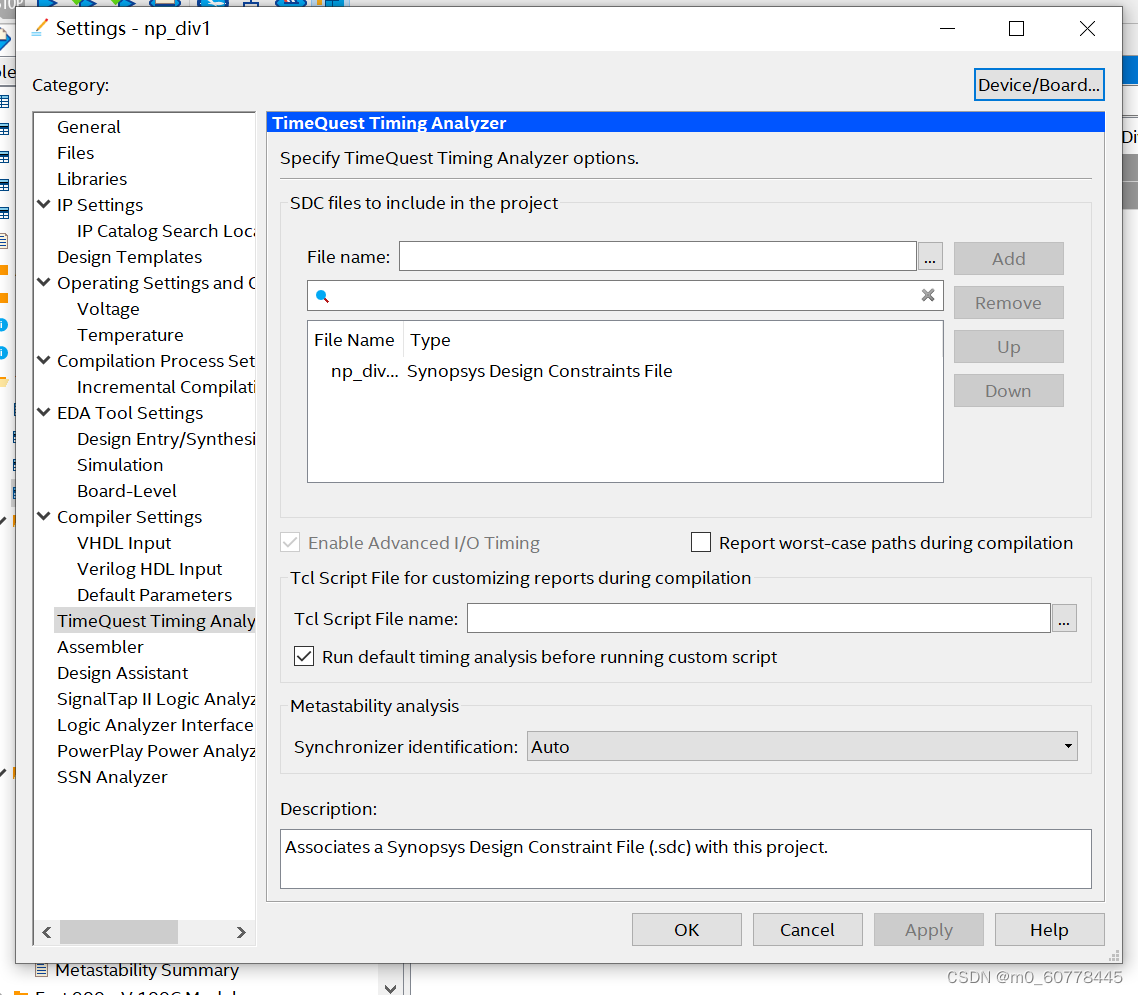

quartus导入sdc文件

QuartusⅡ开发alteraFPGA如何约束时钟(关于消除警告Timing requirements not met)_quartus 时序约束-CSDN博客 根据此生成sdc文件 导入 Assignments---->Settings-----> Timequest

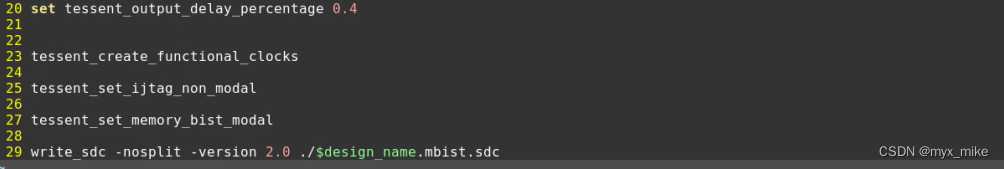

tessent mbist生成mbist SDC

在dc_shell中,先把tessent生成的design source file(可以是RTL也可能是netlist)全部load进去,然后source tessent 吐出来的那个.sdc文件,设置好参数和调用相关的proc,就可以dc_shell吐出来一个mbist sdc了。

如何使用MMC / SDC以及SPi

如何使用MMC / SDC 该安全数字存储卡(以下SDC)是一个用于移动设备的事实上的标准存储卡。SDC被开发为与多媒体卡(下面的MMC)的上部兼容。在大多数情况下,SDC完井设备也可以使用MMC。还有缩小尺寸的版本,例如RS-MMC,miniSD和microSD,具有相同的功能。MMC / SDC中有一个微控制器。闪存控制(块大小转换,纠错和磨损级别 - 称为FTL)在存储卡内部完成。数据以5

Tcl语言:SDC约束命令create_clock详解

相关阅读 Tcl语言https://blog.csdn.net/weixin_45791458/category_12488978.html?spm=1001.2014.3001.5482 在一个设计中创建一个时钟对象的SDC命令是create_clock。该指令的BNF范式(有关BNF范式,可以参考以往文章)为: create_clock[-name clock_nam

FPGA时序分析与约束(7)——通过Tcl扩展SDC

一、概述 术语“Synopsys公司设计约束”(又名SDC,Synopsys Design Constraints)用于描述对时序、功率和面积的设计要求,是EDA工具中用于综合、STA和布局布线最常用的格式。本文介绍时序约束的历史概要和SDC的描述。 二、时序约束的历史 20世纪90年代初引人了时序约束。这些主要用于指定HDL 中无法捕获的设计特性和用于驱动综

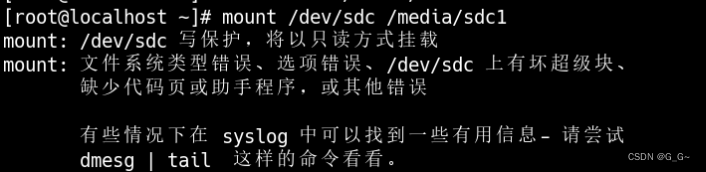

解决:mount: /dev/sdc 写保护,将以只读方式挂载mount:文件系统类型错误,别再傻傻 mkfs.ext4 /dev/sdc 格式化优盘了!

解决:mount: /dev/sdc 写保护,将以只读方式挂载mount:文件系统类型错误,别再傻傻 mkfs.ext4 /dev/sdc 格式化优盘了! 当我们用优盘连接Linux服务器时,报以下错误:前往别再执行 mkfs.ext4 /dev/sdc了,执行后你的优盘内容就没了,虽然可以挂载成功,但你需要从优盘中拷贝到服务器上的内容已经消失了。 当我们用优盘连接Linux服务