本文主要是介绍静态时序分析:SDC约束命令set_disable_timing详解,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

静态时序分析![]() https://blog.csdn.net/weixin_45791458/category_12567571.html

https://blog.csdn.net/weixin_45791458/category_12567571.html

目录

指定对象列表

指定源、目的引脚

指定恢复

简单使用

写在最后

上一章中,我们学习了如何使用set_case_analysis模式分析命令,它通过指定某个端口或引脚为固定值,从而使设计中的一些时序弧失效。本章将学习set_disable_timing命令,它可以用于直接指定失效时序弧,这会导致时序路径的中断,常常用于减少DC分析的复杂度。

set_case_analysis指令的BNF范式(有关BNF范式,可以参考以往文章)为:

set_disable_timingobject_list[-from from_pin_name -to to_pin_name][-restore]//注:该命令的-from选项和-to选项必须同时出现指定对象列表

object_list参数指定了对象列表,包括需要删除时序弧的单元、端口或引脚,这个参数是必选的。

指定源、目的引脚

-from选项和-to选项必须成对出现,它们指定了一个单元需要删除从源引脚到目的引脚这个特定的时序弧,因此如果它们使用了,则对象列表中只能有单元对象。

指定恢复

-restore选项表示将删除的时序弧恢复,此时指定的其它选项要和指定时序弧失效时的命令一致。

简单使用

首先我们可以解决静态时序分析:SDC约束命令create_clock详解一文中出现的时序路径混乱问题,原文的图7如本文图1所示,首先在输入端口clk_1和clk_2定义两个时钟。

create_clock -period 10 [get_port clk_1]

create_clock -period 15 [get_port clk_2]

图1 有两个时钟驱动的电路单元

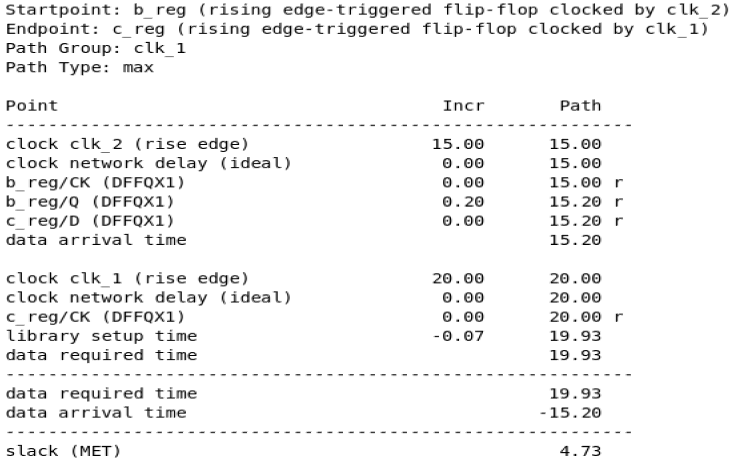

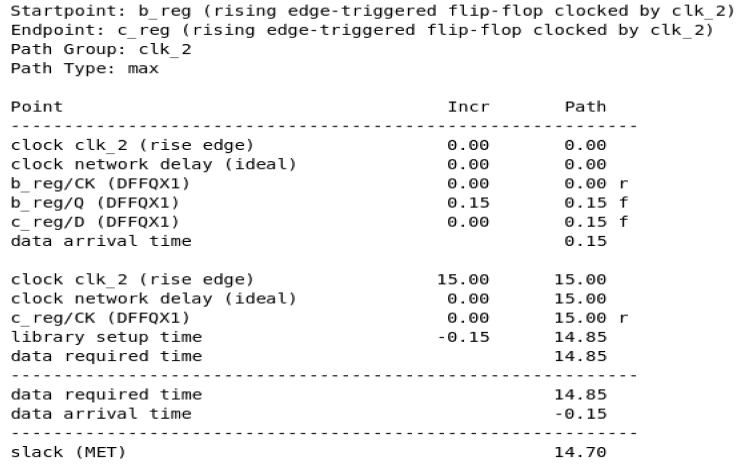

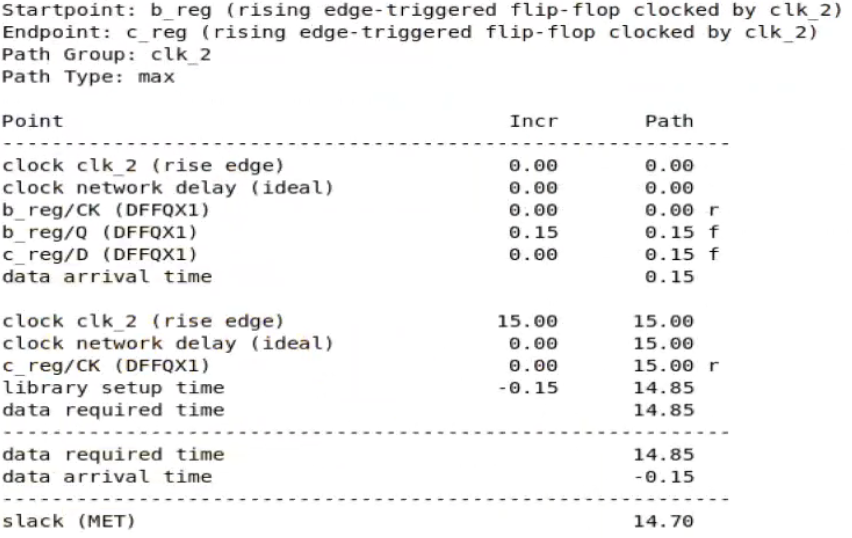

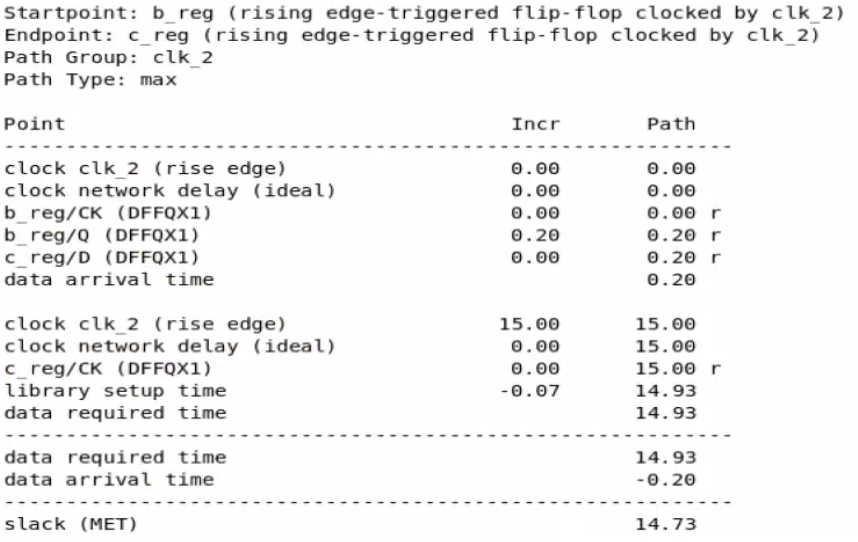

对于上面的电路,本意是b_reg触发器和c_reg触发器同时受时钟clk_1或时钟clk_2之一触发,但如果不使用set_case_analysis命令,在使用report_timing命令后会出现时钟clk_2和时钟clk_1之间的时序分析报告,如图2、图3所示,我们真正需要的是图4的时序报告(本文如不加说明,默认时序报告为建立时间报告)。

图2 发射时钟是clk_2,捕获时钟时clk_1

图3 发射时钟是clk_2,捕获时钟时clk_1

图4 发射时钟是clk_2,捕获时钟是clk_2

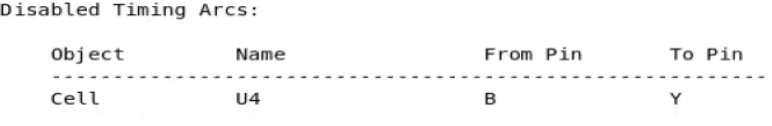

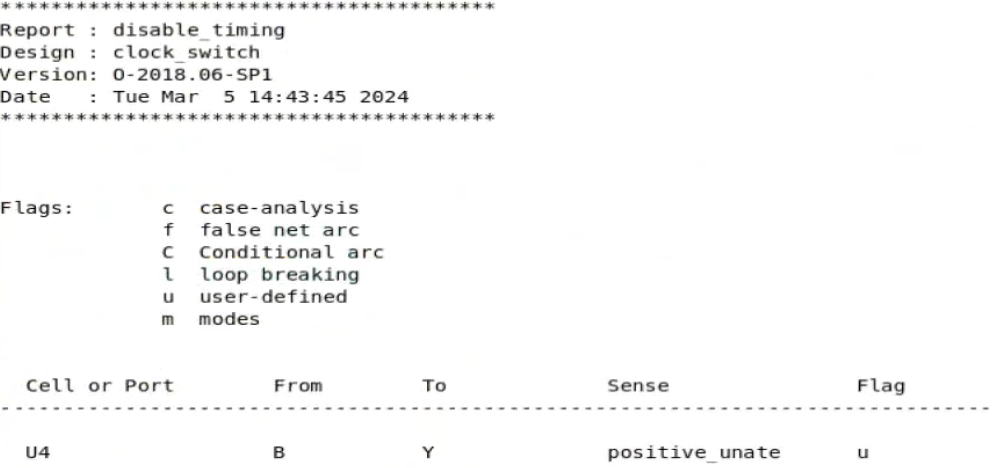

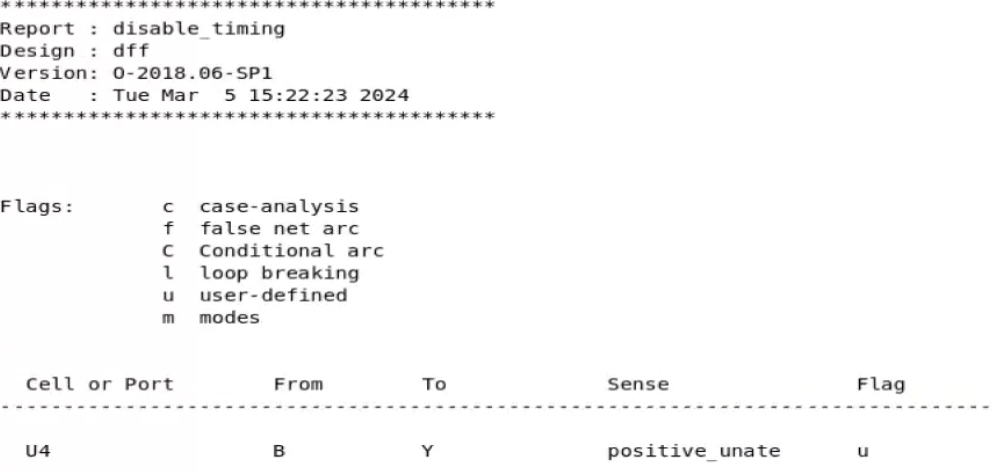

下面我们使用set_disable_timing命令,直接使得数据选择器U4从输入引脚B到输出引脚Y的时序弧失效,当然你也可以是使输入引脚S0到输出引脚Y的时序弧也失效,但由于输入引脚不会定义始终,因此它可以省略。可以通过report_design命令或report_disable_timing命令查看直接指定失效的时序弧,如图5或图6所示,从图6的Flag栏的u可以看出,此时的失效路径是直接由用户定义的。此时的时序分析结果如图7和图8所示。

set_disable_timing [get_cell U4] -from B -to Y

set_disable_timing [get_cell U4] -from S0 -to Y //加上这句也可以

图5 失效时序弧报告(一)

图6 失效时序弧报告(二)

图7 发射时钟和捕获时钟都是clk_2

图8 发射时钟和捕获时钟都是clk_2

对于使用set_disable_timing命令,使得数据选择器U4从输入引脚A到输出引脚Y的时序弧失效,与上面是一样的操作和结果。

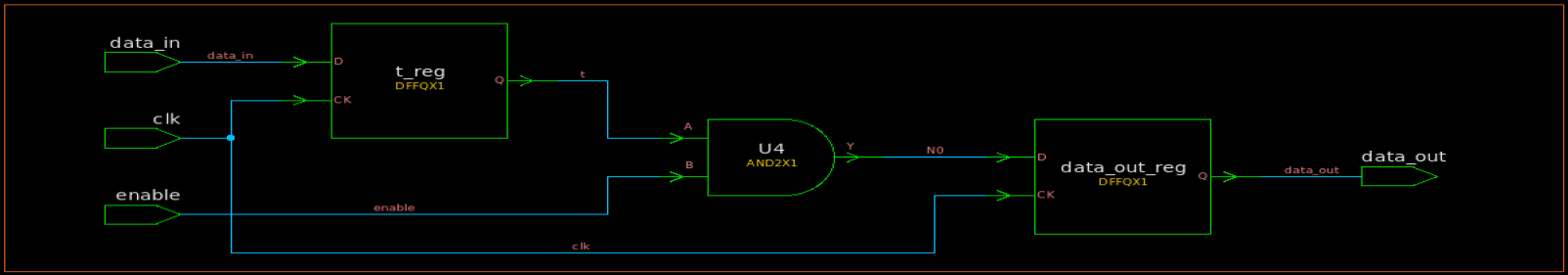

在讨论set_case_analysis命令时,我们说到固定值会随着逻辑传播,直到不能将固定值传播下去为止。那set_disable_timing命令是否也会导致失效时序弧沿着逻辑传播?下面来看一个例子,如图9所示。

图9 一个简单的例子

首先在输入端口clk定义一个时钟,并对输入端口enable添加输入延迟约束。

create_clock -period 10 [get_port clk]

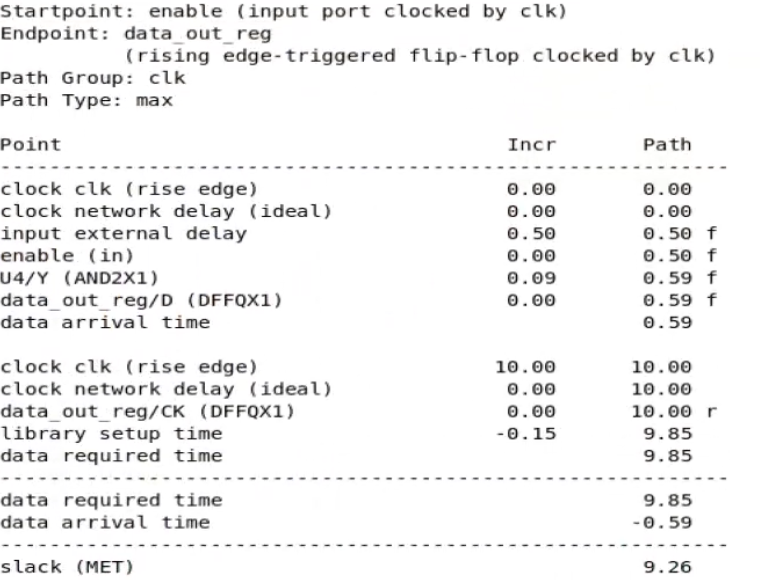

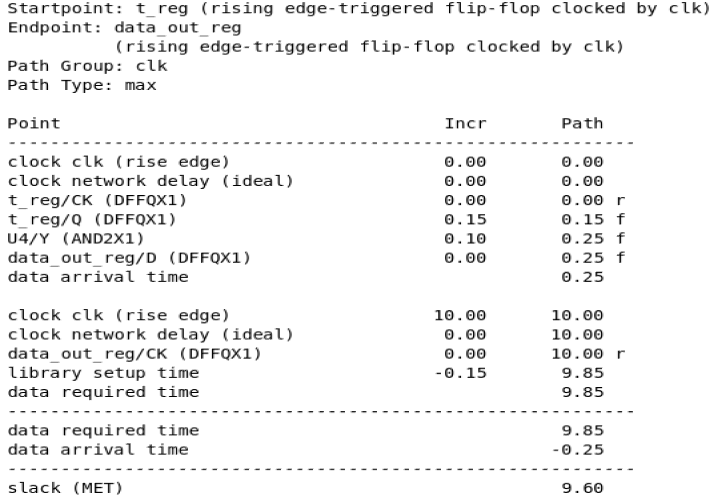

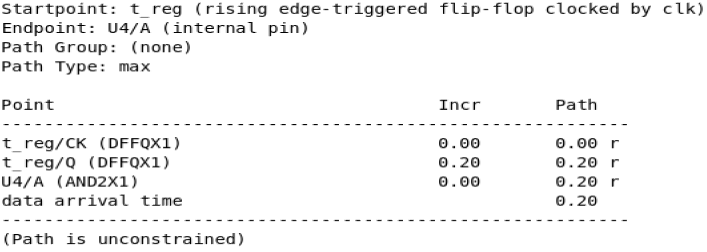

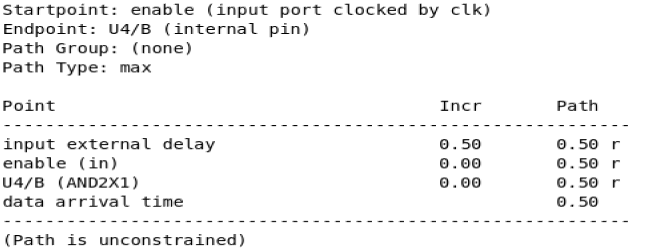

set_input_delay 0.5 -clock clk [get_port enable]此时如果直接使用report_timing命令,则t_reg和data_out_reg以及端口enable和data_out_reg之间的时序路径会正常报告,如图10和图11所示。

图10 两个触发器间的时序报告

图11 端口和触发器间的时序报告

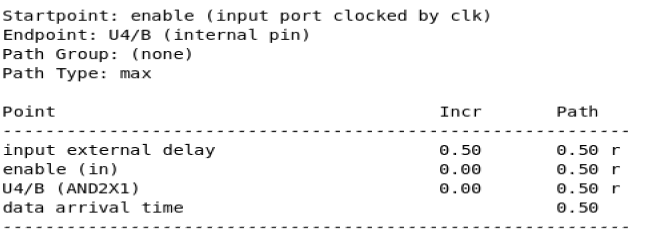

下面使用set_disable_timing命令使与门U4从输入引脚B到输出引脚Y的时序弧失效,可以使用report_design命令或report_disable_timing命令查看直接指定失效的时序弧,如图12或图13所示,可以看出,失效时序弧不会沿着逻辑传播。

set_disable_timing [get_cell U4] -from B -to Y

图12 失效时序弧报告(一)

图13 失效时序弧报告(二)

下面我们来看set_disable_timing命令的一个特性:时序路径分割,这与set_case_analysis命令直接使时序路径消失不同,下面来看一个例子。

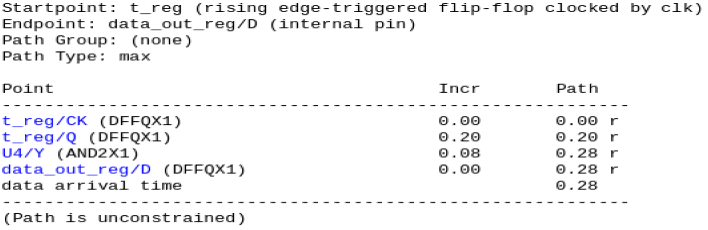

由于在图9中,我们只使与门U4从输入引脚B到输出引脚Y的时序弧失效了,而与门U4从输入引脚A到输出引脚Y的时序弧依然保留了,所以t_reg和data_out_reg的时序路径依旧存在,如图14所示。

图10 两个触发器间的时序报告

但是原本在输入端口enable到触发器data_out_reg之间的时序路径被切断了,此时的时序路径变成了从输入端口enable到与门U4的B引脚(尽管这不是一个常见的时序路径终点,但现在确实如此),如图11所示,而此时与门U4的Y引脚到触发器data_out_reg输入引脚D的时序弧只属于t_reg到data_out_reg的时序路径。

图11 一条奇怪的时序路径

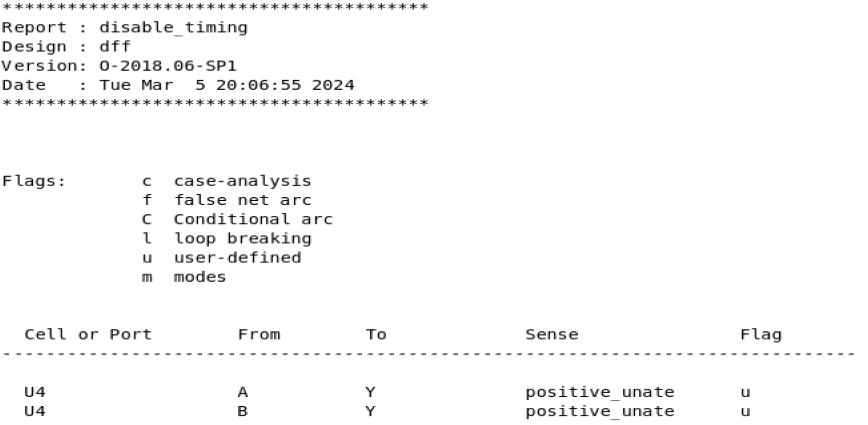

如果此时使用下面的命令,再使与门U4从输入引脚A到输出引脚Y的时序弧失效,如图12所示则这把之前的两条时序路径都切断,此时会出现三条时序路径,第一条是从t_reg到与门U4的A引脚,第二条是从输入端口enable到与门U4的B引脚,第三条是从与门U4的Y引脚到触发器data_out_reg,如图13、图14和图15所示,从图中的startpoint和endpoint可以看出时序路径的起点和终点。

set_disable_timing [get_cell U4] -from A -to Y

图12 失效时序弧报告

图13 第一条时序路径

图14 第二条时序路径

图15 第三条时序路径

我们可以使用-restore选项移除两个指定的失效时序弧,顺带一提,还可以使用remove_disable_timing命令移除失效时序弧,它们是等价的。

set_disable_timing [get_cell U4] -from A -to Y -restore

set_disable_timing [get_cell U4] -from B -to Y -restore//下面的命令等价

remove_disable_timing [get_cell U4] -from A -to Y -restore

remove_disable_timing [get_cell U4] -from B -to Y -restore如果我们直接指定触发器data_out_reg的时钟引脚CK到数据引脚D的时序弧失效,则针对data_out_reg的建立时间和保持时间检查都不会进行,如图16所示。

图16 建立时间和保持时间不会检查

写在最后

set_disable_timing命令能直接指定一条时序弧失效,并中断并分割经过它的时序路径,在实际运用中,使用此命令前需要谨慎,并明确自己在做什么。

这篇关于静态时序分析:SDC约束命令set_disable_timing详解的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!