timing专题

芯片后端之 PT 使用 report_timing 产生报告 之 常用命令

滴水穿石,坚持加持~ pt_shell> report_timing -from <startpoint> -to <endponit> -delay max/min pt_shell> report_timing -from <startpoint> -to <endponit> -delay max/min -nosplit pt_shell> get_cells *data_re

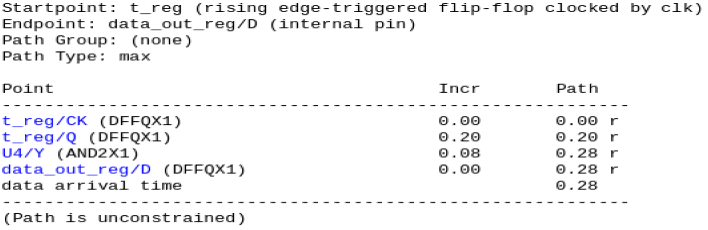

芯片后端之 PT 使用 report_timing 产生报告如何阅读

今天,就PT常用的命令,做一个介绍,希望对大家以后的工作,起到帮助作用。 在PrimeTime中,使用report_timing -delay max命令生成此报告。switch -delay max表示定时报告用于设置(这是默认值)。 首先,我们整体看一下通过report_timing 运行之后,报告产生的整体样式。 pt_shell> report_timing -from start_

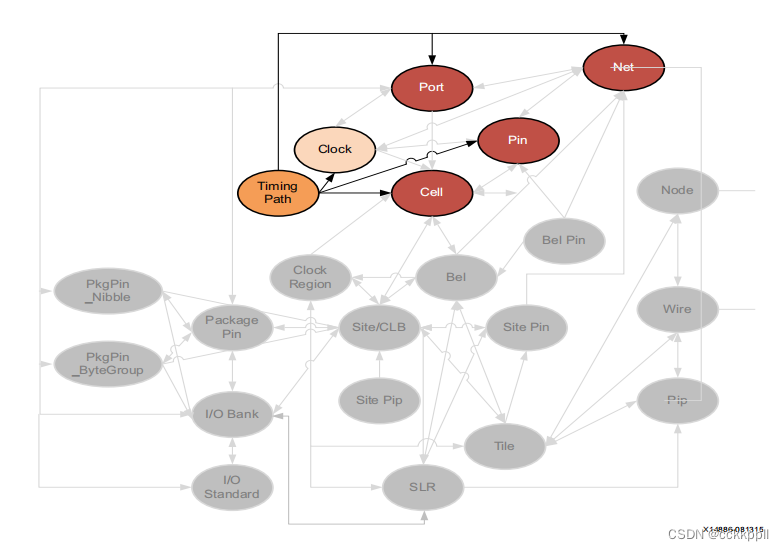

vivado TIMING_PATH

描述 定时路径由设计元素之间的连接来定义。在数字中 在设计中,时序路径是由一对受其控制的顺序元件形成的 或者通过两个不同的时钟来启动和捕获信号。 在典型的定时路径中,数据在一个内的两个连续单元之间传输 时钟周期。例如,启动边缘发生在时间0ns;并且出现捕获边缘 一个时钟周期之后。 最常见的定时路径是: •从输入端口到内部顺序单元的路径 •从一个顺序单元到另一个顺序单元格的内部路径 •从内部顺序单元

set_disable_timing和set_data_check,相关一条efuse时序违反路径的梳理。

因为efuse端口,都是异步,没有时钟。端口之间需要保证时序关系,这是由RTL设计保证的,时序无法分析相关efuse路径。set_disable_timing一般是要求一个lib cell,例如set_disable_timing -from cell.输入 -to cell.输出。datacheck,类似AEN当时钟,RDEN当数据,两个数据信号检查setup路径时序。如果report_ti

set_false_path 与 set_disable_timing 的区别

在静态时序分析中, set_false_path 和 set_disable_timing 都可以用来设置 timing exceptions,告诉工具忽略某些特定的path,但是在使用过程中,这两个命令又有些细微的区别。 set_false_path 是用来设置 timing path,表示不用 check 这些 path 的 timing,但是依然会去计算这些 path 上的delay s

时间轮片(Timing Wheel)实现心跳机制

在使用长连接的时候,我们通常需要使用心跳机制来防止意外断开的无效连接浪费系统资源。 心跳机制的实现常用的有两种: 第一:每一个客户端连接上时,就创建一个定时器,如果在指定时间内没有收到客户端发来的心跳,那么该定时器就将连接断开。如果收到,则重置定时器,重新计时。 但是在连接数量上万,甚至数十万百万时,定时器的数量也将有数十万甚至百万个,极大的耗费系统资源,甚至拖垮整个系统,因此这种方式适用于

PostgreSQL自带的命令行工具14- pg_test_timing

PostgreSQL自带的命令行工具14- pg_test_timing 基础信息OS版本:Red Hat Enterprise Linux Server release 7.9 (Maipo)DB版本:16.2pg软件目录:/home/pg16/softpg数据目录:/home/pg16/data端口:5777 pg_test_timing 是 PostgresSQL 包含的一个

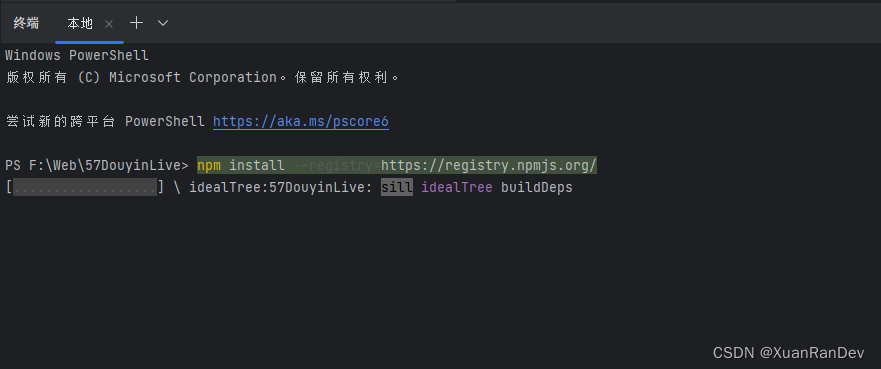

npm install 卡在reify:rxjs: timing reifyNode的解决办法

今天要逆向跑一个electron,但是npm install一直卡在 reify:element-plus: timing reifyNode:node_modules/lodash Completed in 6664ms 这里一动不动,一番研究之后发现可能跟用的镜像有关系,我原本是官方镜像,总感觉第三方镜像有一些莫名的问题,然后之前迫不得已换到淘宝镜像,最后从淘宝镜像切换到官方就好了。

【Xilinx】时序约束学习 TIMING-1: 时钟修改块上的时钟波形无效

在 <cell_type> 输出 <pin_name> 上指定的时钟 <clock_name> 的时钟波形无效, 与时钟修改块 (CMB) 设置不匹配。该时钟波形为 <VALUE>。期望的波形为 <VALUE>。 描述 Vivado Design Suite 会根据 CMB 设置和传入主时钟的特性, 在 CMB 输出上自动衍生时钟。如果用户在 CMB 输出上

1.0.6 js window对象(window,location,screen,history,popupAlert,timing,cookie)

<!DOCTYPE html> <html encoding="gbk"> <head> <meta http-equiv="Content-Type" content="text/html;charset=utf-8"></meta> <script> //js widnow对象 function windowMethod(){ //该例显示浏览器窗口的高度和宽度:(不

一寸Timing一寸金,寸金能买寸光阴——CCD

上次我们简单介绍了一下CTS里面的一些基本概念,随着工艺尺寸的越来越先进,现在大家都热衷于都流行采用useful skew去修timing。 传统的balance的clock tree已经不怎么受待见。提到useful skew,就有必要介绍一下CCD,全称是Concurrent Clock Datapath,并行优化clock和data path。这对习惯于以前传统CTS做法的童鞋来说是一个

每天学命令report_cell_instance_timing

report_cell_instance_timing list_of_cell_instances [-clock_timing] [-early | -late] [{> | >>} filename | -tcl_list] 这个命令可以报出一个instance上所有的pin的timing arc以及delay信息,使用该命令前必须先运行report_timing,会生成三张表格

两点天上来,爱情一线牵——Global Timing Debugger

今天我们来介绍一下时序分析的小工具——Global Timing Debugger(简称GTD)。 它是Innovus/ Encounter中分析Data Path的工具, 和Clock Tree Debugger有众多相似的地方。 顾名思义, Global Timing Debugger就是用来debug timing。对于一些新人来说, 可能看懂和分析timing report是一件很困难

静态时序分析:SDC约束命令set_disable_timing详解

静态时序分析https://blog.csdn.net/weixin_45791458/category_12567571.html 目录 指定对象列表 指定源、目的引脚 指定恢复 简单使用 写在最后 上一章中,我们学习了如何使用set_case_analysis模式分析命令,它通过指定某个端口或引脚为固定值,从而使设计中的一些时序弧失效。本章将学习set_d

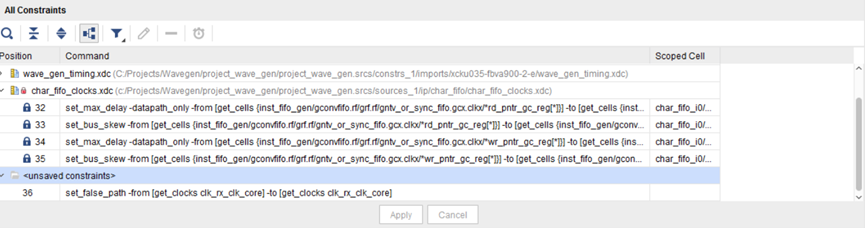

开发者分享|读懂用好 Timing Constraints 窗口

本文作者:赛灵思工程师 Grace Sun 随着设计复杂度和调用 IP 丰富度的增加,在调试时序约束的过程中,用户常常会对除了顶层约束外所涉及的繁杂的时序约束感到困惑而无从下手。举个例子,用户在 XDC 里面并没有指定 set_false_path,为什么有些路径在分析时忽略了?那怎么去定位这些约束是哪里设定的? 事实上,Vivado 集成设计环境提供了很多辅助工具来协助用户完成时序约束的分析。

[NAND Flash 7.1] 闪存系统性能优化方向集锦?AC timing? Cache? 多路并发?

依公知及经验整理,原创保护,禁止转载。 专栏 《深入理解NAND Flash》 <<<< 返回总目录 <<<< 传送门 >>> 总目录 主页: 元存储的博客_CSDN博客 依公开知识及经验整理,如有误请留言。 个人辛苦整理,付费内容,禁止转载。 内容摘要 优化 AC Timing,提升总线频率 1.1 优化 AC Timing 1.2 优化总线频率 使用 Cache R

FPGA时序分析与时序约束(五)——使用Timing Analyzer进行时序分析与约束

Quartus的安装路径下会自带有例程,通过fir_filter进行学习如何使用Timing Analyzer进行时序分析与约束。 1.1 创建时序网表 打开fir_filter并进行综合后可通过菜单栏Tool->Timing Analyzer或工具栏按钮运行Timing Analyzer。 根据前面提到的,时序分析工具需要网表来执行时

时序例外_Timing Exceptions_False Paths(set_false_path)

今天拿到一个别人的工程,布局布线后发现有16个Critical Warning,在生成bit文件时,vivado卡死在布线步骤,说明时序是有问题的。打开综合后的时序报告,发现保持时间Slack为-18ns,而且都是保持时间违例,建立时间没有问题。通过对具体的违例线路分析,发现大部分都是异步fifo读写数据路径违例(如下图所示),最终通过set_false_path解决了问题。所以对false pa

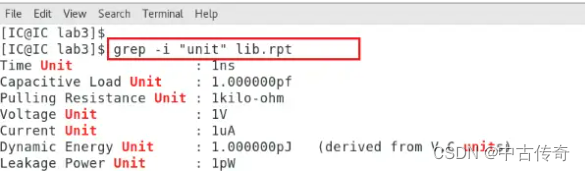

【DC系列教程2--Timing and Area Constrains】

DC系列教程2--Timing and Area Constrains Lab Flow:依赖输入Design SpecificationLab Demo Goal: determin the unit of time in the target library; //设置时间精度Create a Design Compiler timing and area constra

vivado set_disable_timing

禁用定时电弧 可以使用set_disable_timing命令禁用单元内的计时弧。只有可以禁用从单元的输入端口到输出端口的定时弧。注意:set_disable_timing命令也可用于从端口或导线禁用定时弧。在这种情况下,不使用命令行选项-from和-to,只使用端口对象或定时指定圆弧对象。计时器会自动禁用某些定时弧,以处理特定情况。例如,不推荐组合反馈回路,并且不能正确地定时。计时器通过禁用循

DC report_timing 报告分析(STA)

每一个path都有专属的slack,slack值可以是正,0或者负。某一个path拥有最坏的slack的话则称之为 critical path critical path拥有最大的负slack值。若是所有的path都没有时序违规,则slack都是正数,此时最小的那个slack则是critical path。 负数critical paths意味着某一组的path都是critical path。

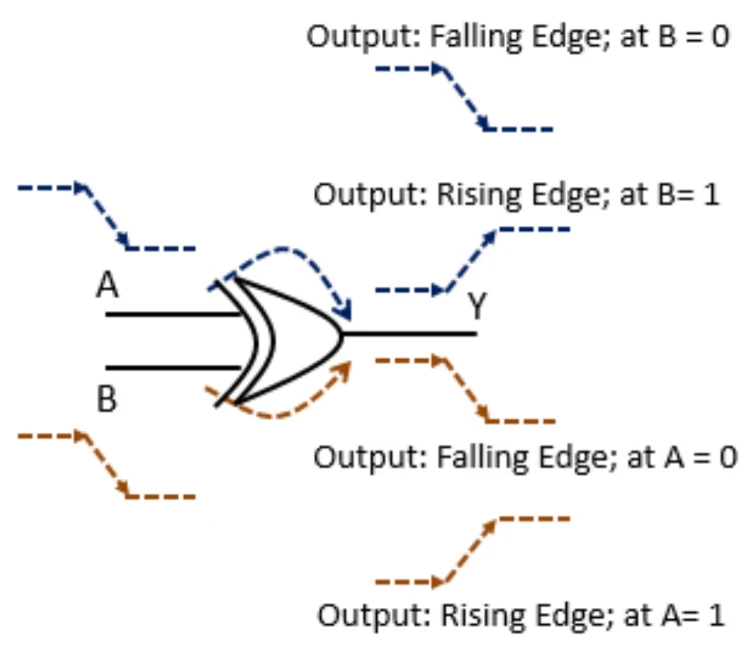

FPGA设计时序分析概念之Timing Arc

目录 1.1 Timing Arc概念 1.2 Timing Arcs的类型 1.3 Timing Sense(时序感知) 1.4 参考资料 1.1 Timing Arc概念 在时序工具对设计进行时序分析时,经常会看到一个概念Timing Arch(时序弧)。Timing Arc是一个信号一个单元Cell的输入引脚Pin到该单元输出引脚Output Pin间的路径。对于

FPGA设计时序分析概念之Timing Arc

目录 1.1 Timing Arc概念 1.2 Timing Arcs的类型 1.3 Timing Sense(时序感知) 1.4 参考资料 1.1 Timing Arc概念 在时序工具对设计进行时序分析时,经常会看到一个概念Timing Arch(时序弧)。Timing Arc是一个信号一个单元Cell的输入引脚Pin到该单元输出引脚Output Pin间的路径。对于

JavaScript Timing 事件(定时器)

JavaScript Timing 事件 1、setTimeout() 方法setTimeout() 方法如何停止执行?2、setInterval() 方法setInterval() 方法如何停止执行? JavaScript 可以在时间间隔内执行。 这就是所谓的定时事件( Timing Events)。 定时器方法如下 方法说明setTimeout()在指定的毫秒数后调用