本文主要是介绍一寸Timing一寸金,寸金能买寸光阴——CCD,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

上次我们简单介绍了一下CTS里面的一些基本概念,随着工艺尺寸的越来越先进,现在大家都热衷于都流行采用useful skew去修timing。 传统的balance的clock tree已经不怎么受待见。提到useful skew,就有必要介绍一下CCD,全称是Concurrent Clock Datapath,并行优化clock和data path。这对习惯于以前传统CTS做法的童鞋来说是一个全新的概念,有很多不同的地方。下面我简单介绍一下这种新技术的概念,希望大家看完能了解它为什么叫做Concurrent Clock Datapath吧~

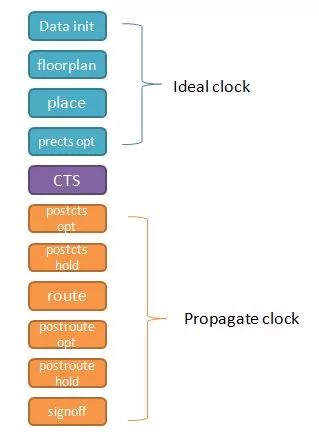

我们知道clock的Timing分为两种模式,ideal clock和propagated clock。CTS之前并没有clock, 因此我们需要建立一个ideal的clock,这时从clock端口到寄存器CK端口的network delay来自sdc中的set_clock_latency设置;做完CTS,并且update好IO latency之后,我们的clock就会自动的转换成propagated的clock,这时network delay就是实际时钟互连线网络的RC extraction算出来的delay。

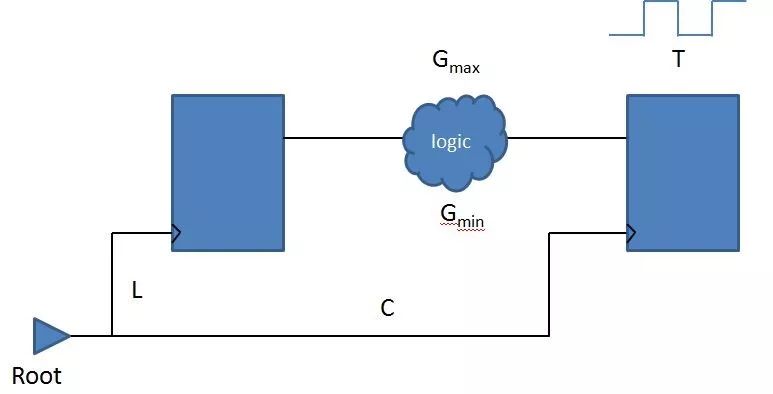

在一个实际设计中,clock起始于ideal模式,并以propagated模式结束。如下图所示:

对传统的flop to flop之间的电路,setup和hold time需要满足以下两个条件,如下图所示:

L和C分别代表Launch和Capture clock path上的delay. Gmax和Gmin代表logic path上的最大和最小delay. 对ideal clock来说,它假定launch和capture clock path上有相同的delay,也就是L=C,这时,上诉两个公式就简化成:

Propagated clock

setup: L+ Gmax < T + C

hold: L+ Gmin > C

Ideal clock

setup: Gmax < T

hold: Gmin > 0

这样问题就变得很简单,Gmin>0是一个永远成立的条件,在这个model下面,我们只需要保证logic path上的最大delay,也就是critical path上的delay比时钟周期快就行。根据这个条件,于是就出现了,传统CTS的目的是使得时钟树的L=C,如果能实现,那么propagated clock timing就会匹配ideal clock timing。

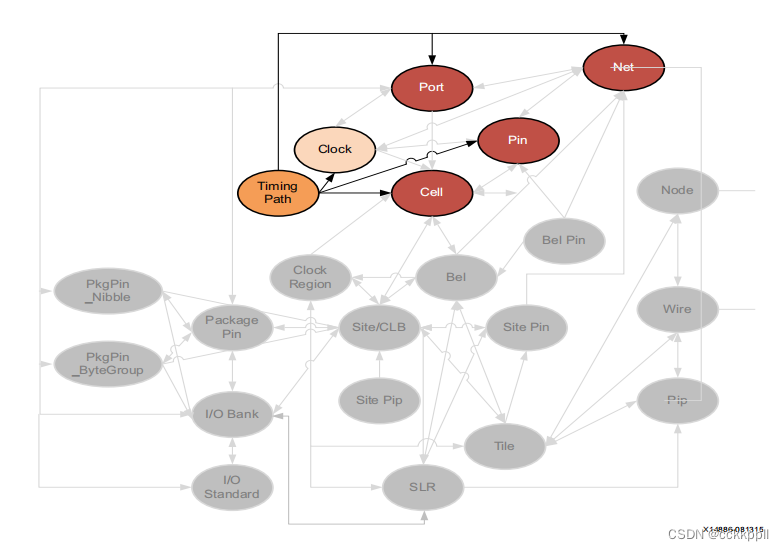

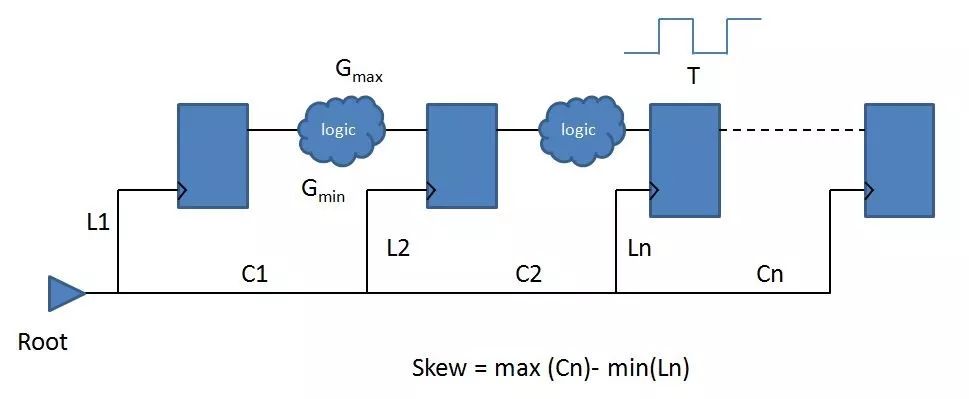

当一个时钟树有n个sink以后,我们就需要引入"skew"的概念。如下图所示:

在引入skew概念后,完全balance的时钟树就很难做成,clock skew变成各个flop之间的Launch和capture clock path的最大差值。

Propagated clock

setup: Gmax < T - (L-C)

hold: Gmin > C - L

Ideal clock

setup: Gmax< T + skew

hold: Gmin > skew

因此,传统的CTS目标就是减小clock skew。如果能实现较小的skew,那么ideal和propagated clock就能保持一个较高的相似度。

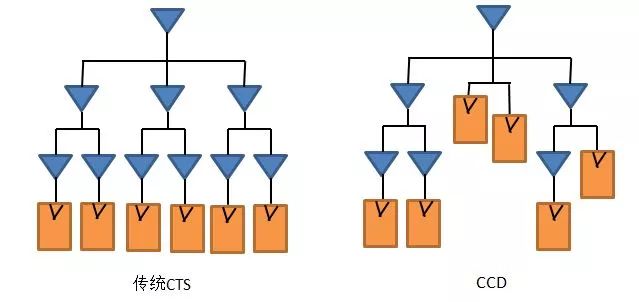

那究竟skew是不是越小越好呢?这个我觉得是case by case的问题。但是,通过减小clock skew来实现ideal和propagated clock收敛的做法已经不适合现在深纳米的设计了。由于OCV, clock gating, 以及clock的复杂性等因素导致两者之间有很大的clock timing gap,实现balanced的L和C几乎变成一个不可能的目标。而CCD就放弃了这种减小clock skew的方法,而是将CTS和postCTS的timing optimize集合为一体,在优化data path的同时进行clock path的优化。根据timing情况自动调整时钟树各点的延迟,以达到合理利用skew来优化timing的目的。

下图显示了传统CTS与CCD两种不同的概念原理。正如我们前文所说,传统CTS以减小skew作为目标,在build clock tree的过程中忽略掉了data path。而CCD的clock tree建立在data path的timing基础上,在propagated timing中,以meet setup和hold timing为主。

当然,虽然CCD和传统CTS的工作原理不一样,但他们的使用流程是一样的。分为以下三部曲。

在传统的CTS中,

第一阶段:clock_opt -to build_clock,主要在生长时钟树,并且做inter clock的balance,目的是为了减小skew。

第二阶段:clock_opt -from route_clock -to route_clock,主要是连接clock net,并且update io latency。

第三阶段:clock_opt -from final_opto,主要是做data path的optimization来修复timing。

而在CCD的flow中,命令一样,但我们首先必须设置以下参数来enable flow

set_app_options -name clock_opt.flow.enable_ccd \

-value true

但CCD flow的三个阶段做的事情与传统CTS flow有所区别。

第一阶段:主要也是在生长时钟树,并且做inter clock的balance,但目的是为了提高setup和hold的timing。

第二阶段:这个阶段做的事情一样,主要是连接clock net,并且update io latency。

第三阶段:这个阶段区别最大,主要是同时优化data path和clock path来修复timing。

CCD与传统CTS的区别介绍就到这了,下次介绍更多相关useful skew的内容,敬请期待~~

各大IC公司招聘各类IC工程师

简历请戳邮箱:taozhang3260@163.com

这篇关于一寸Timing一寸金,寸金能买寸光阴——CCD的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!