本文主要是介绍【DC系列教程2--Timing and Area Constrains】,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

DC系列教程2--Timing and Area Constrains

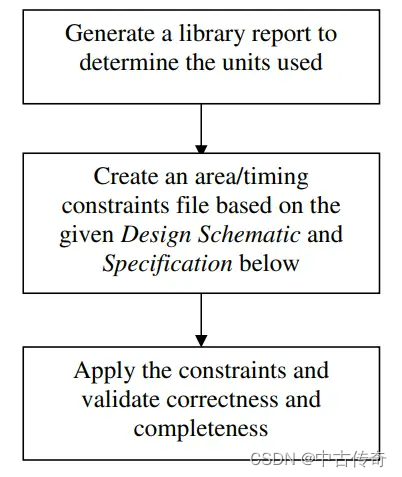

- Lab Flow:

- 依赖输入

- Design Specification

- Lab Demo

Goal:

- determin the unit of time in the target library; //设置时间精度

- Create a Design Compiler timing and area constrains file based on a provided schematic and specifacation //自己写时序和面积约束文件根据给定原理图

- Verify the syntax of the constrains prior to applying them to a design.

- Apply the constraints to a design. //约束应用于设计

- Validate the completeness and correctness of the applied constrains.

Lab Flow:

依赖输入

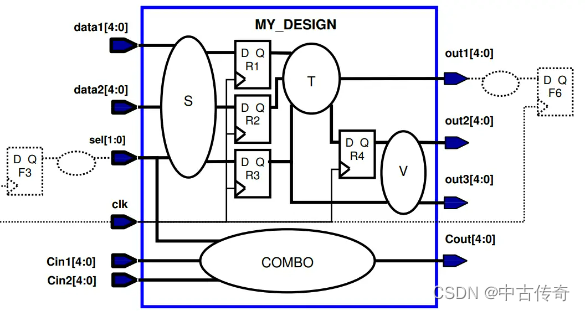

RTL(Design Schematic)

Design Specification

Design Schematic:设计框图,可以tool bar里面点击生成;

形如下图,其实类似在Design Spec里面自己画的模块框图是的,这个更细点带着布尔门和寄存器;

Design Specification

详细设计规格具体要求:

Clock Definition

Register Setup Time

Input Ports(sequential logic)

Combinational Logic

Design Area

Lab Demo

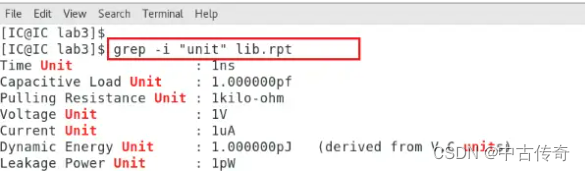

1.Setup for the .synopsys_dc.setup

read_db sc_max.db // read_db <targent_library_file>

list_libs //check for libs

report_lib cb13fs120_tsmc_max // if want to redirect,use below

redirect -file lib.rpt {report_lib cb13fs120_tsmc_max}

exit // for exit dc_shell

gvim lib.rpt

grep -i “unit” lib.rpt

2.Create a Timing and Area Constrains File

If do not know how to do ,ref the .solutions.

- create xxx.con under ./scripts/

touch lab4.con

- Based on the Design Spec and Design Schematic,as well as the appropriate time unit,Get the required constrains writed in lab4.con

#Dont know how to write

cp .solutions/lab4.con ./scripts

de_shell: source scripts/lab4.con

- check for verify the constrains applied to design

check_timing

report_clock

report_clock -skew

report_port -verbose

- write out the applied constrains to a file for further checking

write_script -out scripts/lab4.wscr

- tkdiff cmd to compare the .solutions/lab4.wscr with scripts/lab4.wscr

save the design as unmapped/MY_DESIGN.ddc and exit.

GuI: saved as..

unix: write -hierarchy -format ddc -output /xx/xxx/xx/xx/xx/xx.ddc

【Ref】

[1] https://blog.csdn.net/weixin_44726874/article/details/131088674

[2] https://max.book118.com/html/2016/1113/62845423.shtm

这篇关于【DC系列教程2--Timing and Area Constrains】的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!