dsp专题

构建智慧桥梁--程易科技DSP知识管理系统

在当今这个信息爆炸的时代,企业的核心竞争力往往来源于对知识的有效管理和利用。程易科技,作为一家致力于为企业提供全方位数字化解决方案的服务商,深刻认识到这一点。为此,公司推出了基于其自主研发的DSP(Digital Service Platform)数字化服务平台的知识管理系统,旨在帮助企业构建一个集知识文档管理、在线问答等功能于一体的高效知识管理体系。 DSP数字化服务平台简介 ·平台背景:程

TI DSP TMS320F280025 Note9:GPIO输入输出与外部中断功能原理与应用

TMS320F280025 GPIO输入输出与外部中断功能原理与应用 文章目录 TMS320F280025 GPIO输入输出与外部中断功能原理与应用GPIO原理输入输出模式的共同特性1. 复用设置2. 内部上拉设置3. GPIO状态读取 对于输出模式输出电平设置开漏输出设置 对于输入模式极性设置采样类型不同步(异步输入)只同步到SYSCLKOUT使用采样窗口进行鉴定 外部输入中断G

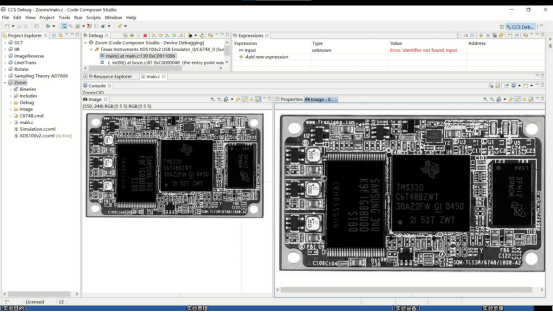

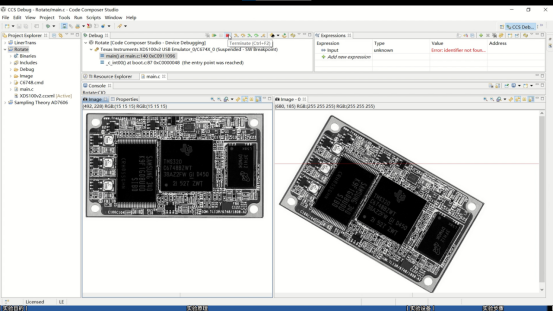

【DSP+FPGA】基于DSP+FPGA XC7K325T与TMS320C6678的通用信号处理平台

DSP + FPGA 协同处理架构板载 1 个TMS320C6678 多核DSP处理节点板载 1 片 XC7K325T FPGA处理节点板载 1 个FMC 接口板载4路SFP+光纤接口FPGA 与 DSP 之间采用高速Rapid IO互联 基于FPGA与DSP协同处理架构的通用高性能实时信号处理平台,该平台采用1片TI的KeyStone系列多核浮点/定点DSP TMS320C6678作为主处

【DSP+FPGA】基于2 个TMS320C6678+ XC7VX690T FPGA 的6U VPX 总线架构的高性能实时信号处理平台

6U VPX架构,符合VITA46规范板载 2 个TMS320C6678 多核DSP处理节点板载 1 片 XC7VX690T FPGA处理节点板载 2 个FMC 接口背板之间具有 4 路 x4 高速 GTH 互联,支持RapidIO、PCI ExpressFPGA 与 DSP 之间采用高速Rapid IO互联 基于6U VPX架构的高性能实时信号处理平台,该平台采用2片TI的KeyStone

使用/dev/dsp的wav文件播放器源码

转载于:http://blog.csdn.net/dux003/article/details/5459423 #include #include #include #include #include void usage(const char* self) { printf("usage:/n"); printf("/t%s [-c channels

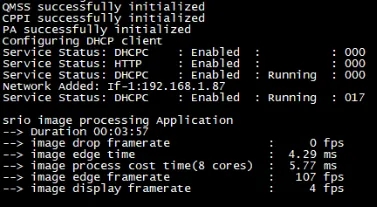

DSP C6000教学实验箱操作教程_数字图像处理:5-3 图像缩放

一、实验目的 学习图像缩放的原理,掌握图像的读取方法,并实现图像缩放。 二、实验原理 图像缩放 在计算机图像处理和计算机图形学中,图像缩放是指对数字图像的大小进行调整的过程。图像缩放是一种非平滑的过程,需要在处理效率以及结果的平滑度和清晰度上做一个权衡。当一个图像的大小增加之后,组成图像的像素的可见度将会变得更高,从而使得图像表现得“软”。相反地,缩小一个图像将会增强它的平滑度和清晰度。

DSP 中数字下变频的基础知识

本文讨论数字下变频,这是一种广泛用于数字无线电接收器的数字信号处理技术。 数字下变频是一种数字信号处理技术,广泛用于数字无线电接收机。本文将回顾数字下变频器 (DDC) 的基础知识。我们将首先了解使用 DDC 而不是模拟对应物的优势。然后,我们将讨论一个示例并探索 DDC 的基本操作。 要了解使用 DDC 的优势,让我们首先回顾一下传统的双下变频接收器并检查其缺点。基本的双下变频接收器如图 1

解锁全球增长潜力:Flat Ads DSP助您触达全球,高效增长!

在当今数字化营销的时代,广告主们面临着前所未有的挑战和机遇。如何精准触达目标用户,如何最大化广告效果,如何在全球市场中实现快速增长,这些都是广告主面临的考验。作为全球领先的移动广告营销平台,Flat Ads拥有自研的DSP平台,为广告主们提供了高效、精准、智能的一站式营销解决方案。 DSP(Demand Side Platform:需求方平台)是采买流量的广告投放平台,允许广告主通过程序

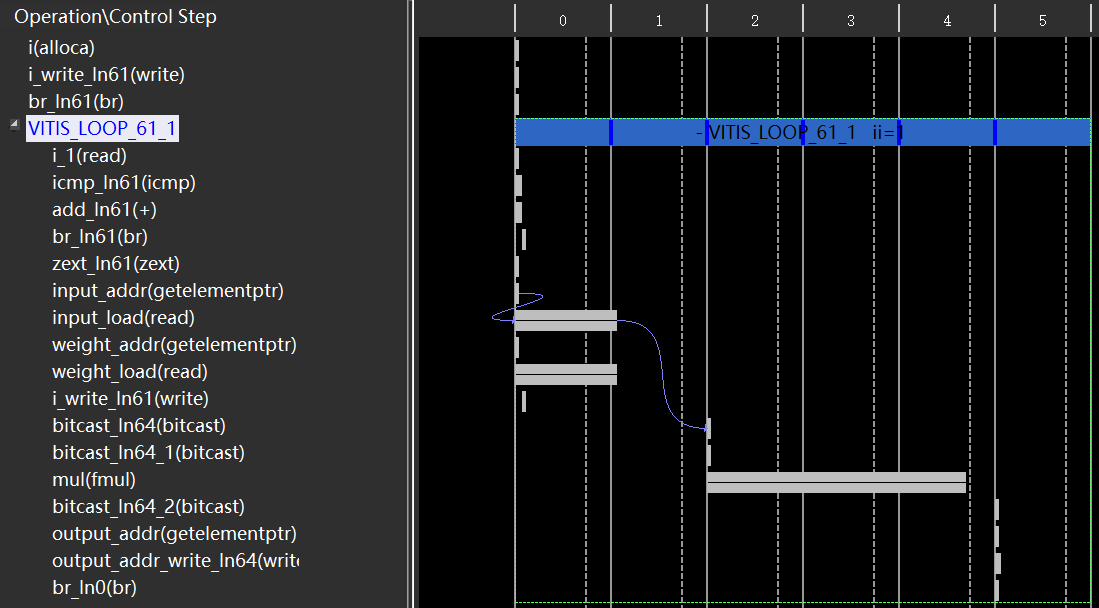

基于 Vitis HLS 的单个乘法 DSP 映射研究

文章目录 1 自媒体账号2 引言3 整数乘法4 定点乘法5 浮点乘法6 总结 1 自媒体账号 目前运营的自媒体账号如下: 哔哩哔哩 【雪天鱼】: 雪天鱼个人主页-bilibili.com 如果觉得有所收获的话,可以点击我的主页 -> 充电 -> 自定义充电 支持一下,十分感谢! 微信公众号 【雪天鱼】 CSDN 【雪天鱼】: 雪天鱼-CSDN博客 QQ 学习交流群

斯坦福SR810和SR830 DSP锁定放大器

SR810 和 SR830 DSP 锁定放大器 SR810 锁定放大器和 SR830锁定放大器以合理的成本提供高性能。SR830 同时显示信号的幅度和相位,而 SR810 仅显示幅度。两种仪器都使用数字信号处理 (DSP) 来代替传统锁定中的解调器、输出滤波器和放大器。SR810 和 SR830 具有 1 mHz 至 102 kHz 的工作范围和 100 dB 的无漂移动态储备,提供无与伦比的性

001 TI的DSP跑OS

TI公司常用的DSP芯片可以归纳为三大系列: TMS320C2000系列,称为DSP控制器,集成了flash存储器、高速A/D转换器以及可靠的CAN模块及数字马达控制的外围模块,适用于三相电动机、变频器等高速实时工控产品等需要数字化的控制领域。 TMS320C5000系列,这是16位定点DSP。主要用于通信领域,如IP电话机和IP电话关、数字式助听器、便携式声音/数据/视频产品、调制解调器、

DSP教学实验箱_数字图像处理_操作教程:5-1 图像旋转

一、实验目的 学习图像旋转的原理,掌握图像的读取方法,并实现图像旋转。 二、实验原理 图像旋转 图像的旋转是指以图像的某一点为原点以逆时针或顺时针旋转一定的角度。其本质是以图像的中心为原点,将图像上的所有像素都旋转一个相同的角度。和图像平移一样,图像旋转也是图像的位置变换,对于旋转后超出源图像范围的区域要处理为不显示。 旋转后的图像不会变形,但是其垂直对称轴和水平对称轴都发生了变化,旋转

模块[camera]_ISP与DSP的区别

ISP 是Image Signal Processor 的简称,也就是图像信号处理器。而DSP是Digital Signal Processor 的缩写,也就是数字信号处理器。 ISP一般用来处理Image Sensor(图像传感器)的输出数据,如做AEC(自动曝光控制)、AGC(自动增益控制)、AWB(自动白平衡)、色彩校正、Lens Shading、Gamma 校正、祛除坏点、A

DSP问题:TMS320F280049 GPIO输入上拉电压只有2.1V

1、问题现象 使用TMS320F280049编写GPIO输入检测程序时,配置GPIO为输入上拉,使用万用表测量GPIO口只有2.1V左右,程序此时检测到的是低电平,导致无法检测到按钮按下(按钮按下接地)。 2、问题原因 TMS320F280049 GPIO输入上拉是很弱的,所以空闲状态下电压较低。 3、解决方案 在设计电路时需要加上2.1k外部上拉电阻(官方推荐),实际使用10k上拉电阻

怎么建设高性能多核DSP+FPGA实验室?一起来河北工程大学看看

河北工程大学是河北省重点骨干大学,河北省人民政府与水利部共建高校,河北省重点支持的国内一流大学建设高校,河北省文明单位,坐落在中国历史文化名城、“成语典故之都”邯郸市。 学校现有工学、理学、管理学、农学、医学、文学、经济学、法学、艺术学、教育学、历史学11个学科门类。招生专业72个,其中工程类专业47个,占比达65.2%。拥有河北省唯一的服务国家特殊需求博士人才培养项目—水资源水环境调控及综合管

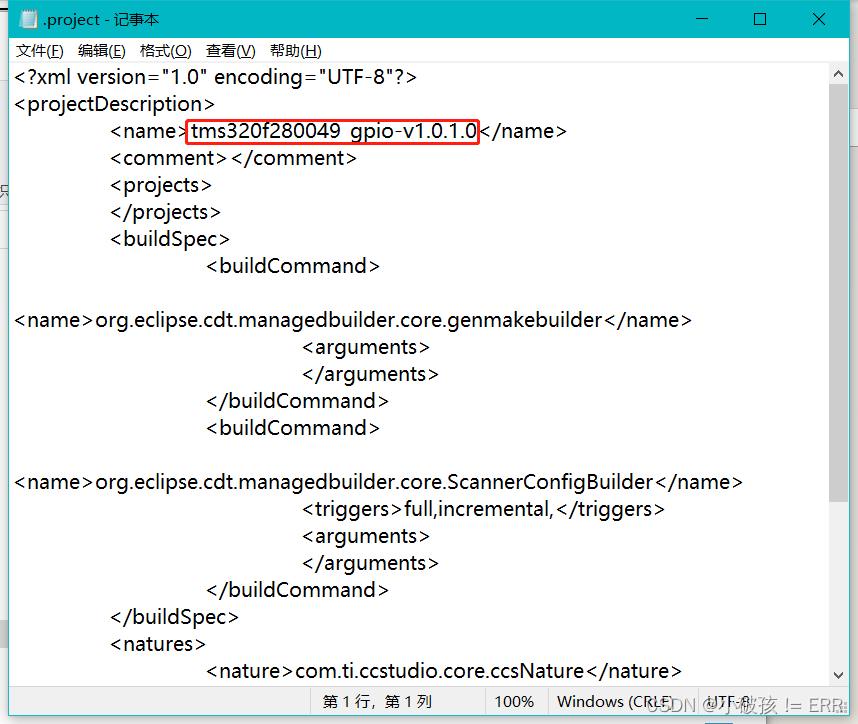

DSP问题:CCS更改工程名导入报错

1、问题现象 复制一个工程出来后,修改版本号,重新导入工程后报错。 显示项目描述无效。 2、问题原因 由于CCS无法通过工程描述中找到指定名字文件夹。使用记事本打开.project文件,里面的描述还是以前的文件夹名,所以导入时报错。 3、解决方案 修改描述和文件夹名称一致即可。

DSP芯片上算法加速技巧总结

#1 将多层或者双层循环改为单层循环。 让循环只形成一个pipeline,充分利用dsp的流水线, #2 使用const关键字限定目标。 C6000编译器如果确定两条指令是不相关的,则安排它们并行执行。 关键字const可以指定一个变量或者一个变量的存储单元保持不变。 这有助于帮助编译器确定指令的不相关性。 #3 使用内联指令_

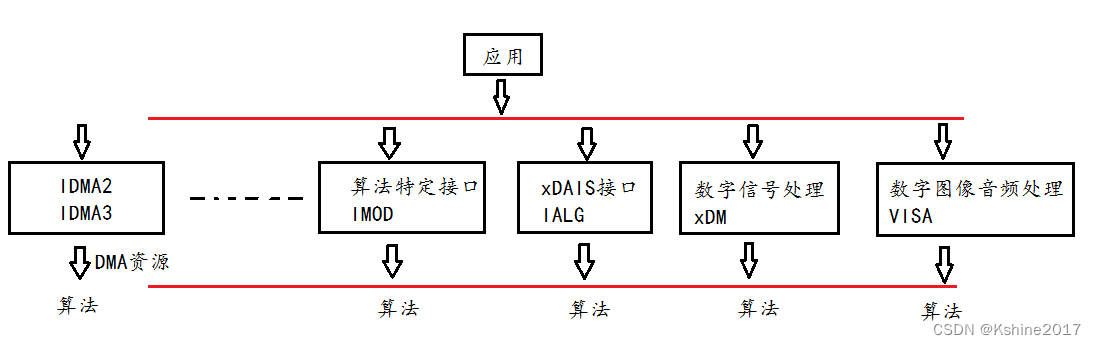

【DSP】xDAIS算法标准

1. 简介 在安装DSP开发支持包时,有名为 “xdais_7_21_01_07”文件夹。xDAIS全称: TMS320 DSP Algorithm Standard(算法标准)。39条规则,15条指南。参考文档。参考文章。 2. 三个层次 3.接口 XDAIS Digital Media。编解码引擎。VISA(Video,Image,Speech,Audio)。 4. 未完待续。

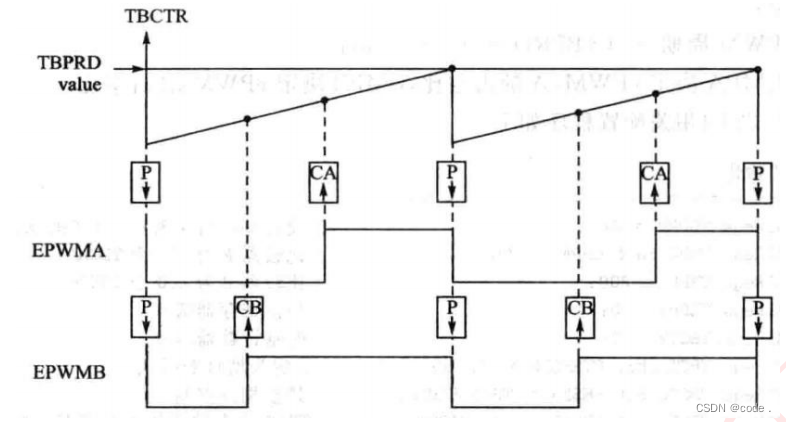

TI_DSP_F2808学习笔记3: ePWM

共有6组ePWM,每一组 ePWM 模块都包含以下 7 个模块:时基模块 TB、计数比较模块 CC、动作模块 AQ、死区产生模块 DB、PWM 斩波模块 PC、错误联防模块 TZ、时间触发模块 ET。 时基模块 TB 确定PWM的周期和相位。 1)PWM 时基计数器(TBCTR) 保存当前的计数值。这里面的值会每个时钟信号(系统时钟源SYSCLKOUT经过分频后的TBCLK)修改一次,是增

dsp、ssp、rtb和dmp

1. DSP(DemandSidePlatform,需求方平台) 商品购买者 2. SSP(Sell-SidePlatform,供应方平台) 商品供货商 3. RTB(RealTimeBidding,实时竞价 商品实时排位 4. DMP(Data-ManagementPlatform,数据管理平台) 竞价排位数据来源

FPGA第二篇,FPGA与CPU GPU APU DSP NPU TPU 之间的关系与区别

简介:首先,FPGA与CPU GPU APU NPU TPU DSP这些不同类型的处理器,可以被统称为"处理器"或者"加速器"。它们在计算机硬件系统中承担着核心的计算和处理任务,可以说是系统的"大脑"和"加速引擎"。这些处理器单元都是计算机系统中的关键组件,它们扮演着不同的角色,为计算机系统提供各种计算和处理能力。 FPGA ~ 第 2 篇 —— FPGA、CPU、GPU、AP

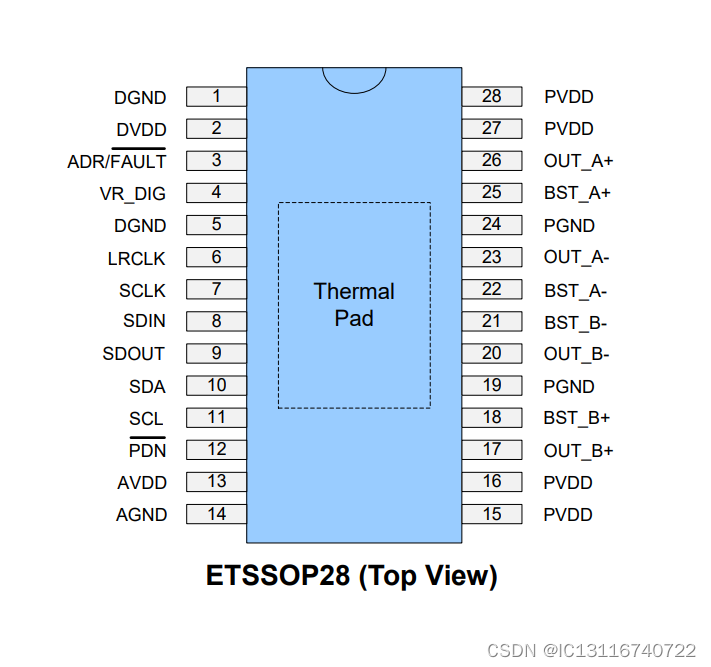

2×24.5W、内置 DSP、低失真、高信噪比、I2S 输入 D 类音频功率放大器,完美替换TPA5805,晶豪,致盛,

ANT3825 是一款高集成度、高效率的双通道数字 输入功放。供电电压范围在 5V~18V,数字接口 电源支持 3.3V 或 1.8V。双通道 BTL 模式下输出 功率可以到 2×24.5W(4Ω,16V,THD+N=1%), 单通道 PBTL 模式下可以输出 37W(4Ω,18V, THD+N=1%)。ANT3825 采用新型 PWM 脉宽 调制架构,根据信号大小动态调整

DSP TMS320C6455 芯片支持库CSL API参考

本文翻译自官方库《C6455_CSL_APIREFERENCE》。 1 CSL介绍 芯片支持库由一系列定义良好的API构成,这些API提取出了Soc设备的细节以便用户可以配置、控制和读写外设,而不用担心寄存器字段级的实现细节。 CSL服务以模块的形式展现。CSL API遵循统一的风格,统一的跨处理器指令集架构,且独立于操作系统,提高了可移植性。 2 CSL概要 CSL有2层实现,基本寄存

自适应信号处理基础及应用——DSP学习笔记五

本专栏的图片内容都来自于老师讲课的PPT,本篇博客只是我个人对于上课内容的知识结构分析和梳理。 导论 自适应系统的定义、特征、形式、举例 特征 非自适应系统 • 固定参数的设计方法 • 假定事先知道了一切可能的输入条件;在这些条件下怎样动作;选择了一个性能准则;进而选择了一个看起来最好的系统 自适应系统 能够自动地适应变化的环境与变化的系统要求 • 能够通过训练改变系统结构

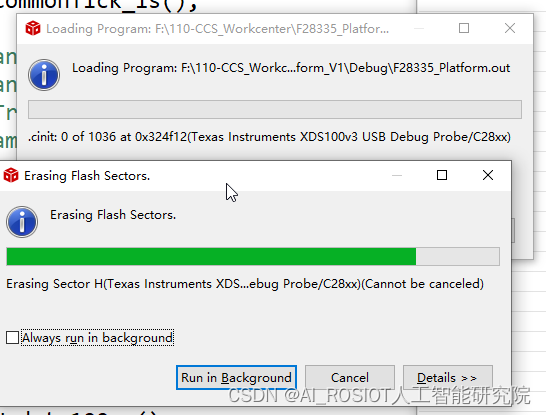

DSP开发实战教程-国产DSP替代进口TI DSP的使用技巧

1.替换CCS安装路径下的Flash.out文件 找到各自CCS的安装路径: D:\ti\ccs1230\ccs\ccs_base\c2000\flashAlgorithms 复制进芯电子国产DSP官网提供的配置文件 下载链接:https://mp.csdn.net/mp_download/manage/download/UpDetailed 2.替换原有文件 3.重启CC

![模块[camera]_ISP与DSP的区别](/front/images/it_default2.jpg)