本文主要是介绍怎么建设高性能多核DSP+FPGA实验室?一起来河北工程大学看看,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

河北工程大学是河北省重点骨干大学,河北省人民政府与水利部共建高校,河北省重点支持的国内一流大学建设高校,河北省文明单位,坐落在中国历史文化名城、“成语典故之都”邯郸市。

学校现有工学、理学、管理学、农学、医学、文学、经济学、法学、艺术学、教育学、历史学11个学科门类。招生专业72个,其中工程类专业47个,占比达65.2%。拥有河北省唯一的服务国家特殊需求博士人才培养项目—水资源水环境调控及综合管理,拥有河北省唯一的水利工程博士后科研流动站。工程学学科进入ESI排名全球前1%。拥有水利工程、地质资源与地质工程、机械工程、管理科学与工程等17个硕士学位授权一级学科

机械与装备工程学院是河北工程大学办学历史最悠久的学院之一,学院设有6个教学系,建设有机械设计制造及其自动化、车辆工程、材料成型及控制工程、机器人工程、测控技术与仪器、机械电子工程(3+4)等6个本科专业。建设有1个国家级一流本科专业“机械设计制造及其自动化”,1个省级一流本科专业“车辆工程”,1个新工科专业“机器人工程”,“测控技术与仪器”专业已经通过工程教育认证申请。

实验室状态

创龙教仪联合河北工程大学共同建设高性能DSP+FPGA教学平台,在机械与装备工程学院-精密测量实验室,针对DSP+FPGA课程,探讨了该课程的应用方向,制定学生课程学习的培养计划。

参与交流的黄老师,孙老师等和学生们对TL6678F-TEB相关实验案例表现出十足的热情,并对创龙教仪专业的技术能力与认真的工作态度表示了肯定。

面对日新月异的技术发展,创龙教仪在不断学习与探索新技术与高校新需求之间的联系,并通过与高校间的交流学习助力高校培养能够适应新社会生产需求的高级人才,以响应国家 二十大 **“产教融合”**的方针!

特色案例

实验名称:

CameraLink工业相机实时检测与处理综合实验

实验目的:

(1)了解TI C66x DSP和Xilinx FPGA平台的优势和应用。

(2)了解CameraLink工业相机和MJPEG。

(3)学习基于TI C6678 DSP和Xilinx FPGA实现CameraLink工业相机实时检测与处理。

实验原理:

CameraLink工业相机简介

CameraLink工业相机是指具有CameraLink接口满足工业要求的相机。CameraLink接口是由AIA协会推出的数字图像信号串行通讯接口协议,是在ChannelLink技术基础上发展而来的。CameraLink标准支持的最高数据传输率可达680MB/s。

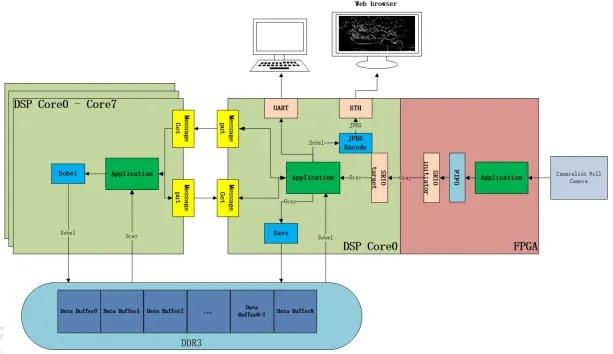

FPGA端作为SRIO Initiator,DSP端作为SRIO Target。FPGA端通过SRIO SWRITE和乒乓方式,将数据传输至DSP端的0x90000000和0x90500000的DDR地址空间。

DSP端project目录下包括两个工程,分别为主核工程与从核工程。主核工程编译后默认生成的可执行文件适用于DSP ETH1网口,如需重新生成适用于DSP ETH0网口的可执行文件,请参考关键代码小节进行源码修改。从核工程编译后生成的可执行文件为srio_image_processing_slave.out。

工程解析

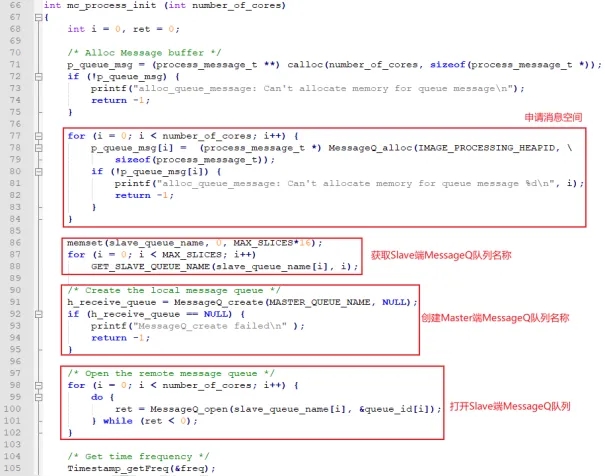

Image_processing_master任务调用mc_process_init函数,初始化和打开对应消息队列,用于传输消息。

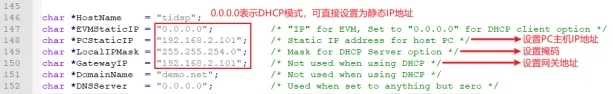

默认使用DHCP模式自动获取DSP ETH1网口IP地址。如需修改为静态IP地址,或修改为使用DSP ETH0网口,可参考如下说明进行配置。

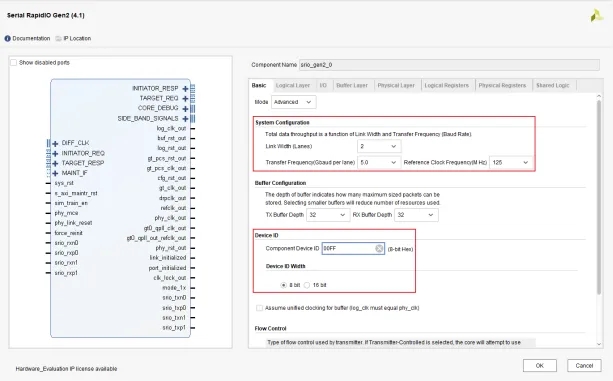

本案例使用Serial RapidIO Gen2 IP核实现SRIO Initiator,使用HELLO(Header Encoded Logical Layer Optimized)格式,支持NREAD、NWRITE、NWRITE_R、NWRITE_R、DOORBELL、MESSG等Response Packet操作。

实验设备

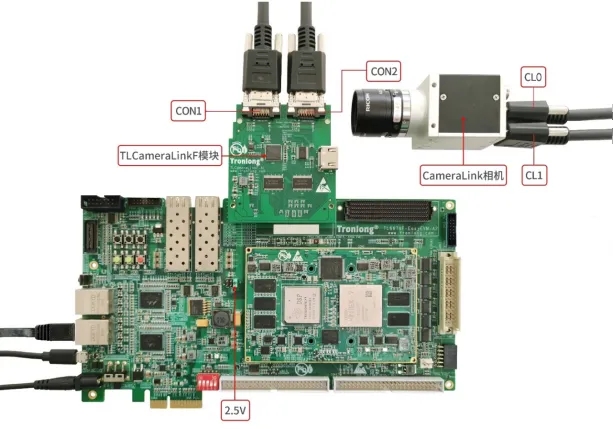

硬件:TL6678F-TEB,CameraLink黑白相机(型号:RS-A5241-CM107-S00),CameraLink视频采集模块(型号:TLCameraLinkF),路由器(动态IP需要,如采用静态IP方式可不需要)。

软件:Vivado2017.4,CCS5.5,Windows7以上操作系统。

硬件连接

(1)用Micro USB串口线将PC端连接实验主板调试串口。

(2)连接好实验箱的电源和仿真器。

(3)将FPGA下载器连接开发板FPGA端JTAG接口(CON10)到PC端。

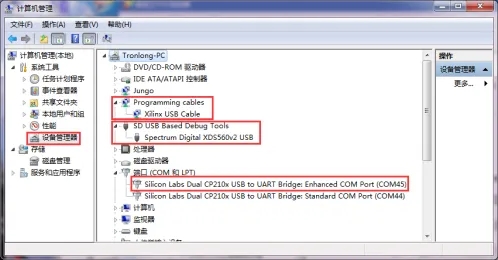

(4)打开设备管理器查看Enhanced COM port口的COM口号、查看仿真器和下载器连接是否正常。

(5)打开并设置串口调试软件,波特率为115200。

(6)将TLCameraLinkF模块连接至评估板FPGA FMC2接口,评估板J1跳线帽选择2.5V档位,以配置FMC IO的BANK电压为2.5V。请将CameraLink相机的CL0通过数据线连接至TLCameraLinkF模块的CON1接口,将CameraLink相机的CL1通过数据线连接至TLCameraLinkF模块的CON2接口。

(7)用网线连接实验主板和路由器,实验主板默认ETH1口,要保证开发板与PC端保持在同一网段下。

(8)拨码开关拨到NO BOOT模式:000XX(备注:XX为1或0均可)。

(9)实验箱上电。

实验现象

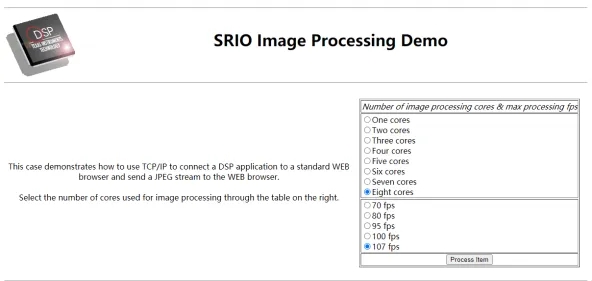

在PC机浏览器输入评估板IP地址打开网页界面,在网页界面中选择处理核心数量为Eight cores,选择本案例所使用相机的最高处理帧率为107fps。

点击"Program Item",网页将显示经DSP端进行Sobel(边缘检测)算法处理后的图像。

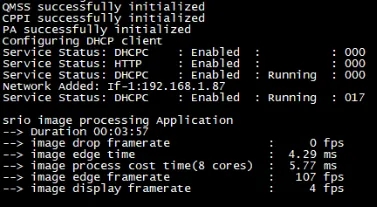

同时,DSP端串口调试终端将会打印处理信息。

这篇关于怎么建设高性能多核DSP+FPGA实验室?一起来河北工程大学看看的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!