多核专题

【论文阅读】一种针对多核神经网络处理器的窃取攻击(2020)

摘要 攻击者可以通过侧信道信息(Side-channel)完成模型窃取攻击[17]. [17] Hua W Z, Zhang Z R, Suh G E. Reverse Engineering Convolutional Neural Networks through Side-channel Information Leaks[C]. 2018 55th ACM/ESDA/IEEE Des

英特尔多核平台编程优化大赛报告

前言 本次优化使用的CPU是Intel Xeon 5130 主频为2.0GHz 同Intel酷睿2一样是基于Core Microarchitecture 的双核处理器。本次优化在Intel的工具帮助下主要针对Core Microarchitecture 系列处理器进行优化。但是由于未知原因,Intel VTune Analyzers并不能在该系统下正常工作。所以,所有使用Intel VTune

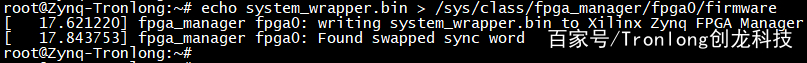

【ZYNQ MPSoC开发】PS裸机多核程序的固化

写在前面 多核程序的固化总体操作流程与单核程序固化相同,针对本文中的一些操作,大家如果有不清楚的,可以参考我之前写的单核固化的博客。 共通前置步骤 这是区别于单核固话的主要不同之处。以我的程序为例,我用到了两个核心,分别跑在A53_0和A53_1上,结构如下图所示: 1,首先对各个核心的应用程序都build好,生成.elf文件。

怎么建设高性能多核DSP+FPGA实验室?一起来河北工程大学看看

河北工程大学是河北省重点骨干大学,河北省人民政府与水利部共建高校,河北省重点支持的国内一流大学建设高校,河北省文明单位,坐落在中国历史文化名城、“成语典故之都”邯郸市。 学校现有工学、理学、管理学、农学、医学、文学、经济学、法学、艺术学、教育学、历史学11个学科门类。招生专业72个,其中工程类专业47个,占比达65.2%。拥有河北省唯一的服务国家特殊需求博士人才培养项目—水资源水环境调控及综合管

多核的idleTask的设定及其功能

平台介绍: loongson3A-4核cpu,vxWorks6.8 在多核使能后,核就自动加载了idleTask的内容,这个idleTask时什么时候设置好的呢?idleTask任务的内容是什么呢? 一,设置时机 函数调用关系 usrInit--->usrKernelInit--->kernelInit _WRS_FUNC_NORETURN void kernelInit

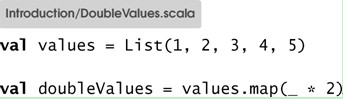

【连载】Scala程序设计:Java虚拟机多核编程实战——简介

可以在JVM上编程的语言有很多。通过这本书,我希望让你相信花时间学习Scala是值得的。 Scala语言为并发、表达性和可扩展性而设计。这门语言及其程序库可以让你专注于问题领域,而无需深陷于诸如线程和同步之类的底层基础结构细节。 如今硬件已经越来越便宜,越来越强大。很多用户的机器都装了多个处理器,每个处理器又都是多核。虽然迄今为止,Java对我们来说还不错

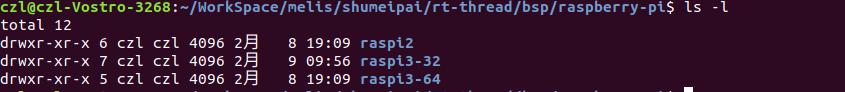

在树莓派3b/3b+上搭建rt-thread多核开发环境

1.本文目的 本⽂主要介绍如何快速⾼效的搭建树莓派rt-thread的开发环境。按照⽂章的步骤,可以很快速的将rt-thread SMP系统在树莓派上运⾏起来。 2.准备条件 1.raspberry-pi 3b/3b+均可,本文使用的是3b+版本 2.usb转ttl串口模块,本文使用的是ch340 3. ubuntu系统的电脑, 本文使用的是ubuntu1

(书稿底稿)(C/C++)第一章:CPU基础知识 1.2.3 CORE内核 1.2.4 多核概念

1.2.3 CORE内核 处理器架构和核心微架构 上面已经描述了,CPU被分为前端和后端,它们又被多个功能块(function block)组成,如:解码单元(decode unit)、预处理分支单元(branch-prediction unit)、整数单元(integer unit)、加载存储单元(load-store uni

【AM5728】TI最新DSP+ARM异构多核平台

AM5728是TI Sitara系列高性能SOC,得益于异构多核处理架构,CPU内集成了多核DSP、多核PRU、IVA-HD、GPU等协处理单元,通过硬件加速的方式极大增强CPU的数据、多媒体处理能力,可满足工业协议支持、大数据计算、实时控制等应用需求,同时采用先进的28纳米生产工艺,极大降低处理器的功耗,能耗比更加突出。 广州创龙基于TI AM5728浮点双DSPC

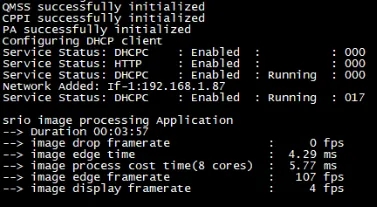

基于TI KeyStone C66x系列多核架构定点/浮点TMS320C6678设计的评估板千兆以太网口

CPU处理器 TI TMS320C6678是一款TI KeyStone C66x多核定点/浮点DSP处理器,集成了8个C66x核,每核心主频高达1.0/1.25GHz,支持高性能信号处理应用,拥有多种工业接口资源,以下是TMS320C6678 CPU功能框图: 千兆以太网口 开发板引出2个千兆以太网口(CON5、CON6),采用了Marvell Alaska 88E1111网络芯片,

创龙结合TI KeyStone系列多核架构TMS320C6678 DSP以及Xilinx Kintex-7 FPGA评估板的XADC接口

CPU处理器 基于TI KeyStone C66x多核定点/浮点DSP TMS320C6678 + Xilinx Kintex-7 FPGA的高性能信号处理器,TI TMS320C6678集成8核C66x,每核主频1.0/1.25GHz,每核运算能力高达40GMACS和20GFLOPS,FPGA XC7K325T逻辑单元326K个,DSP Slice 840个,8对速率为12.5Gb/s高速串行

ZYNQ PS + PL异构多核案例开发手册之axi_timer_pwm_demo案例

本文主要介绍ZYNQ PS + PL异构多核案例的使用说明,适用开发环境:Windows 7/10 64bit、Xilinx Vivado 2017.4、Xilinx SDK 2017.4。 axi_timer_pwm_demo案例 1 案例功能 案例功能:PS端通过AXI4-Lite总线发送命令至PL端AXI Timer IP核,IP核再根据命令通过PWM方式控制评估底板PL端LED5的状

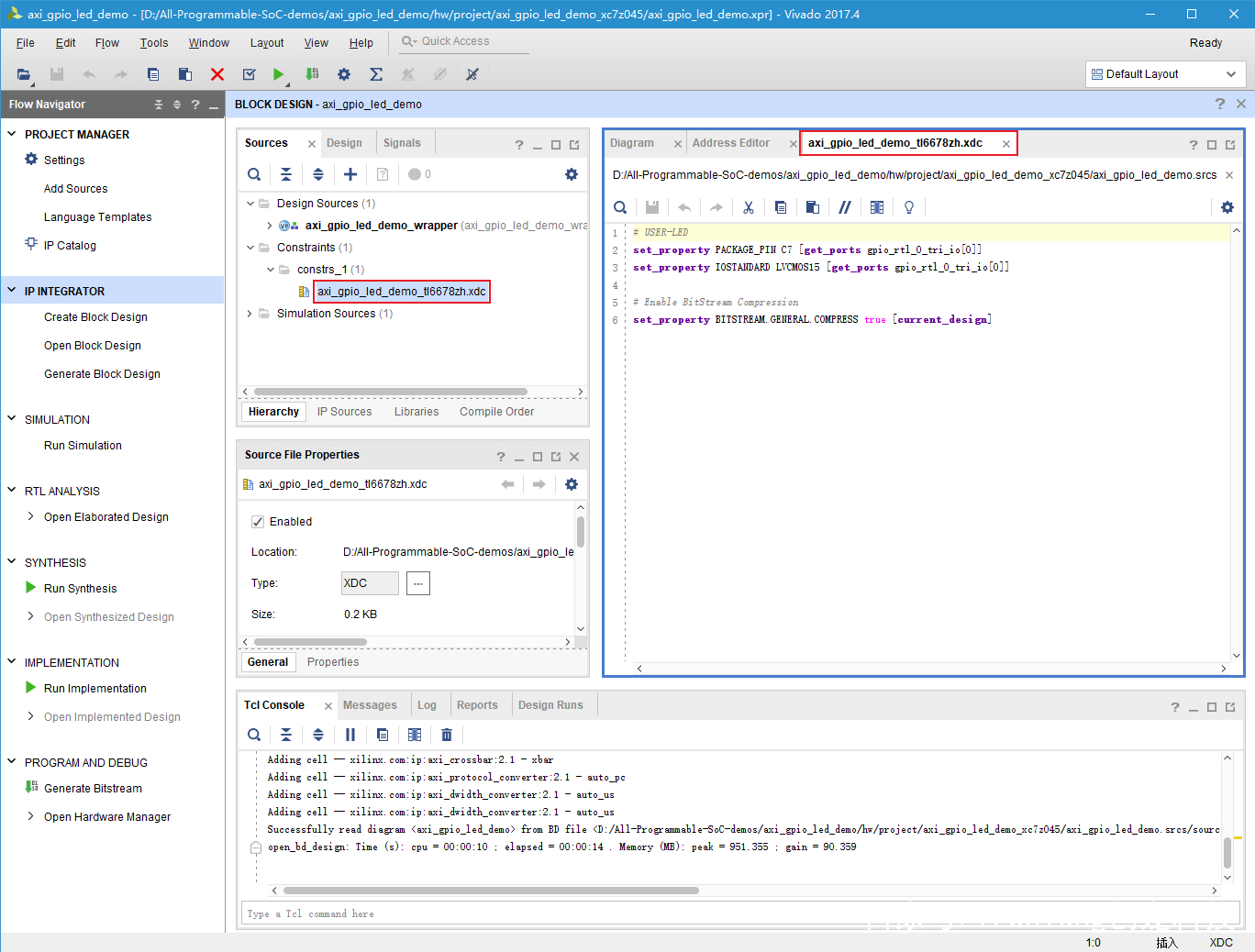

ZYNQ PS + PL异构多核案例开发手册之1axi_gpio_led_demo案例

本文主要介绍ZYNQ PS + PL异构多核案例的使用说明,适用开发环境:Windows 7/10 64bit、Xilinx Vivado 2017.4、Xilinx SDK 2017.4。 案例包含PL端Vivado工程,主要使用Xilinx提供的标准IP核配置PL端资源实现接口扩展,同时包含PS端裸机/Linux程序、PL端MicroBlaze应用程序。 案例使用Block Design

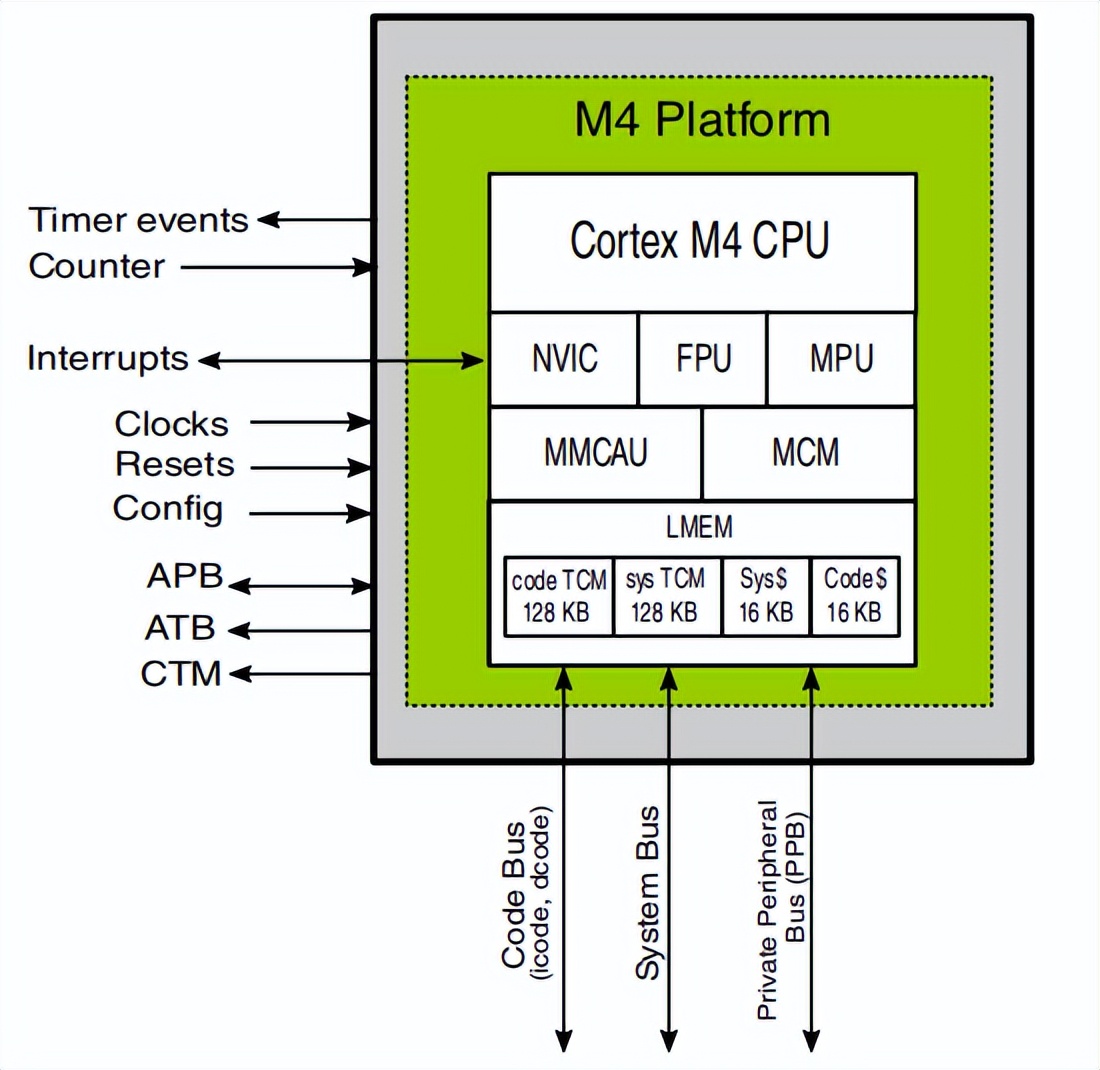

i.MX 8M Mini——四核Cortex-A53+Cortex-M4多核CPU如何实现工控

随着ARM处理器性能不断增强,当前越来越多产品都倾向尽量用单一架构的高性能ARM平台来满足产品的不同功能要求。但是,在工业应用领域还是要面对一些实时控制和通讯的要求,单一系统架构无法完全满足。面对复杂的工业应用场景,创龙科技推出了基于NXP i.MX 8M Mini设计的工业核心板和评估板,提供了四核Cortex-A53 + 单核Cortex-M4异构多核的组合使用方法,使Cortex-M4发挥出

Cache多核之间的一致性MESI

快速链接: 【精选】ARMv8/ARMv9架构入门到精通-[目录] 👈👈👈 思考: 1、为什么要学习MESI协议? 哪里用到了?你确定真的用到了? 2、MESI只是一个协议,总得依赖一个硬件去执行该协议吧,那么是谁来维护或执行的呢? 3、你不理解的真的是MESI吗,真的需要学习MESI吗? 应该是cache架构吧 4、core0和core1之间的一致性是MESI? 那cluste

K210 FreeRTOS多任务多核系统调度

一、目的 众所周知,K210这款AI新品是一款64bit 双核芯片,其支持裸机编程,并且官方也提供freertos sdk,方便开发者在其上进行多任务应用开发。那么如何进行任务创建和多核开发呢。 二、参考 #include <stdio.h>#include "FreeRTOS.h"#include "task.h"static void task_0(void *args) {whil

多核编程4种方式:多线程、多进程、csp(轻量级线程)、actor(轻量级进程)

1)多线程方式利用多核心 锁(信号量、互斥锁、自旋锁、读写锁、原子锁cas、乐观锁、悲观锁) 锁的粒度 什么情况下用什么锁,比较困惑 消息队列 管道(不需要加锁): pipe+epoll/select/epoll 资源+锁 并发实体:线程 总结: 需要大量的锁。 2)多进程方式利用多核心

网络多核处理器的入侵检测系统的设计

随着计算机硬件技术的迅速发展,处理器集成晶体管数量越来越多,主频也越来越高,处理器的性能越来越强大。同时,现代社会对信息网络处理速度的要求也提高了,不断需要更强处理能力的CPU。众所周知,处理器性能不断提高主要基于两个原因:-是半导体工艺的逐渐进步;二是处理器体系结构的不断发展。它们相辅相成,互相刺激以促进对方的发展。但是由于半导体工艺发展到今天,处理器集成的晶体管数量有数亿个,半导体

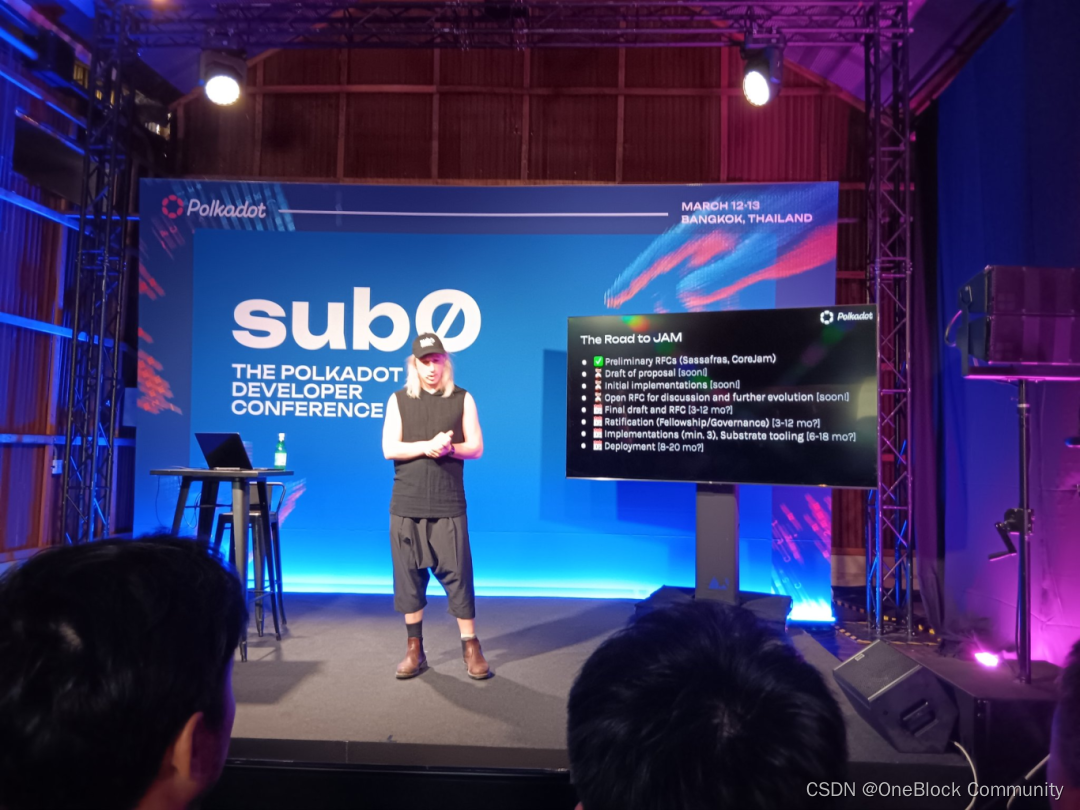

Gavin Wood 精彩演讲|安全灵活 JAM 链,打造去中心化多核计算机

Polkadot 年度开发者大会 sub0 Asia 近期在泰国曼谷正式落幕。面对区块链行业的激烈竞争,Polkadot 创始人 Gavin Wood 在演讲中说明将如何利用 Polkadot 2.0 与 JAM 链带来新的技术创新,推动生态持续发展。 Polkadot 将推一个名为 JAM 链的新网络。JAM 链将会是无状态的去中心化网路,作为 Polkadot 的全新运算基础设施,提供多

多核(CPU)系统中并行计算Atomic原子操作与缓存一致性(memory/cache coherency)

单线程的程序执行过程中指令处理数据(内存读写)的过程可以认为是线性连续的,也就是前后步骤硬性依存关系,第一步执行完才会执行第二步,流程逻辑简单,但是运行时性能弱,在多核的现代系统中无法发挥算力优势,也就不能提升性能,用户体验和执行效率低下。最多,只能用并发特性,更充分的利用处理指令周期的时间片。 多核系统(这里主要指的是多CPU核心的系统)中运行的程序软件,需要发挥多核的算力,不但要并发还要并行

多核多cluster多系统之间缓存一致性概述

引流关键词:缓存,高速缓存,cache, CCI,CMN,CCI-550,CCI-500,DSU,SCU,L1,L2,L3,system cache, Non-cacheable,Cacheable, non-shareable,inner-shareable,outer-shareable, optee、ATF、TF-A、Trustzone、optee3.14、MMU、VMSA、cache、T