本文主要是介绍ZYNQ PS + PL异构多核案例开发手册之1axi_gpio_led_demo案例,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

本文主要介绍ZYNQ PS + PL异构多核案例的使用说明,适用开发环境:Windows 7/10 64bit、Xilinx Vivado 2017.4、Xilinx SDK 2017.4。

案例包含PL端Vivado工程,主要使用Xilinx提供的标准IP核配置PL端资源实现接口扩展,同时包含PS端裸机/Linux程序、PL端MicroBlaze应用程序。

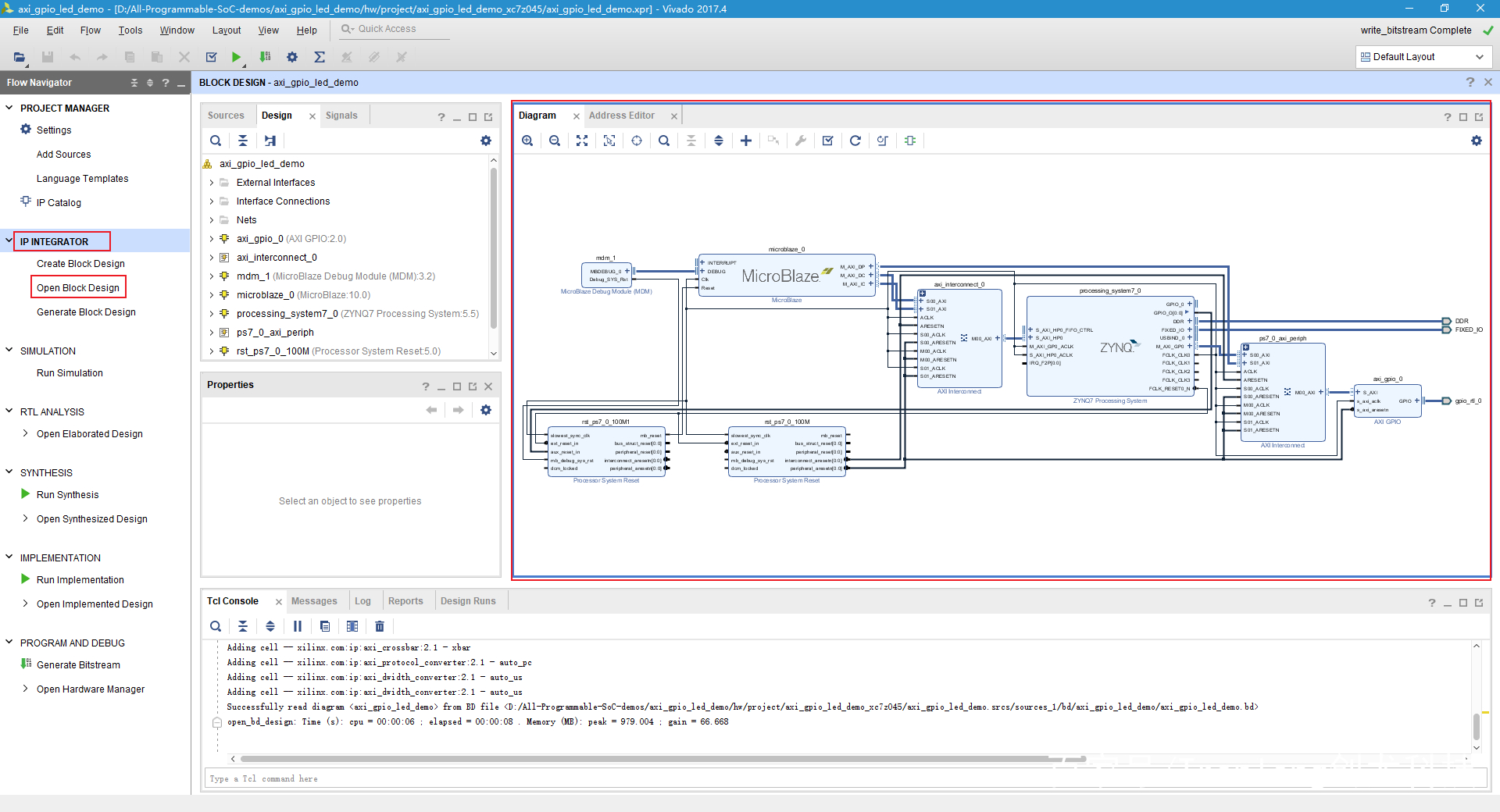

案例使用Block Design + Verilog语言方式进行开发,可在Vivado界面点击"IP INTEGRATOR -> Open Block Design"打开BLOCK DESIGN开发界面。

图 1

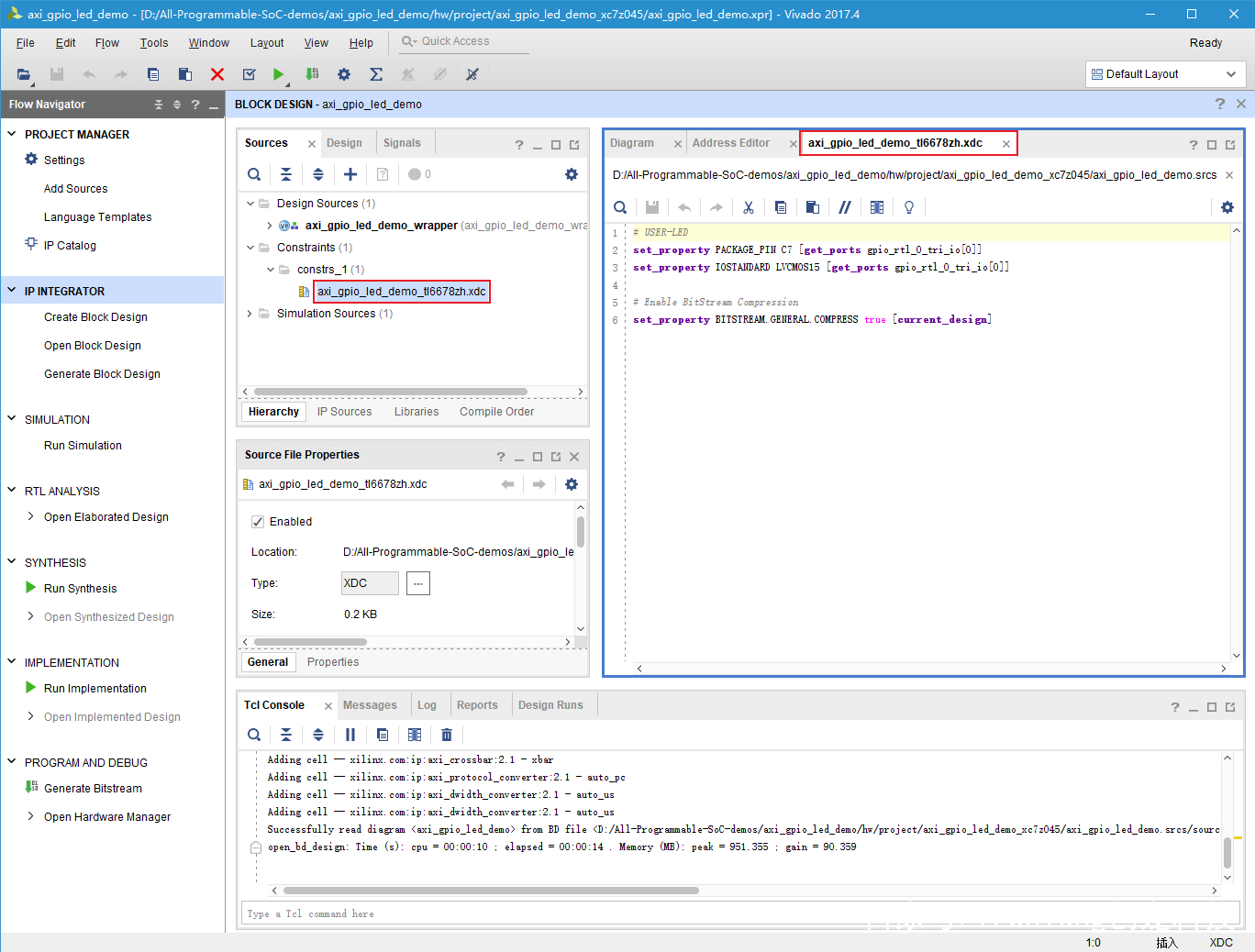

可点击"Sources -> Constraints",双击打开.xdc约束文件。

图 2

处理器硬件资源详细开发说明可查阅产品资料“6-开发参考资料\数据手册\核心板元器件\ZYNQ\”目录下的《ug585-Zynq-7000-TRM.pdf》文档。

视频相关案例说明,请查阅视频案例开发手册。

1 axi_gpio_led_demo案例

1.1 案例功能

案例功能:PS端通过AXI4-Lite总线发送命令至PL端AXI GPIO IP核,IP核再根据命令控制评估底板PL端LED5的状态

这篇关于ZYNQ PS + PL异构多核案例开发手册之1axi_gpio_led_demo案例的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!