本文主要是介绍基于 Vitis HLS 的单个乘法 DSP 映射研究,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

文章目录

- 1 自媒体账号

- 2 引言

- 3 整数乘法

- 4 定点乘法

- 5 浮点乘法

- 6 总结

1 自媒体账号

目前运营的自媒体账号如下:

- 哔哩哔哩 【雪天鱼】: 雪天鱼个人主页-bilibili.com

如果觉得有所收获的话,可以点击我的主页 -> 充电 -> 自定义充电 支持一下,十分感谢!

- 微信公众号 【雪天鱼】

- CSDN 【雪天鱼】: 雪天鱼-CSDN博客

QQ 学习交流群

- FPGA科研硕博交流群 910055563 (进群有一定的学历门槛,长期未发言会被请出群聊,主要交流FPGA科研学术话题)

- CNN | RVfpga学习交流群(推荐,人数上限 2000) 541434600

- FPGA&IC&DL学习交流群 866169462

记录下自己的学习过程,个人拙见,请谨慎参考。

2 引言

ZCU106 的DSP型号为 DSP48E2,支持的最大乘法位宽是 27-bit x 18-bit;

目标:通过简单的单个元素乘法,观察 HLS 工具将不同位宽的乘法映射为几个DSP

- Vitis HLS 2021.1

- ZCU106

以下结论的成立的前提是相信 HLS C综合后报告结果是正确的,因为本文主要研究对于HLS工具而言,是将不同位宽的乘法映射为几个DSP。所以不会使用 Vivado 进一步进行验证。

但实际上,Vitis HLS 和 Vivado 的综合结果是会有一定的差距的。

3 整数乘法

- 测试代码:

#include <ap_int.h>constexpr unsigned int IN_SIZE = 20;

typedef ap_int<32> int_test;

void pixel_mul_int(int_test input[IN_SIZE],int_test weight[IN_SIZE],int_test output[IN_SIZE]){for(int i=0; i<IN_SIZE; i++){#pragma HLS PIPELINE II=1output[i] = input[i] * weight[i];}}

通过一个 for 循环实现 IN_SIZE 次元素相乘

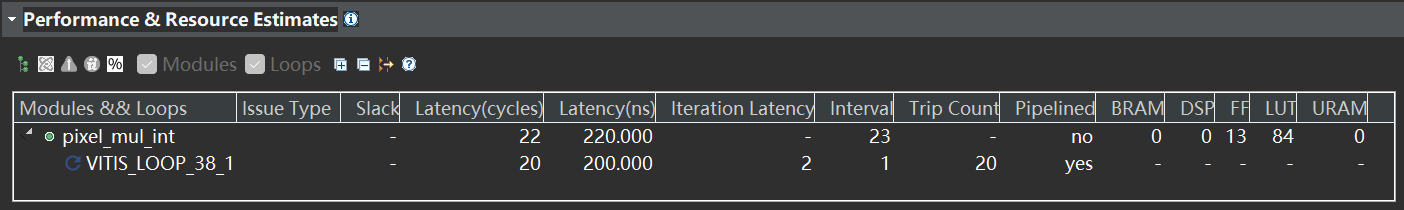

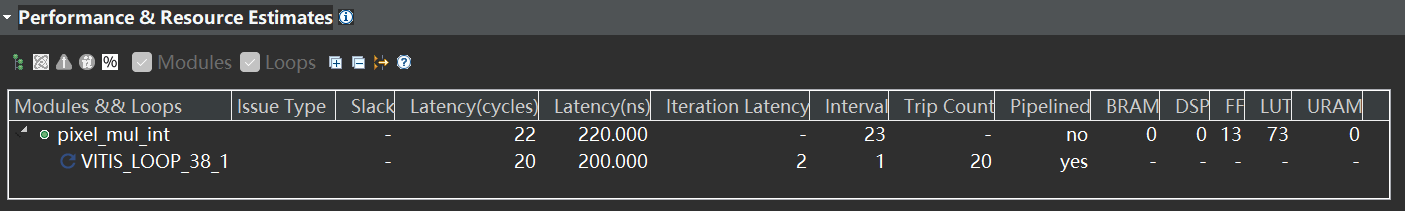

- 32位 x 32位

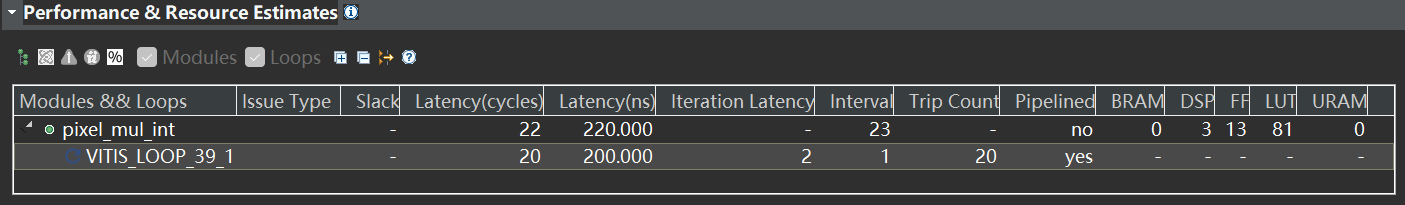

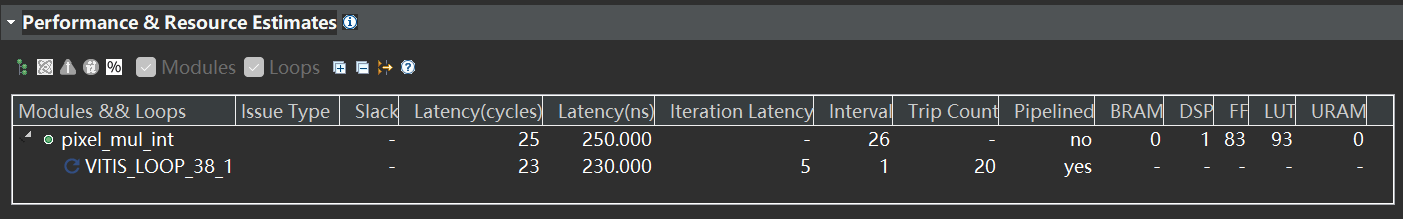

32 位整数乘法需要 3 个DSP

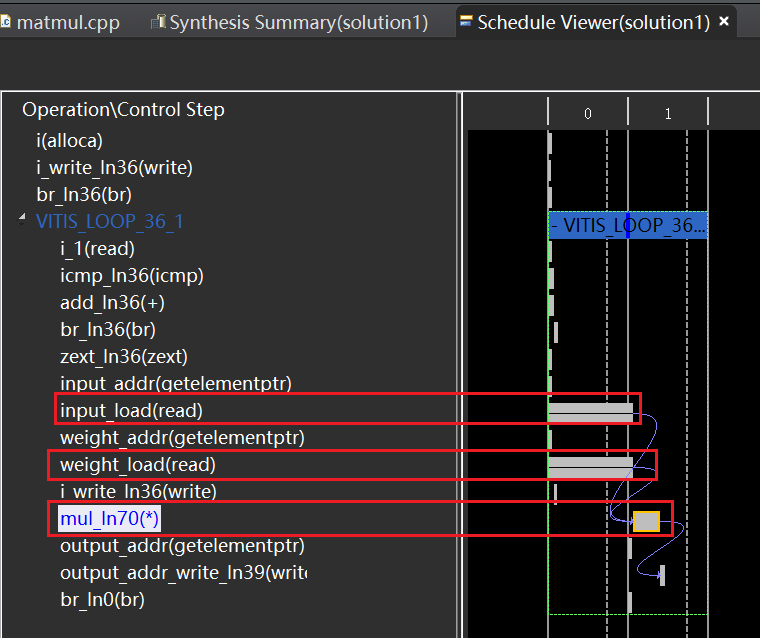

2 个时钟周期完成单次迭代计算,周期1读input和weight, 周期2 进行乘法计算

-

27 位 x 27 位

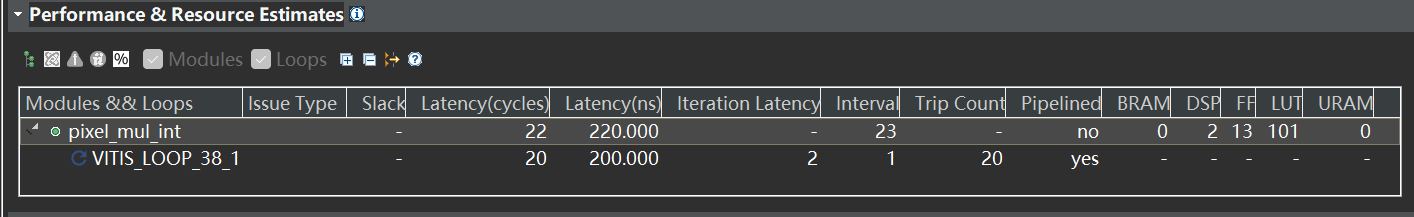

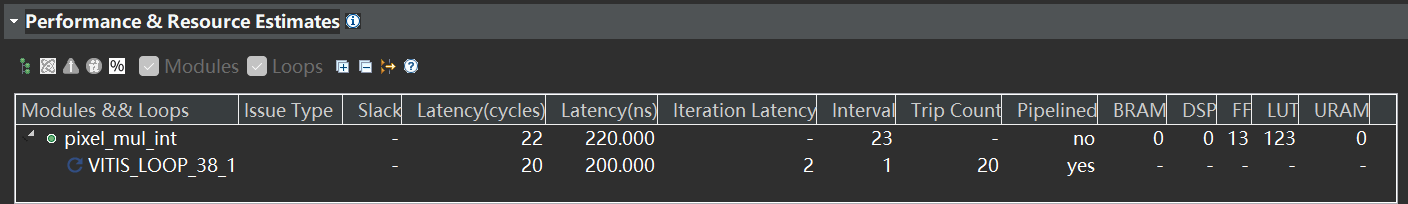

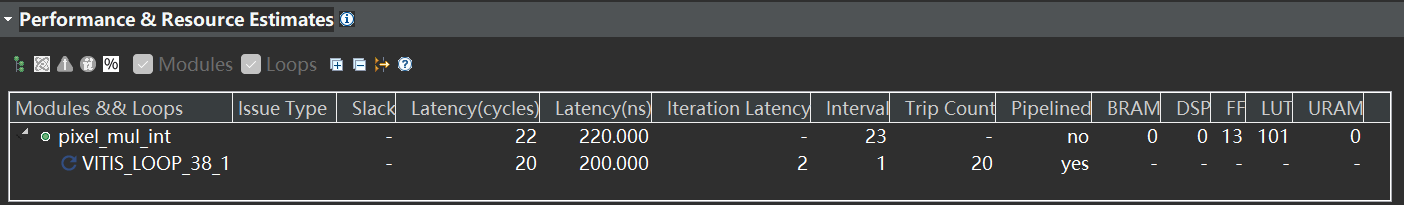

27 位整数乘法需要 2 个DSP -

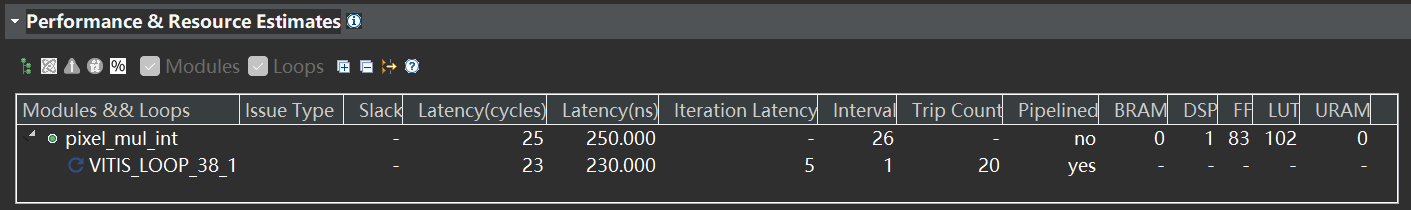

18位 x 18 位 | 17位 x 17位

18位整数乘法需要 1 个DSP

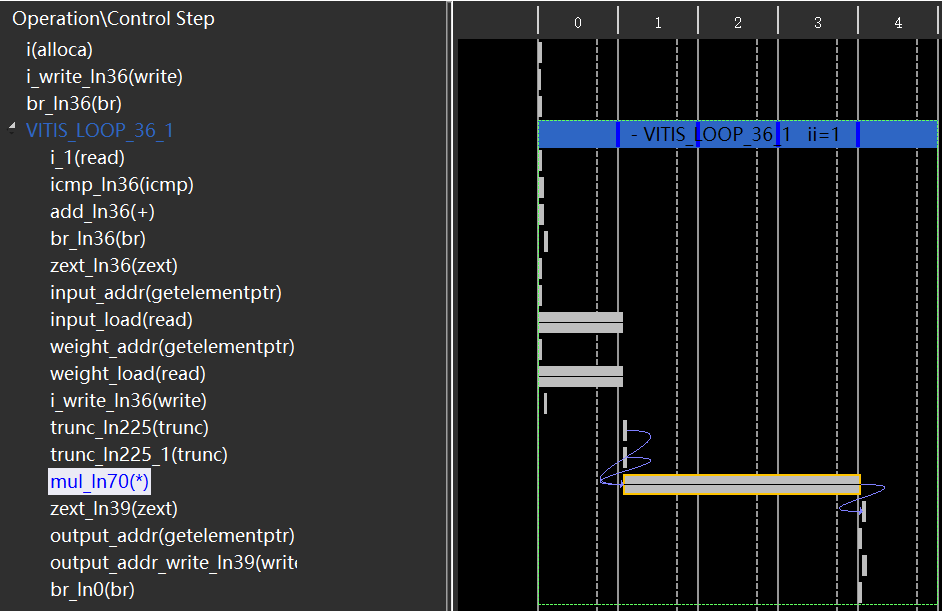

问题:使用单个DSP,为什么 Iteration Latency就从 2 变成了 5

从调度图中可以看到,此时乘法需要三个时钟周期才能完成,导致完成单次迭代的时间变长 -

16 位 x 16 位 | 14 位 x 14 位 | 12位 x 12位 | 11位 x 11位

-

10位 x 10位

-

8 位 x 8 位

不再占用DSP,使用 LUT 计算 -

6 位 x 6 位

-

4位 x 4 位

所以对于整数乘法总结如下:

- 当被乘数位宽 > 27-bit, 乘数位宽 > 18-bit 需要3个DSP实现; 当被乘数位宽 <= 27-bit, 乘数位宽 > 18-bit 需要2个DSP实现;当被乘数位宽 <= 27-bit, 乘数位宽 <=18-bit 需要1个DSP实现;

- 当乘数与被乘数的位宽均较小时(这里临界点是 10位整数乘法),将不会映射到DSP硬核上计算,而是采用LUT实现。并且随着位宽的继续减少,所用的LUT资源也会随之减少。

4 定点乘法

- 测试代码:

#include <ap_fixed.h>constexpr unsigned int IN_SIZE = 20;

typedef ap_fixed<32, 10> fixed_mul;

void pixel_mul_fixed(fixed_mul input[IN_SIZE],fixed_mul weight[IN_SIZE],fixed_mul output[IN_SIZE]){for(int i=0; i<IN_SIZE; i++){#pragma HLS PIPELINE II=1output[i] = input[i] * weight[i];}}

-

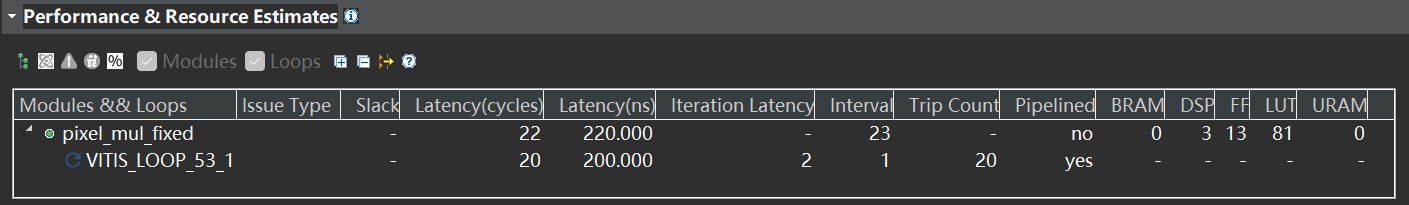

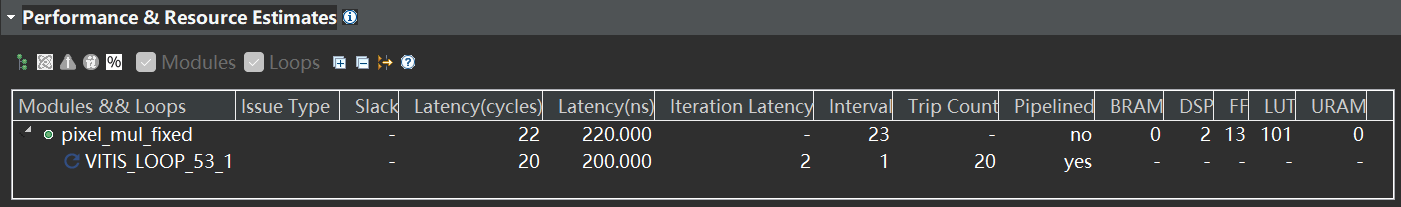

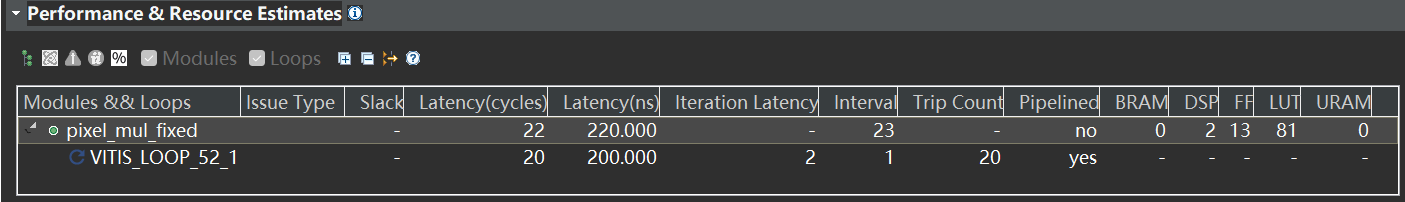

32位有符号定点数计算 — ap_fixed<32, 20> | ap_fixed<32, 10> | ap_fixed<32, 5>

与 32 位整数计算的综合结果一样, 且整数位的大小不影响最终结果,综合结果只和乘数和被乘数的位宽有关。即 DSP 能实现支持位宽内的定点小数乘法。 -

27位有符号定点数计算 — ap_fixed<27, 10>

-

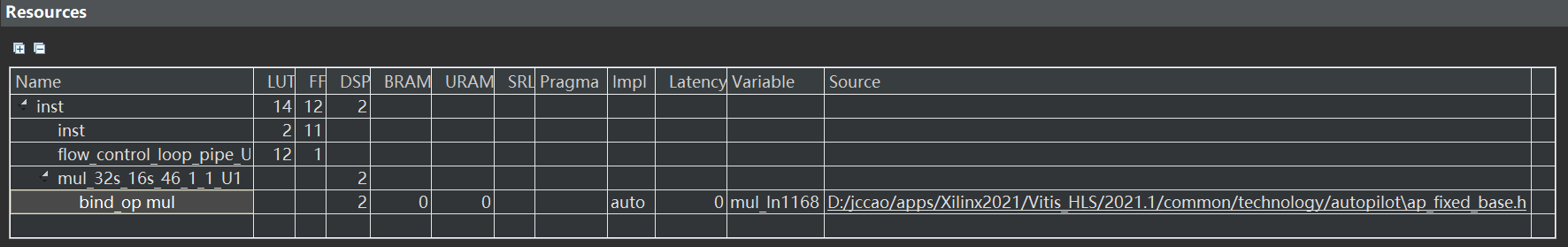

ap_fixed<32, 10> x ap_fixed<16, 2>

HLS 内启动 Implementation

-

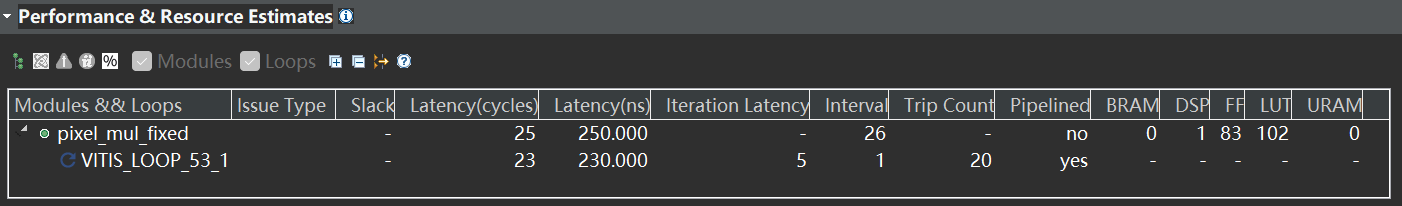

18位有符号定点数计算 — ap_fixed<18, 10>

-

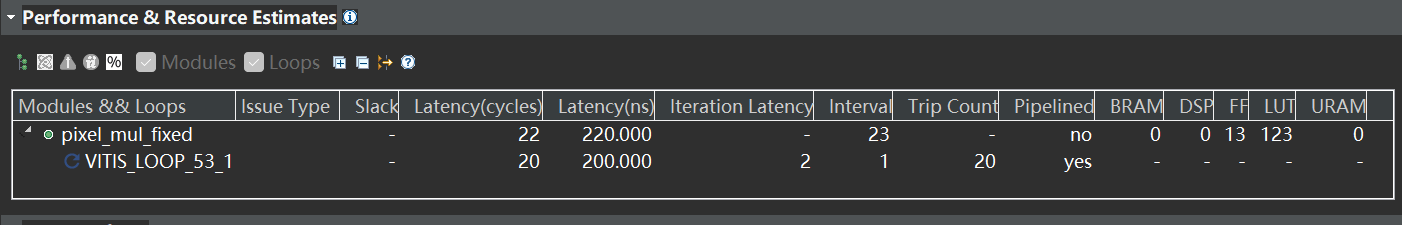

10位有符号定点数计算 — ap_fixed<10, 5>

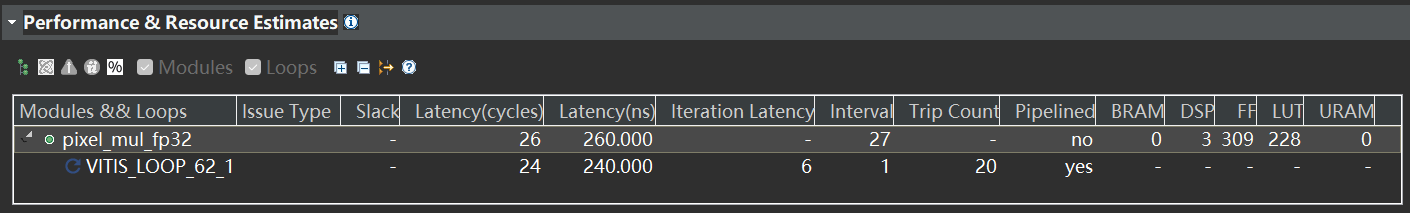

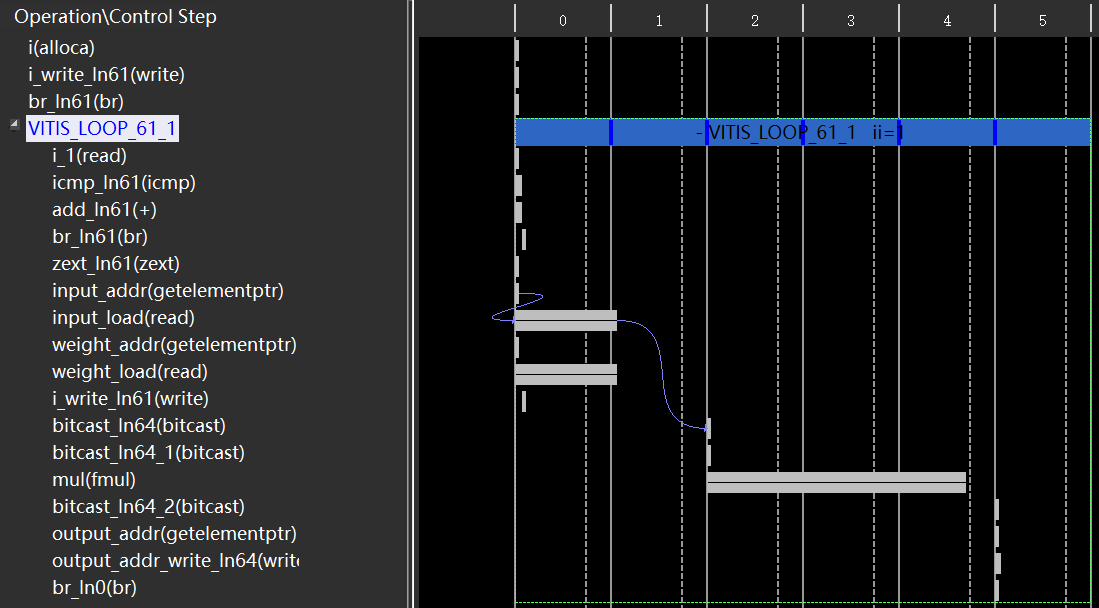

5 浮点乘法

- fp32 x fp32

遇到的问题:无法打开调度图,

通过重启 Vitis HLS ,重新C综合后解决该问题

第0周期和第1周期读取输入数据,第2,3,4周期进行乘法计算,第5周期写回结果

6 总结

- 整数乘法和定点乘法,只有乘数和被乘数的总位宽不变,乘法在 DSP 实现的策略一样,延迟和占用个数不会改变。

- 在使用 HLS 工具进行硬件开发时,在满足精度的前提下,可以通过限制乘数和被乘数在目标 DSP 硬核的输入范围内,避免浪费DSP资源。

待解决问题:

- Q: DSP48E2 是否可以直接支持整数运算、定点运算以及浮点运算?

可能需要通过 Vivado 调用 DSP IP 进行更深入的研究

这篇关于基于 Vitis HLS 的单个乘法 DSP 映射研究的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!