vitis专题

Vitis AI 综合实践(DPU example: dpu_resnet50.ipynb)

目录 1. 简介 2. 代码解析 2.1 导入库 2.2 图像预处理 2.3 读取标签 2.4 读取图像 2.5 获取IO形状 2.6 申请内存 2.7 运行推理 2.8 后处理 3. 相关类的介绍 3.1 DpuOverlay 类 3.2 Overlay 类 3.3 Bitsteam 类 3.4 Device 类 3.5 DeviceMeta 元类 3.6 ty

Vitis AI 基本认知(Tiny-VGG 标签获取+预测后处理)

目录 1. 简介 2. 解析 2.1 获取标签 2.1.1 载入数据集 2.1.2 标签-Index 2.1.3 保存和读取类别标签 2.2 读取单个图片 2.3 载入模型并推理 2.3.1 tiny-vgg 模型结构 2.3.2 运行推理 2.4 置信度柱状图 2.5 预测标签 3. 完整代码 4. 总结 1. 简介 本博文在《Vitis AI 基本认知

sdk 转 vitis 异常处理

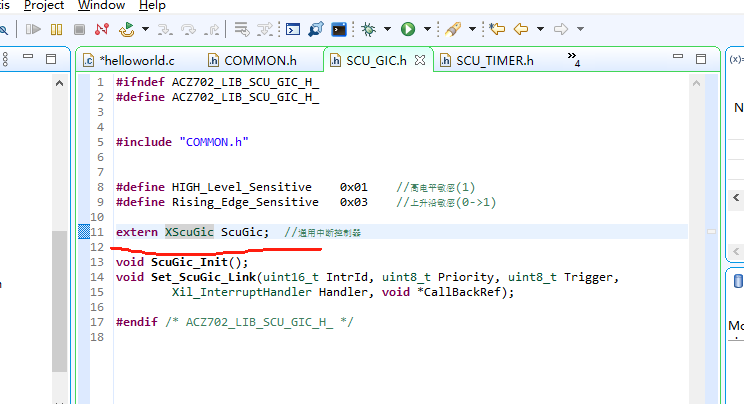

1. 烧写无法启动,报 done不拉高 2. c++报重复定义 经发现确实函数定义没有处理extern 另外烧写过程可能会报内存错误 这时候检查jtag模式 开关 另一类说法 vitis会读取一些变量 如果axi和ddr有一些问题一样会报错

Vitis AI 进阶认知(Torch量化基础+映射+量化参数+对称性+每通道+PTQ+QAT+敏感性)

目录 1. 介绍 2. 基本概念 2.1 映射函数 2.2 量化参数 2.3 校准 2.4 对称与非对称量化 2.5 Per-Tensor and Per-Channel 2.6 PTQ 2.7 QAT 2.8 敏感性分析 2.6 退火学习率 3. 几点建议 4. 总结 1. 介绍 Practical Quantization in PyTorch | P

基于 Vitis HLS 的单个乘法 DSP 映射研究

文章目录 1 自媒体账号2 引言3 整数乘法4 定点乘法5 浮点乘法6 总结 1 自媒体账号 目前运营的自媒体账号如下: 哔哩哔哩 【雪天鱼】: 雪天鱼个人主页-bilibili.com 如果觉得有所收获的话,可以点击我的主页 -> 充电 -> 自定义充电 支持一下,十分感谢! 微信公众号 【雪天鱼】 CSDN 【雪天鱼】: 雪天鱼-CSDN博客 QQ 学习交流群

Vitis HLS 学习笔记--添加 RTL 黑盒函数

目录 1. 简介 2. 用法详解 2.1 需要的文件 2.1.1 RTL 函数签名 2.1.2 黑盒 JSON 描述文件 2.1.3 RTL IP 文件 2.2 操作步骤 3. 总结 1. 简介 Vitis HLS 工具可以将现有的 Verilog RTL IP(即硬件描述语言编写的模块)集成到 C/C++ HLS 项目中。通过这种方式,Vitis HLS 能够将 RT

Vitis HLS 学习笔记--Vitis Accelerated Libraries介绍

目录 1. 简介 2. 库的文件结构 3. 分类介绍 3.1 blas 3.2 codec 3.3 data_analytics 3.4 data_compression 3.5 data_mover 3.6 database 3.7 dsp 3.8 graph 3.9 hpc 3.10 motor_control 3.11 quantitative_finance

Vitis HLS 学习笔记--移除内存分配malloc

目录 1. 简介 2. 示例解析 2.1 源码解释 2.2 malloc 分析 2.3 替代方案分析 3. 总结 1. 简介 Vitis HLS 也不支持动态创建或删除 C/C++ 对象(用于综合)。 本文探究如何在C/C++代码中避免使用显式的malloc函数来分配内存。在硬件设计和FPGA开发中,避免动态内存分配是一个常见的实践。 通过一个例子,了解 malloc

Vitis HLS 学习笔记--矢量数据类型

目录 1. 简介 2. 用法详解 2.1 存储器布局 2.2 示例展示 2.3 综合报告 3. 总结 1. 简介 在 Vitis HLS 中,矢量数据类型是一种特殊的数据类型,它允许你一次处理多个数据元素,就像一排并排的盒子,每个盒子里都装着一个数据元素。这种方式非常适合于同时执行多个相同的操作,这就是所谓的 SIMD(单指令多数据)操作。 矢量数据类型用法 #inc

Vitis HLS 学习笔记--接口存储器布局模型

目录 1. 简介 2. 详解 2.1 数据对齐 2.2 数据结构填充 3. 总结 1. 简介 软件开发者写的程序会在 CPU 处理器上运行,而硬件开发者设计的“内核”则会在 FPGA 上运行。这两部分需要通过一个精心设计的接口来沟通,就像两个人用对讲机来交流一样。为了确保这种沟通顺畅,数据必须以一种特定的方式来存储和组织,这就是所谓的存储器模型。这个模型就像是一个书架,告诉你

Vitis HLS 学习笔记--接口聚合与解聚-AXI主接口

目录 1. 简介 2. 用法及语法 3. 详细解读 4. 总结 1. 简介 在使用 Vitis HLS 工具进行硬件设计时,如果你在接口上使用了结构体,工具会自动把结构体里的所有元素组合成一个整体。就像把一堆零件组装成一个玩具一样。这样做的好处是,数据可以作为一个单元一起处理,而不是分开处理每个元素。 默认情况下,Vitis HLS 会自动做这个组合工作,你不需要特别告诉它去

Vitis HLS 学习笔记--FRP自由运行流水线

1. 简介 在Vitis HLS中,FRP自由运行流水线(Free Running Pipeline)是一种流水线风格的架构,它即使在没有输入数据的情况下也会运行。这种架构优化了频率,因为它减少了寄存器使能信号的扇出,简化了流水线控制逻辑。FRP流水线通常用于需要避免因为停滞而导致的性能下降或死锁的场合。 FRP流水线与传统的可刷新流水线(flushable pipeline)相比,有以下优点

Vitis HLS 学习笔记--控制驱动与数据驱动混合编程

目录 1. 简介 2. 示例分析 2.1 代码分析 2.2 控制驱动TLP的关键特征 2.3 数据驱动TLP的关键特征 3. 总结 1. 简介 在 HLS 硬件加速领域,Vitis HLS 提供了强大的抽象并行编程模型。这些模型包括控制驱动和数据驱动的任务级并行性(TLP),它们是硬件设计优化的基石。控制驱动TLP通过#pragma HLS dataflow指令实现函数的并

vitis zync 介绍

https://blog.csdn.net/sements/article/details/109121380 文章目录 1 - 从 Xilinx Zynq 讲起 2 - Vitis 平台概览 2.1 - Vitis IDE 2.2 - Vitis HLS / Accelerated Library 2.3 - Vitis AI 2.4 - Petalinux 3 - The end? Xili

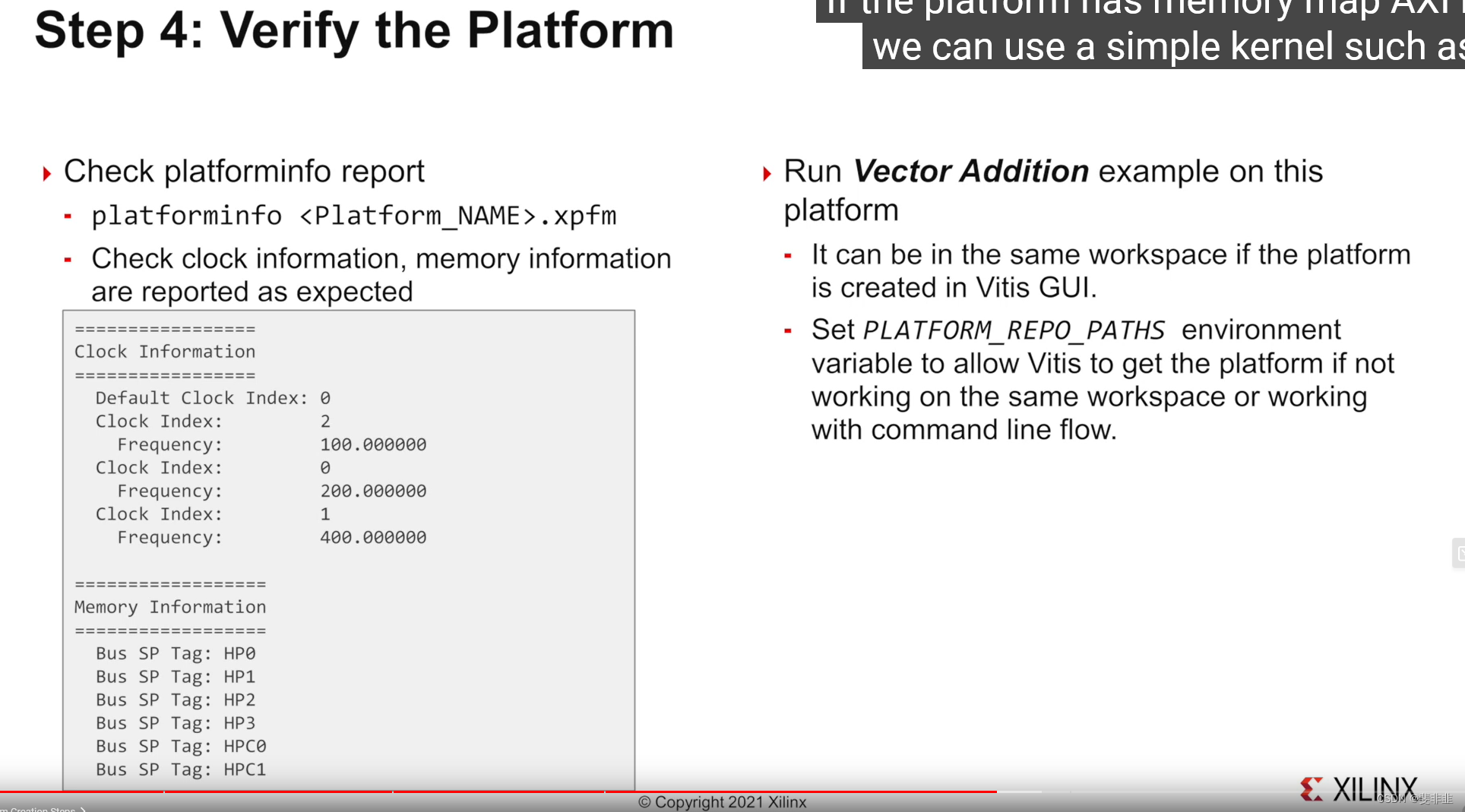

vivado新版本兼容老版本,vitis classic兼容sdk教程

new version: vivado版本2023.2 和vitisv classic 2023.2 old version: vivado 2018.3以及之前的版本 打开工程 自动升级到当前版本,选择OK 点击Yes,合并当前的目录架构 点击OK 点击Report IP status 勾选要升级的IP核,点击升级 在项目工程文件夹新建个文件夹ps_hello.vitis

Vitis HLS 学习笔记--理解串流Stream(2)

目录 1. 简介 2. 极简的对比 3. 硬件模块的多次触发 4. 进一步探讨 do-while 5. 总结 1. 简介 在这篇博文中《Vitis HLS 学习笔记--AXI_STREAM_TO_MASTER-CSDN博客》,我分享了关于 AXI Stream 接口的实际应用案例。然而,尽管文章中提供了代码示例,对于代码中使用的编码格式并未进行深入探讨。例如,其中使用了 do

Vitis HLS 学习笔记--AXI_STREAM_TO_MASTER

目录 1. 简介 2. 示例 2.1 示例功能介绍 2.2 示例代码 2.3 顶层函数解释 2.4 综合报告(HW Interfaces) 2.5 关于TKEEP和TSTRB 2.6 综合报告(SW I/O Information) 3. 总结 1. 简介 本文通过“<Examples>/Interface/Streaming/axi_stream_to_master

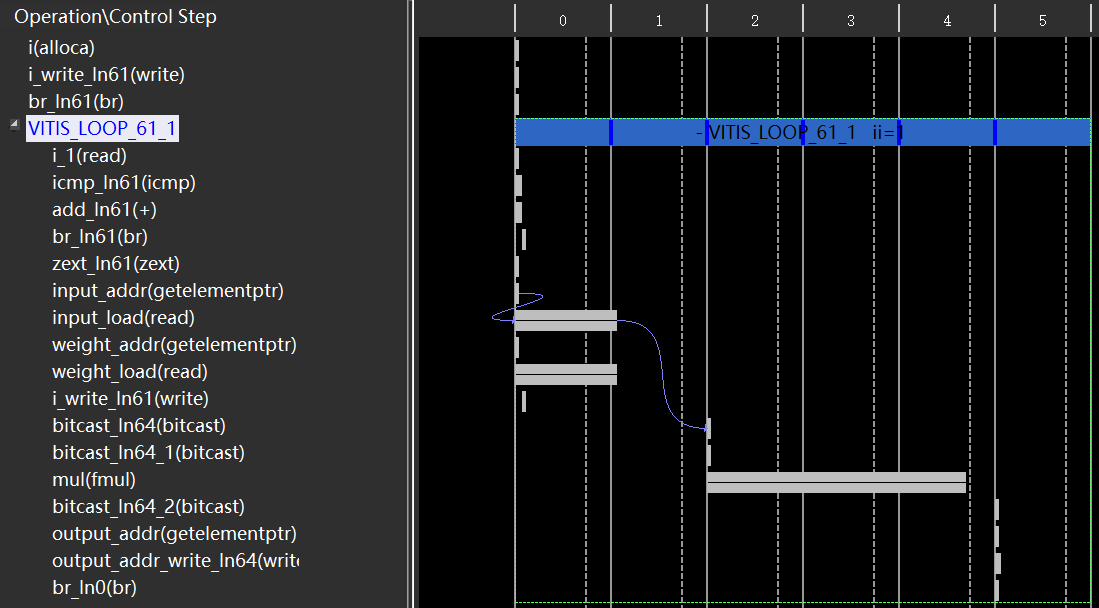

Vitis HLS 学习笔记--HLS流水线基本用法

目录 1. 简介 2. 示例 2.1 对内层循环打拍 2.2 对外层循环打拍 2.3 优化数组访问后打拍 3. 总结 1. 简介 本文介绍pipeline的基本用法。pipeline是一种用于提高硬件设计性能的技术。本文介绍了pipeline在累加计算函数中的应用。通过优化内外层循环和数组访问,显著提高了函数的时序性能,实现更高效的硬件设计。 2. 示例 这个程

Vitis HLS 学习笔记--HLS眼中的完美循环嵌套

目录 1. 简介 2. 示例 2.1 不完美循环 2.2 完美循环 2.3 HLS 眼中的循环 3. 总结 1. 简介 在处理嵌套循环时(HDL或HLS工具中),优化循环结构对于实现最佳性能至关重要。嵌套循环的性能优化直接影响着计算的时延和资源利用率。创建完美嵌套的循环意味着循环结构被设计得紧凑、高效,以最大程度地利用硬件资源和并行计算能力。 在硬件描述或高级综合中,循环

Vitis HLS 学习笔记--MAXI手动控制突发传输

目录 1. 简介 2. MAXI 突发传输详解 2.1 突发传输的前置条件 2.2 hls::burst_maxi 详解 2.2.1 基本知识 2.2.2 hls::burst_maxi 构造函数 2.2.3 hls::burst_maxi 读取方法 2.2.4 hls::burst_maxi 写入方法 2.3 示例一 2.4 示例二 3. 总结 1. 简介 这篇

Vitis HLS 学习笔记--AXI4 主接口

目录 1. 简介 2. 认识MAXI 3. MAXI突发操作 3.1 全局/本地存储器 3.2 MAXI优势与特点 3.3 查看MAXI报告 3.3.1 HW Interfaces 3.3.2 M_AXI Burst Information 3.4 MAXI 资源消耗 4. 理解 Volatile 4.1 标准C/C++中的 volatile 4.2 HLS 中的 vola

Vitis HLS 学习笔记--IDE软件高效操作指引

目录 1. 简介 2. 实用软件操作 2.1 C/RTL Cosimulation 选项 2.2 Do not show this dialog again 2.3 New Solution 2.4 对比 Solution 2.5 以命令行方式运行(windows) 2.6 文本缩放快捷键 2.7 查看和修改快捷键 2.8 将Vitis HLS RTL 导入 Vivado IP

Vitis HLS 学习笔记--C/C++ static 关键字的作用

目录 1. 简介 2. c/c++共有性质 3. c++独有性质 4. 示例说明 5. static 对于 HLS 工具的影响 6. 总结 1. 简介 在Vitis HLS中,偶尔会用到 static 关键字。考虑到Vitis HLS同时兼容C和C++语言,有必要理解这两种语言中static关键字细微差异。本文旨在梳理和总结C与C++中static关键字的具体差别,以便于开

Vitis HLS 学习笔记--Syn Report解读(1)

目录 1. 介绍 2. 示例一 2.1 HLS 代码 2.2 Report 解读 2.2.1 General Information 2.2.2 Timing Estimate 2.2.3 Performance & Resource Estimates 2.2.4 HW interfaces 2.2.4.1 硬件接口报告 2.2.4.2 导出至 Vivado 中的 IP 2