本文主要是介绍TI_DSP_F2808学习笔记3: ePWM,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

共有6组ePWM,每一组 ePWM 模块都包含以下 7 个模块:时基模块 TB、计数比较模块 CC、动作模块 AQ、死区产生模块

DB、PWM 斩波模块 PC、错误联防模块 TZ、时间触发模块 ET。

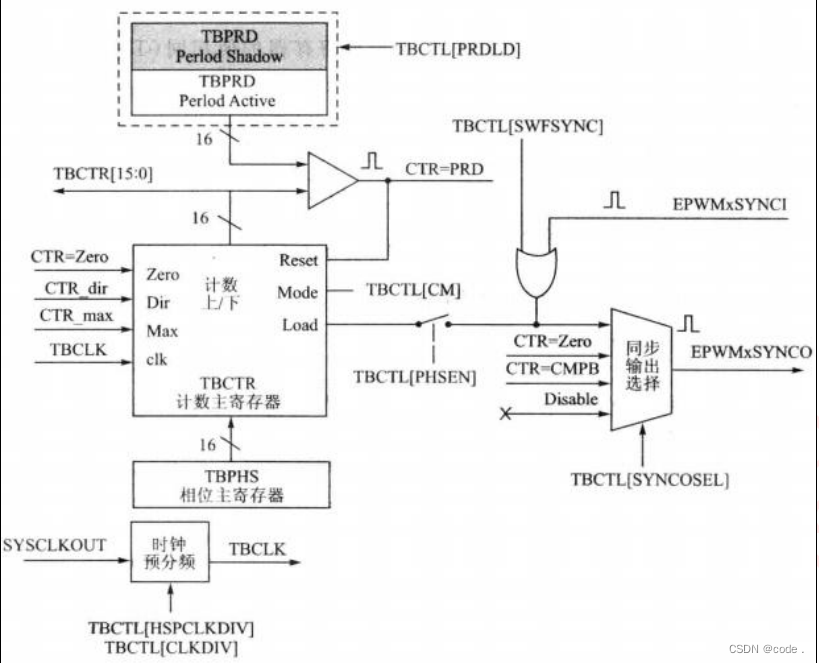

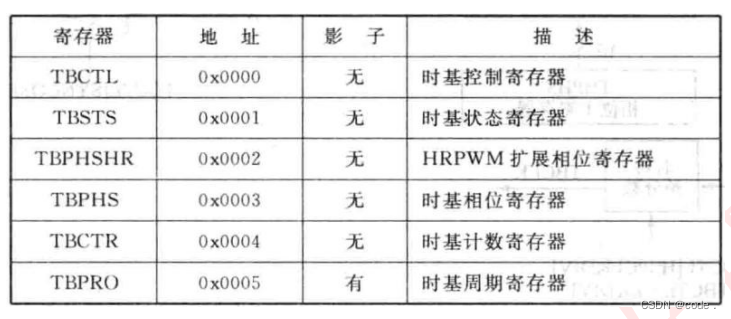

时基模块 TB

确定PWM的周期和相位。

- 1)PWM 时基计数器(TBCTR)

保存当前的计数值。这里面的值会每个时钟信号(系统时钟源SYSCLKOUT经过分频后的TBCLK)修改一次,是增1还是减1,取决于计数模式:- 增计数:TBCTR从0开始,每次增1,到TBPRD(时基周期寄存器值)止,下一次时钟来时复位为0,不断循环

- 减计数:TBCTR从TBPRD开始,每次减1,到0止,下一次时钟来时复位为TBPRD,不断循环

- 增减计数:TBCTR先从0开始,每次增1,到TBPRD后变为减计数,每次减1,减到0后,变为增计数,不断循环

计数模式由TBCTRL设置。

- 2) 同步信号

如果同步信号使能(TBCTL[PHSEN]=1),当有同步信号(同步信号脉冲:ePWMxSYNCI或是软件强制同步信号脉冲:向 TBCTL 的 SWFYNC 位写入 1)进来的时候,TBCTR会加载相位寄存器(TBPHS)中的数值,加载后是继续增计数,还是减计数,要看计数模式:

①向上-向下计数模式(先递增后递减)下:取决于TBCTL[PHSDIR],TBCTL[PHSDIR]=1 表示相位寄存器的值是递增过程中的值,TBCTL[PHSDIR]=0 时表示相位寄存器的值是递减过程中的值。即TBCTL[PHSDIR]=1时,后续在此相位值上开始增计数,反之,则继续减计数。

②向上计数模式(递增)下:不受TBCTL[PHSDIR]影响,后续在相位寄存器的值基础上,递增计数

③向下计数模式(递减)下:不受TBCTL[PHSDIR]影响,后续在相位寄存器的值基础上,递减计数

TBCLKSYNC 位可以被用来同步在一个设备上所有使能的 PWM 模块。该位是系统时钟使能寄存器的一部分。当 TBCLKSYNC=0 时,ePWM 模块时基时钟停止(默认情况),TBCLKSYNC=1 时,所有的 ePWM 模块在 TBCLK 的时钟上升沿到来时同时被启动,为了更好的同步各 ePWM 模块的 TBCLK,每个 ePWM 模块的预分频系统时钟的时基时钟 TBCTL 的寄存器都要设置为相同的值。设置 ePWM 时钟的操作步骤如下:

①使能各 ePWM 模块的时钟。

②设置 TBCLKSYNC=0,停止所有已使能的 ePWM 模块的时基时钟。

③配置预分频值与 ePWM 工作模式。

④设置 TBCLKSYNC=1,启动时基时钟。

- 3)影子寄存器

TBCTL[PRDLD]位可以对 TBPRD 的影子寄存器进行使能或者禁止。当 TBCTL[PRDLD]=0 时,TBPRD 的影子寄存器是使能的,读写 TBPRD 的映射地址的内容时,会读写影子寄存器。时基模块计数器值为 0 时(TBCTR=0x0000),影子寄存器的值传递给活动寄存器。默认情况下,影子寄存器都是有效的。当 TBCTL[PRDLD]=1 时,为立即加载模式,读写时基周期寄存器对应的地址时,都是直接到活动寄存器。

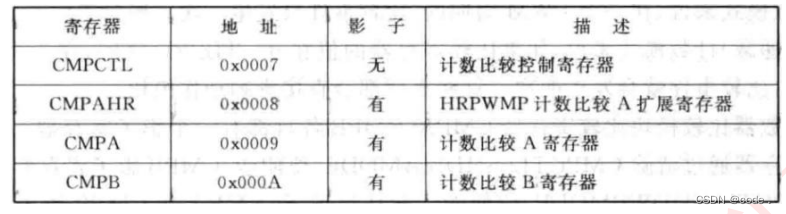

计数比较模块 CC

- 计数器比较模块是以时基计数器的值作为输入,与比较寄存器 CMPA 和比较寄存器 CMPB 不断进行比较,当时基计数器的值等于其中之一时,就会产生相应的事件。对于单向计数模式(向上或者向下),在一个 PWM 周期内,比较事件只发生一次。而对于双向(先递增后递减)计数器模式来说,如果比较寄存器的值在 0-TBPRD 之间,在一个 PWM 周期内,比较事件就会发生两次。

- CMPA、CMPB 各自都有一个影子寄存器。CMPA 影子寄存器通过清除 CMPCTL[SHDWAMODE]位使能,CMPB 影子寄存器通过清零CMPCTL[SHDWAMODE]位使能。默认情况下,CMPA 和 CMPB 影子寄存器是使能的。 影子寄存器被使能的话,CTR=PRD和CTR=ZERO时,影子寄存器的值会传递到有效寄存器中。

动作限定模块 AQ

- (1) 通过时基模块和比较模块,可以产生很多硬件事件:

- 计数回到0:CTR=ZERO

- 计数到PRD:CTR=PRD

- 计数到CMPA:CTR=CMPA (根据计数方向,有两个不同的事件)

- 计数到CMPB:CTR=CMPB (根据计数方向,有两个不同的事件)

在这些事件发生时,PWM输出端口的输出如何变化,取决于动作限定模块 AQ:

- (2) 动作类型

ePWMA 和 ePWMB 输出的几种操作方式如下:

①置高(SET HIGH):使 ePWMA 和 ePWMB 输出高电平。

②置低(CLEAR LOW):使 ePWMA 和 ePWMB 输出低电平。

③取反(TOOGLE):当 ePWMA 或者 ePWMB 当前状态是低电平时,那么下一时刻就是高电平;当 ePWMA 或者 ePWMB 当前状态是高电平时,那么下一时刻就是低电平。

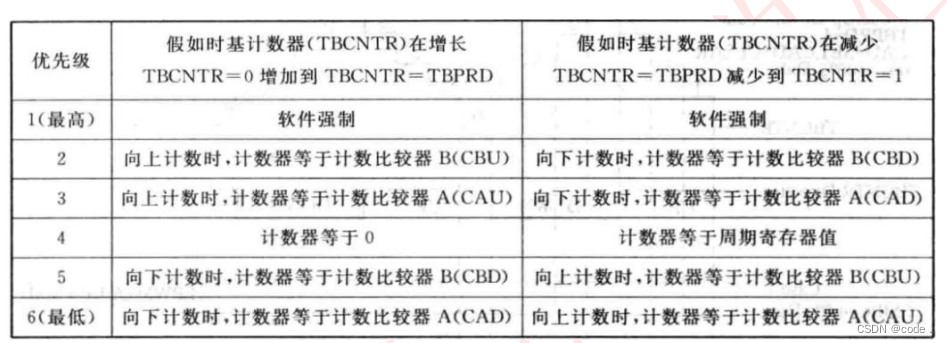

④不动作(DO NOTHING):不对 ePWM 输出做任何改变。但是还是可以产生相应的事件触发信号以及相关中断 - (3) 动作限定模块事件优先级

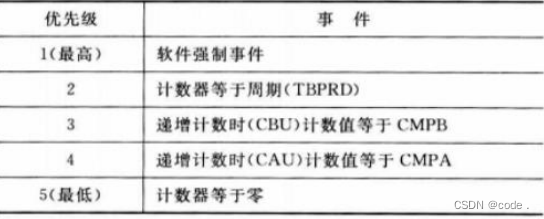

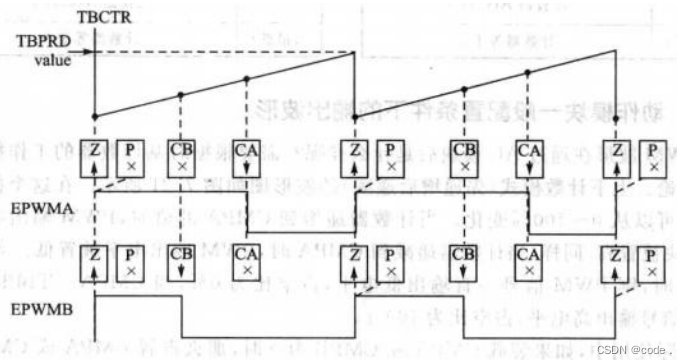

在同一时刻,动作模块可能会收到两个及两个以上的事件时,按优先级相应不同的事件。- 向上向下(先增后减)计数模式的优先级定义如下:

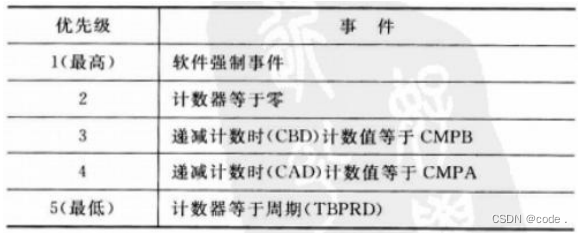

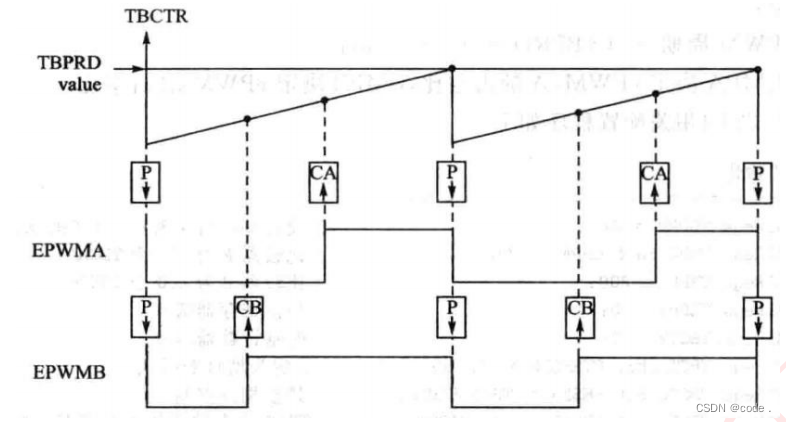

- 向上计数(递增)模式的优先级如下:

- 向下计数(递减)模式的优先级如下:

- 向上向下(先增后减)计数模式的优先级定义如下:

- (4) 举例

EPwm6Regs.TBPRD = tbprd;//设定 PWM 周期为 tbprd+1 个 TBCLK 时钟周期

EPwm6Regs.CMPA.half.CMPA = 350;//比较器 A 的值为 350

EPwm6Regs.CMPB = 200;//比较器 B 的值为 200

EPwm6Regs.TBPHS.half.TBPHS = 0;//相位寄存器清零

EPwm6Regs.TBCTR = 0x0000;//时基计数器清零

EPwm6Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP;//设定为增计数模式

EPwm6Regs.TBCTL.bit.PHSEN = TB_DISABLE;//禁止相位控制

EPwm6Regs.TBCTL.bit.PRDLD = TB_SHADOW;//TBPRD 寄存器采用影子寄存器模式

EPwm1Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_DISABLE;//禁止同步信号

EPwm6Regs.TBCTL.bit.HSPCLKDIV=TB_DIV1;//设定 TBCLK=SYSCLK 时基时钟= 系统时钟

EPwm6Regs.TBCTL.bit.CLKDIV=TB_DIV1;

EPwm6Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;//设定 CMPA 为影子寄存器模式

EPwm6Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm6Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;//在 CTR=Zero 时装载

EPwm6Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

EPwm6Regs.AQCTLA.bit.ZRO = AQ_SET;//CTR=ZERO 时,将 ePWM6A 置高

EPwm6Regs.AQCTLA.bit.CAU = AQ_CLEAR;//CTR=CAU 时,将 ePWM6A 置低

EPwm6Regs.AQCTLB.bit.ZRO = AQ_SET;//CTR=ZERO 时,将 ePWM6B 置高

EPwm6Regs.AQCTLB.bit.CBU = AQ_CLEAR;//CTR=CAU 时,将 ePWM6B 置低

EPwm6Regs.CMPA.half.CMPA = Duty1A;//调整 ePWM6A 的占空比

EPwm6Regs.CMPB = Duty1B;//调整 ePWM6B 的占空比

EPwm6Regs.AQCTLA.bit.PRD = AQ_CLEAR;//CTR=PRD 时,将 ePWM6A 置低

EPwm6Regs.AQCTLA.bit.CAU = AQ_SET;//CTR=CAU 时,将 ePWM6A 置高

EPwm6Regs.AQCTLB.bit.PRD = AQ_CLEAR;//CTR=PRD 时,将 ePWM6B 置低

EPwm6Regs.AQCTLB.bit.CBU = AQ_SET;//CTR=CAU 时,将 ePWM6B 置高

这篇关于TI_DSP_F2808学习笔记3: ePWM的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!