drc专题

关于音频EQ、DRC、等响度、3D环绕音、虚拟低音、变音、AEC、AGC、ANS等解释

1.EQ: EQ是均衡器的缩写。它的基本作用是通过对声音某一个或多个频段进行增益或衰减,达到调整音色的目的。当然,EQ还有一个显著的功能,降噪。EQ通常包括如下参数:F(requency),频率――这是用于设定你要进行调整的频率点用的参数;G(ain),增益――用于调整在你设定好的F值上进行增益或衰减的参数;Q(uantize)――用于设定你要进行增益或衰减的频段 “宽度”。 2.DRC(动态

AD10的DRC检查

PCB布线完毕后文件输出到打印机之前,还有一步关键的操作要完成:完整的设计规则检查,Design Rule Check简称DRC。在菜单栏Tools\Design Rule Checker。点进去之后弹出一个设计规则检查器对话框。里面包含的检查内容有:导线宽度、元件之间的间距,安全距离,过孔的类型等等。 报告设置: sub-net destals是对网络连接关系进行检查并生成报告····

电路笔记 : 嘉立创EDA 导入、查找、设计管理器(快速寻找网络标签)功能+DRC错误检查和处理

导入功能 查找功能 可查找多种类型,如原件名称、网络标签等 设计管理器 图层查看 DRC错误 规则设置 线距问题 大多数PCB制造商能够可靠地生产5 mil间距的走线和间隙。这是一个常见的标准,适合大多数消费级和工业级电子产品。在5 mil以上的间距,制造商可以确保线路的完整性和一致性。 合理的线间距有助于减少信号串扰(cross-talk)和电磁干扰

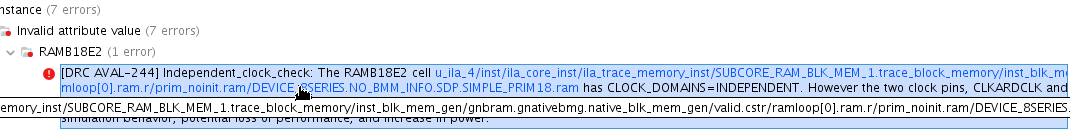

vivado bit生成报 DRC AVAL-244

经常在添加Debug Core ILA 后会遇到这个问题,字面意思就是说“这个调试ram需要独立的时钟CLKARDCLK和CLKBRWCLK,但实际DRC时发现这两个时钟是一样的。”虽然不太明白,但可以看到问题定位在u_ila_4模块,打开debug页面,确认下u_ila_4模块所用的采样时钟。 第一步:先把Messages的Critial waring/Warning过一遍,把代码里的b

Altium Designer 22 DRC规则检查解析(转载)

原文链接:Altium Designer 22 DRC规则检查解析 - 哔哩哔哩 (bilibili.com) PCB Designer Rules 即用来约束PCB走线或布局的规则条例。通常有如,PCB板厂所提供给你的最小线宽线距参数、最小字符宽高度、最小VIA&PAD内外径参数等,需要设计遵守的,否则会导致产品生产困难(乃至无法生产)或不良率的增加;约束条款即称为PCB Designer R

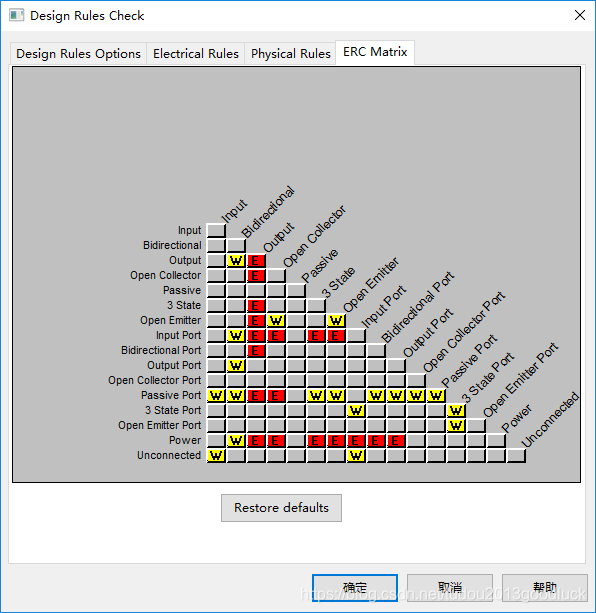

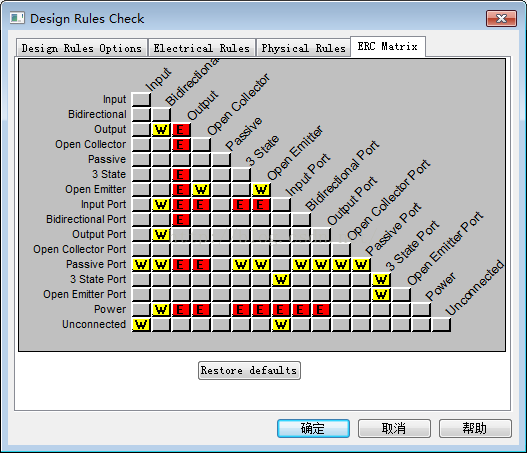

ORCAD16.6中原理图DRC检查(下)

接ORCAD16.6中原理图DRC检查(上) 上次说了电气规则,下面接着说物理规则。 参考了http://blog.sina.com.cn/s/blog_e0ae98f10101fhg1.html; 5、物理规则 check power pin visible——检查电源引脚可视性; check missing pin number——检查是否有丢失的Pin numbers

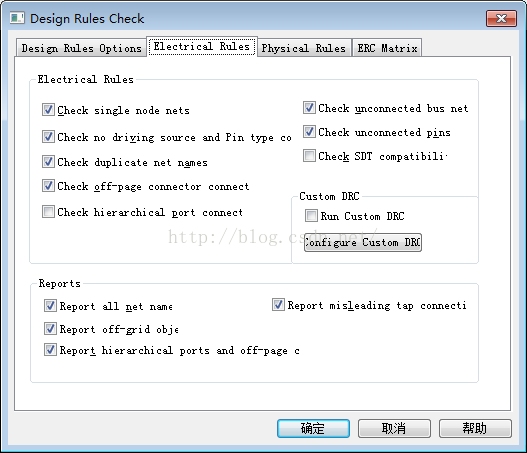

ORCAD16.6中原理图DRC检查(上)

在做原理图的时候,差点犯了个致命问题,本该是同一网络的net,结果两边的net名字不一致,幸好被领导发现了,要不然就报废了。 于是乎就去折腾下 DRC 检查的功能,以前也没用过。 好了打开 DRC 检查的菜单步骤: 1、打开 ORCAD 软件,先选中整个 dsn 文件; 2、在Tools中点击Design Rules Check; 3、打开显示界面 ①Scope:范围,是检查整

Allegro消除元件本身的引脚间距过小造成的DRC错误

1.元件自身引脚间距过小,DRC报错 2.Edit->property或shift+F2选中元件 3.为元件添加Nodrc_Sym_Same_Pin属性 4.添加结束后,DRC错误消失

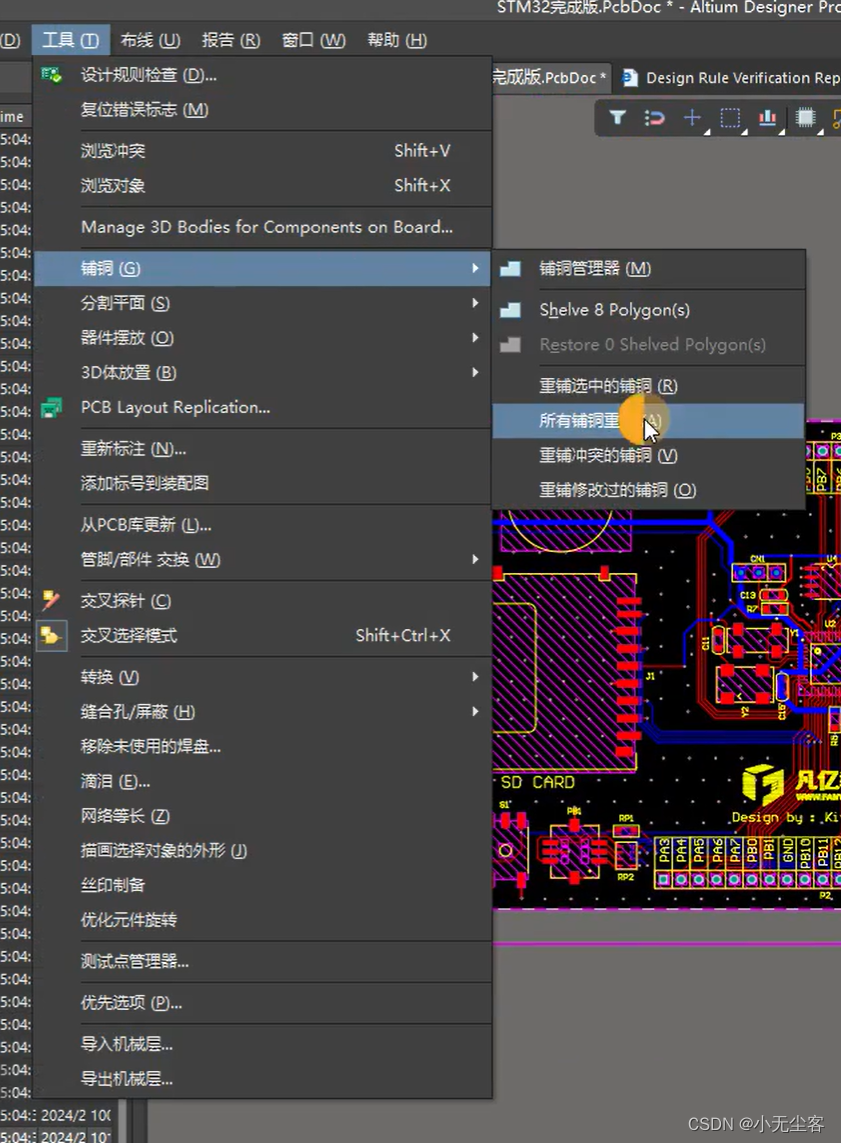

AD24-PCB的DRC电气性能检查

1、 2、如果报错器件选中,不能跳转时,按下图设置 3、开始出现以下提示时处理 4、到后期,错误改得差不多的时候;出现以下的处理步骤 ①将顶层和底层铜皮选中,移动200mm ②执行以下操作 ③将铜皮在移动回来,进行重新铺铜;再次进行DRC检查即可

【Vivado常见问题】【DRC NSTD-1 DRC UCIO-1】无法生成bitstream(部分管脚位置或电平未指定)

假如工程就是有些信号暂时没法指定管脚呢,比如顶层设计端口包含串口,LED、按键,此时只想验证按键和串口,LED由于当前硬件限制没有对应的物理电路,没法确定管脚。这种情况可以使用一句脚本语言来暂时忽略该限制。 set_property SEVERITY {Warning} [get_drc_checks NSTD-1]set_property SEVERITY {Warning} [get_dr

ICV:signoff_check_drc脚本

更多学习内容请关注「拾陆楼」知识星球 拾陆楼知识星球入口 往期文章链接: ICV:metal fill insertion流程 ICV:metal fill insertion脚本

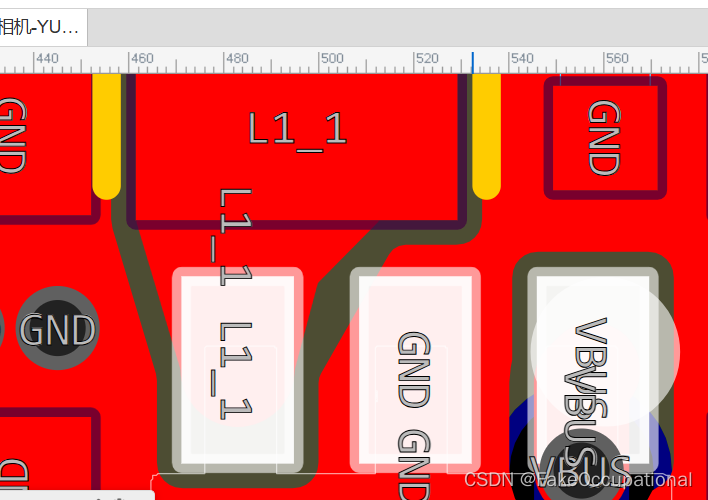

【立创EDA-PCB设计基础完结】7.DRC设计规则检查+优化与丝印调整+打样与PCB生产进度跟踪

前言:本文为PCB设计基础的最后一讲,在本专栏中【立创EDA-PCB设计基础】前面已经将所有网络布线铺铜好了,接下来进行DRC设计规则检查+优化与丝印调整+打样与PCB生产进度跟踪 目录 1.DRC设计规则检查 2.优化与丝印调整 1.过孔连接优化 2.泪滴优化 3.元件名称丝印调整 4.导入图片 3.打样与PCB生产进度跟踪 1.DRC设计规则检查 与本专栏中前面进行

海思AQ工具HiAQTools调试三 DRC曲线

其他流程: 海思AQ工具HiAQTools调试一 声音曲线 海思AQ工具HiAQTools调试二 声音增益 海思AQ工具HiAQTools调试四 串口调试 调试DRC曲线前,此步骤必须先确认调整好声音曲线和增益。 DRC是什么? Dynamic Range Control,动态范围控制。其作用是限制,最大输出功率,防止输出功率过高而导致耳机喇叭烧坏。 一、准备工具 1.串口工具 用于将电视

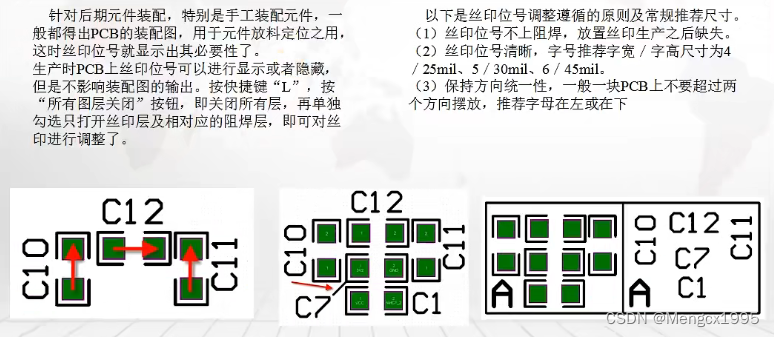

第34课 DRC的检查及丝印的调整

菜单栏设计----规则检查 把检查项里的电气规则全部勾选上,运行DRC。 这时会弹出一个警告信息,这时重新对所有的铜皮进行重新铺铜在运行就不会出现了。 出现的错误信息可以在Panel----Message中打开,双击可以定位到错误的位置。 对于丝印的尺寸和摆放遵循以下的原则。 在进行丝印摆放的时候,按L建把其他层全部关闭,只留下丝印层和阻焊层进行摆放。 可以把器件位置

在vivado中GTP GTH GTZ使用GTGREFCLK时 Vivado_DRC: (REQP-52) 或Vivado_DRC: (REQP-49)错误解决办法

本文首发于hifpga.com XILINX的手册上明确指出了可以用于测试目的使用GTGREFCLK(实际上量产中也有人这么用,通常是为了省差分晶振,或者是没有频率合适的差分晶振,这么用当然是有一些前提的否则量产翻车怪自己咯,FPGA就是这样,没有什么绝对可行或绝对不可行)。 可是当你真的使用的时候你就发现用常规编译是没法通过的。 首先在run implment 布局布线的时候就会出现Viv

cadence virtuoso layout drc error

For 0.11um design, 2.5/3.3V transistor channel (overlap of Poly and AA) enclosure by DG.( Designer can waive this rule for 0.13um design).>=0.30 对于 0.11 微米的设计,2.5/3.3V 晶体管通道(Poly 和 AA 的重叠部分)由 DG 封装(对

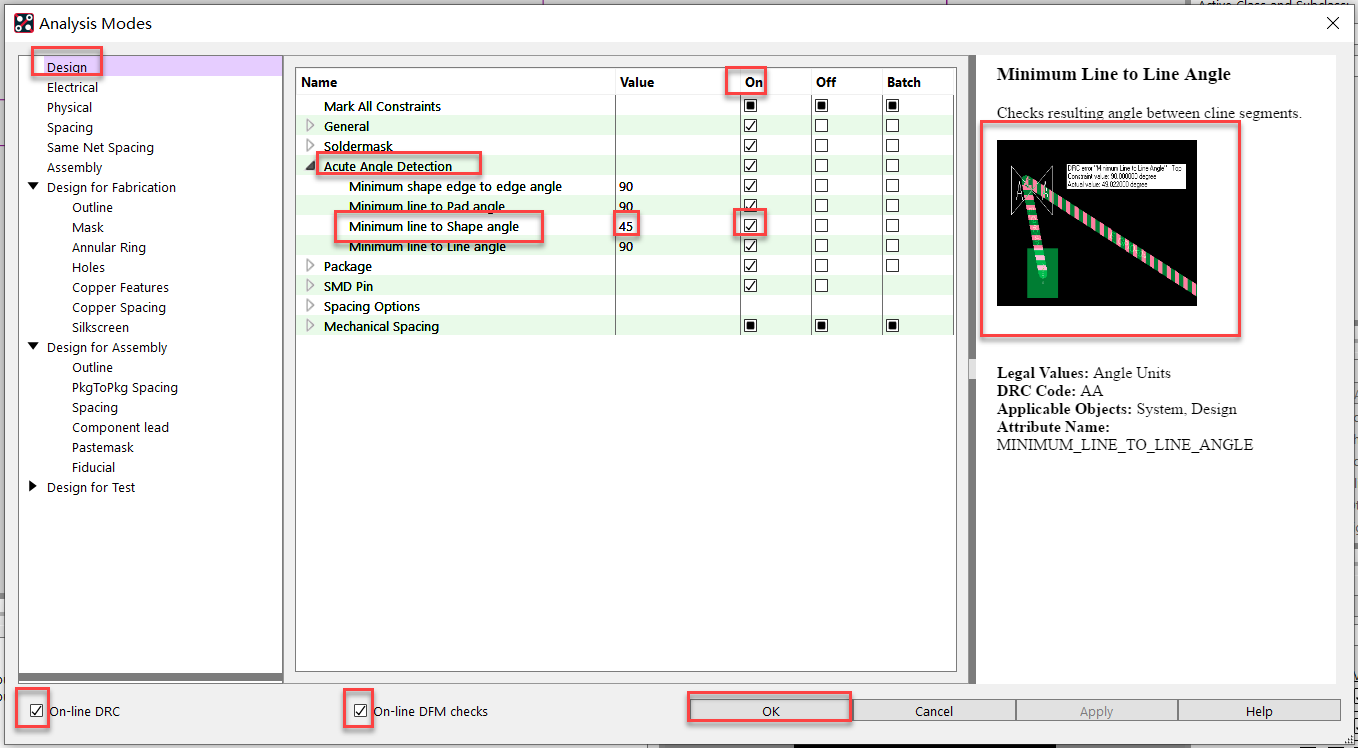

cadence SPB17.4 - allegro - DRC - Minimum Line to Shape Angle

前言 铺地铜之前, DRC是没问题的. 铺地铜之后, 出现 DRC错误 Minimum Line to Shape Angle 例子如下: Constraint NameDRC Marker LocationRequired ValueActual ValueConstraint SourceConstraint Source TypeElement 1Element 2Minimum Lin