本文主要是介绍cadence virtuoso layout drc error,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

For 0.11um design, 2.5/3.3V transistor channel (overlap of Poly and AA) enclosure by DG.( Designer can waive this rule for 0.13um design).>=0.30

对于 0.11 微米的设计,2.5/3.3V 晶体管通道(Poly 和 AA 的重叠部分)由 DG 封装(对于 0.13 微米的设计,设计人员可以放弃这一规则)。

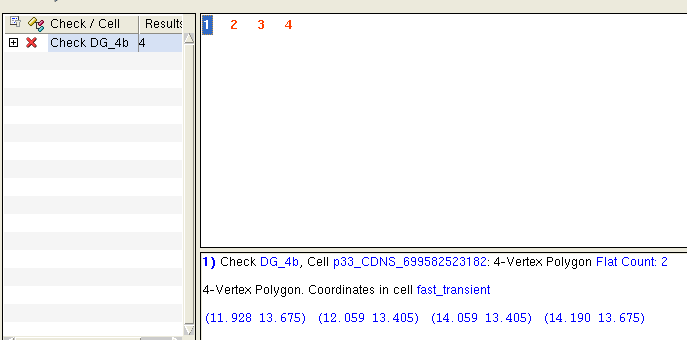

双击报错的时候发现报错的位置没有任何问题。

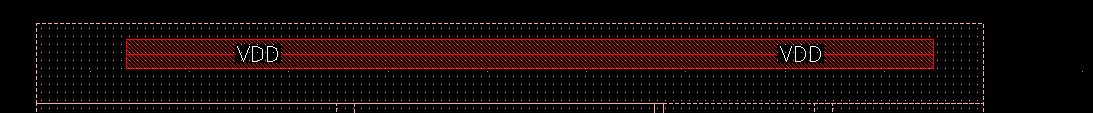

解决办法:用DG层把所有AA层覆盖。

这篇关于cadence virtuoso layout drc error的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!