virtuoso专题

【virtuoso】INV 原理图+前仿真 + 版图 + 后仿真

采用SMIC工艺,不同工艺版图窗口可能有差异 1. 原理图&前仿真 1.1 绘制原理图 PMOS: NMOS宽长比2:1 PMOS开启导通电阻大一点,这样设置,可以使得阈值电压是VDD/2 按 i,可以插入器件按p,可以放置端口 1.2 创建symbol create --> Cellview --> From Cellview 直接ok即可

分享 | 使用Virtuoso VCPVSR工具基于标准单元的布局布线流程

本节内容 · 导览 一、准备工作 二、运行VCP前的配置 三、VCP的布局规划 四、VCP的自动摆放 五、VSR的自动绕线 分享使用Virtuoso GXL Custom Digital Placer(VCP) & Space-based Router(VSR)工具进行基于纯数字Sta

react-table,react-window,react-virtuoso

react-table: 优点: 它有一个无头 API,可以与 React-table 无缝协作。 高效性能和动态高度。 为动态高度提供本机支持,无需手动测量行高。 缺点: 每次滚动时重新渲染表格组件。如果同一渲染函数中除了表格之外还有其他组件,这可能会有问题。 react-window: 优点: 轻量级库。 有据可查。 缺点: 缺乏无头 API。渲染 div 元素,与 react-table

Cadence virtuoso 原理图 器件及连接都为黄色

使用tsmc65nm工艺库发现原理图器件及连接都显示黄色 解决办法:用工艺库下的display.drf文件替换工作目录下的display.drf文件(建议将原来的display.drf文件备份) 重新启动virtuoso,显示正常

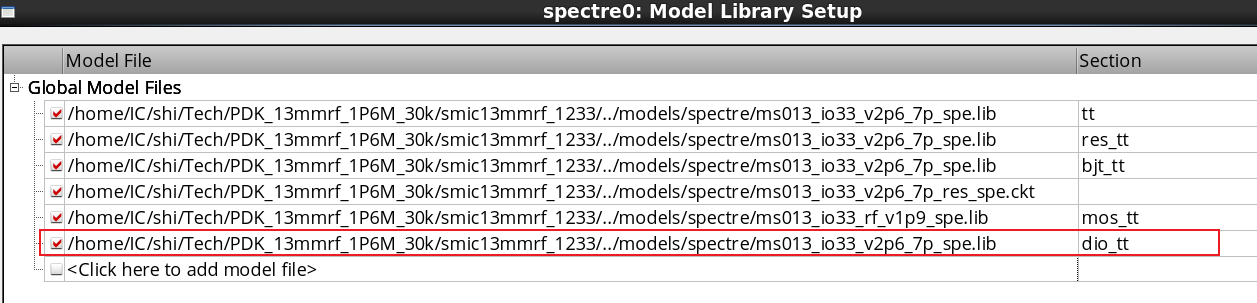

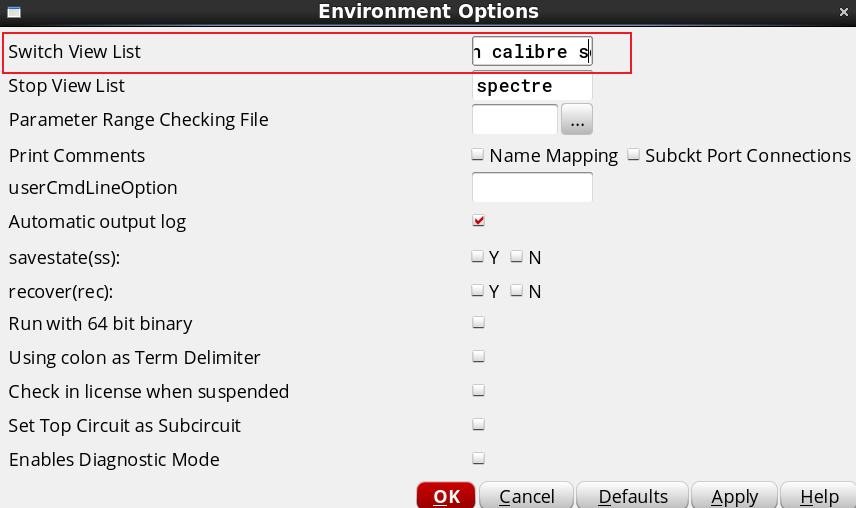

virtuoso 后仿 ADE L error

ADE后仿时出现error ERROR (SFE-23): "input.scs" 299: The instance `_57_D32_noxref' is referencing an undefined model or subcircuit, `parasitic_nwd'. Either include the file containing the definition of `p

Cadence Virtuoso ADE_XL 仿真初使用(基于Cadence 617)

Cadence Virtuoso ADE_XL 仿真初使用(基于Cadence 617) 在进行virtuoso仿真时,为满足电路的设计指标,难免会在多个工艺角和PVT条件下仿真,用ADE_L又麻烦又慢,ADE_XL完美解决问题! 下面以两级运放为例,讲述使用方式。 初探ADE_XL Cadence Virtuoso ADE_XL 仿真初使用(基于Cadence 617) 1.仿真设置2.

Virtuoso仿真效率大幅提升,究竟做对了什么?

这是我们EDA云实证的第四期。 本期实证的主角是——Virtuoso。 半导体行业中使用范围最广的EDA应用之一。 1991年Virtuoso技术正式发布,最初作为掩模设计师的版图工具,是Opus平台的一部分,主要功能包括电路设计与仿真、版图设计、设计验证,以及模拟/数字混合设计等。 近30年来,Virtuoso产品已和最初有很大不同,但其核心仍然是版图编辑器。 应用工具层面。Cadence一

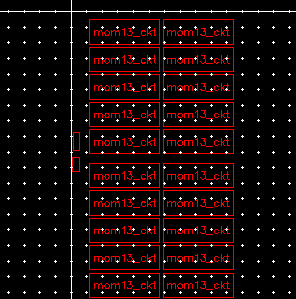

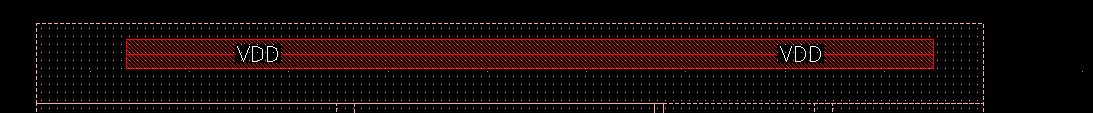

virtuoso layout版图设计 调用器件

在设计好一个电路之后,需要对其进行版图设计。 在原理图界面点击 点击ok 库和名字要跟原理图名字一致,一般自动就命名好了,点击ok 出现版图界面,点击左下角的图标。 选择要不要生成boundary 选择layer,一般为M1,点击creat label as,点击options 这里选择label的高度,我选择的是0.2,下面两个勾选same as pin

【模拟集成电路】Virtuoso如何设置画斜线与更换颜色

文章目录 如图所示,我们需要画出这样的斜线 操作步骤如下:按下快捷键W,如图所示,把full改成direct。这样就可以更改走线形式了。同时,也可以在这里更改线的颜色。

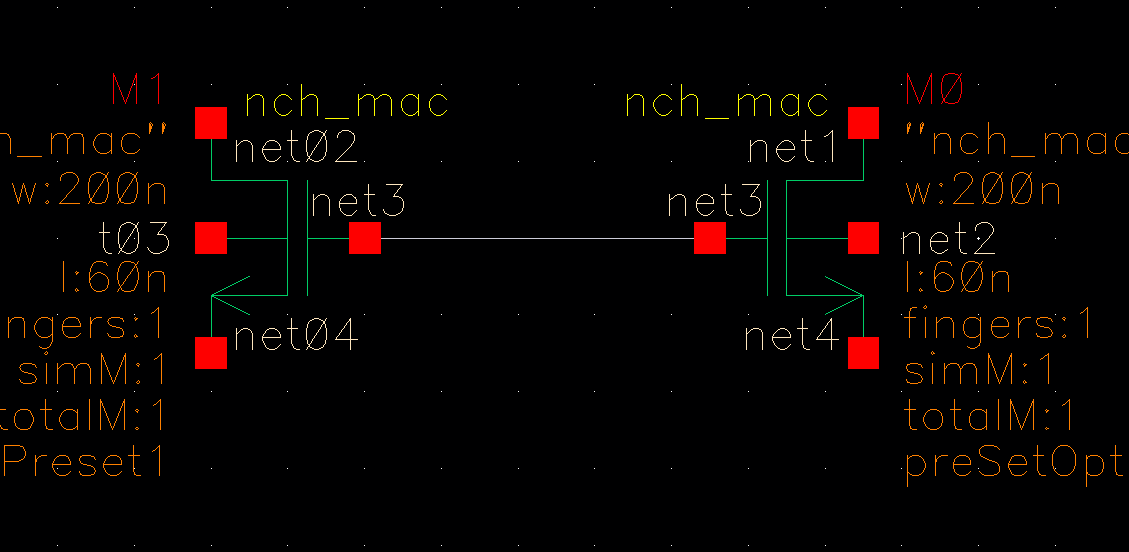

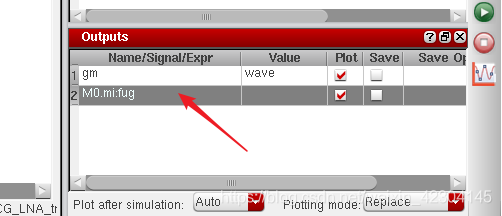

在virtuoso中查看晶体管参数曲线

在virtuoso中查看晶体管参数曲线 晶体管参数曲线查看方式打开AED环境,加载state,进行dc仿真,找到tools,点击results browser在路径框里找dcOplnfo,选中想看的晶体管,找到mi,下面就由它的各个参数,右键点击calculator,其公式就在caculator里显示出来了然后再ADE窗口的result中添加这时候如果只显示一个点,也就是其gm值然后可以在t

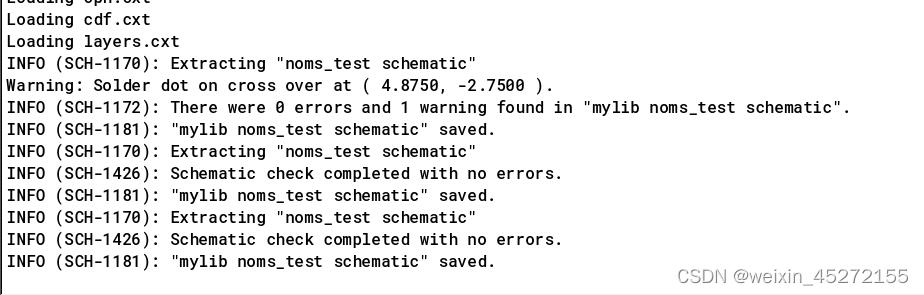

cadence virtuoso PEX 寄生参数提取及后仿真

寄生参数提取 加载xrc文件,在这个工艺库中这个规则文件是在LVS文件夹中 加载H-Cells文件和X-Cells文件 调出PEX options窗口 在Ground node name输入原理图中的地线名称 (如果这里无法输入,请参考:Cadence virtuoso drc lvs pex 无法输入-CSDN博客) 点击run PEX Cell

virtuoso 后仿 ADE L error

ADE后仿时出现error ERROR (SFE-23): "input.scs" 299: The instance `_57_D32_noxref' is referencing an undefined model or subcircuit, `parasitic_nwd'. Either include the file containing the definition of `p

cadence virtuoso layout drc error

For 0.11um design, 2.5/3.3V transistor channel (overlap of Poly and AA) enclosure by DG.( Designer can waive this rule for 0.13um design).>=0.30 对于 0.11 微米的设计,2.5/3.3V 晶体管通道(Poly 和 AA 的重叠部分)由 DG 封装(对

用Virtuoso和Abstract完成gds2lef

需要用到的工具有virtuoso和abstract。 数模混合的项目通常需要模拟完成模块设计,把接去数字的pin打上label(text),数字的floorplan才能正式开始。 如果只需要简单的数字PR boundary和pin点位置,那么只使用virtuoso就够了,还想把模拟版图都转成lef就要用到abstract工具。 1.PR boundary+pin

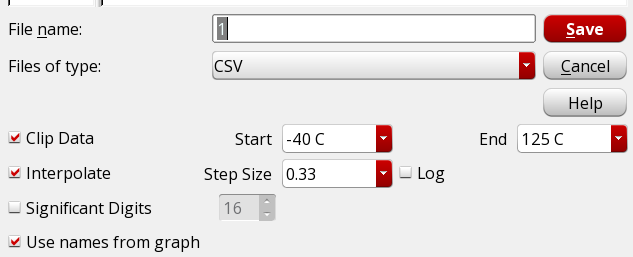

Cadence virtuoso 导出vcsv文件无反应

问题:右击仿真曲线,send to export,save后无反应,没有数据输出 解决办法: 右击仿真曲线,send to-table-append 点击 file-export后save

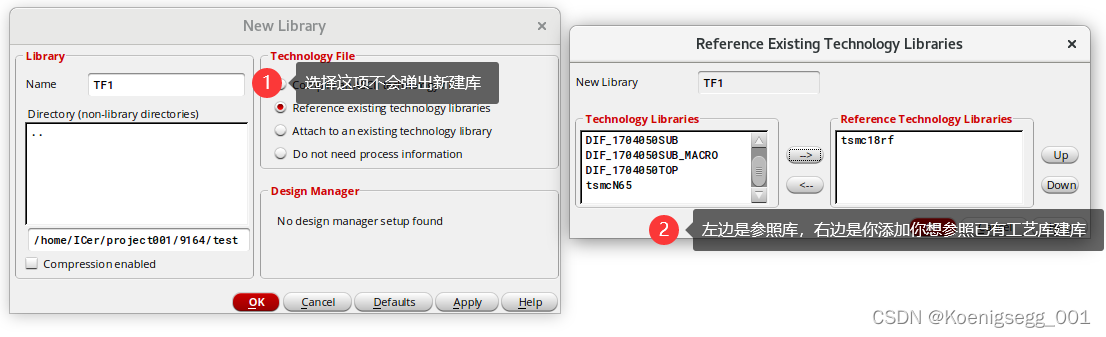

Cadence(virtuoso)集成电路设计软件基本操作——建库的两种方法

Cadence(virtuoso)集成电路设计软件基本操作——建库的两种方法 学习目标 如何在cadence中建立设计库建库的具体步骤及各步骤作用 建立库菜单 参照新工艺文件建立库 Compile an ASCII technology file Reference existing technology libraries Attach to an existing

初步认识Cadence Virtuoso IC617

目录 前言开发环境Linux平台搭建工艺库 软件的使用启动虚拟机Cadence Virtuoso IC 软件的使用创建一个自己的工作目录启动软件添加库新建设计库自建库与工艺库绑定新建原理图 前言 Cadence是一家专门提供电子自动化设计(EDA)软件的厂商,该公司开发的很多软件被广泛应用,cadence virtuoso IC 集成电路中常用的软件之一,如果想要学习集成电路

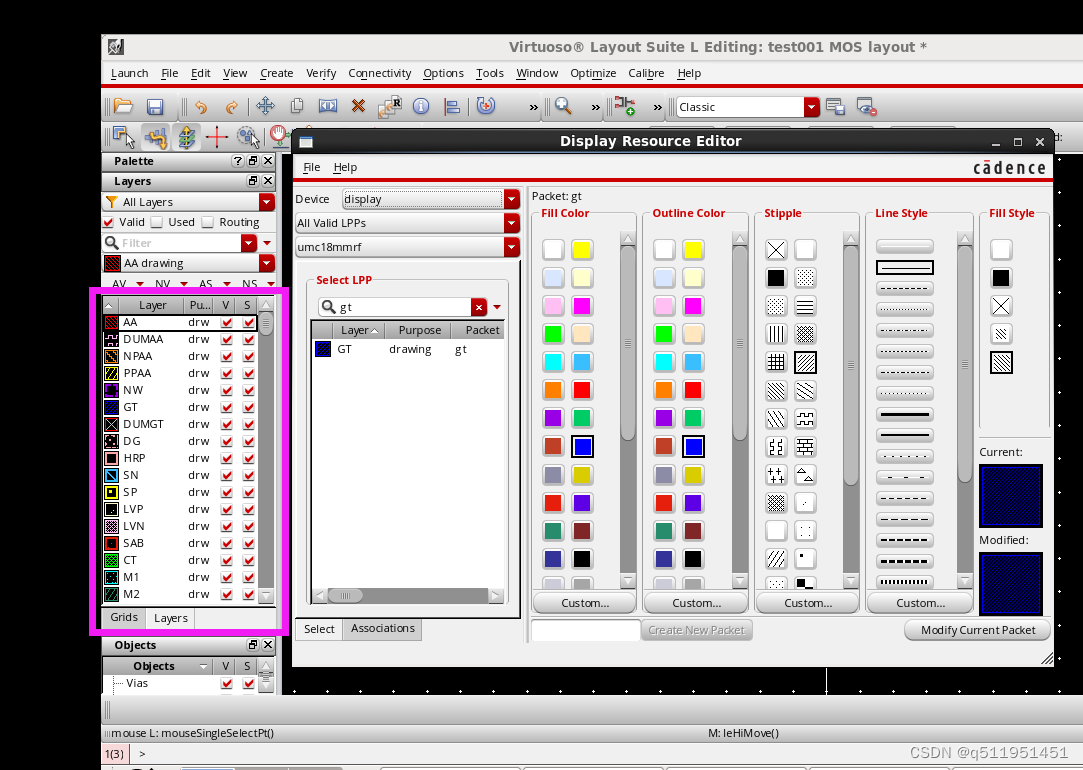

版图设计工具解析-virtuoso的display.drf文件解析

1. display.drf文件解析 virtuoso的版图颜色定义分析 下图为virtuoso的版图颜色,包括填充,轮廓,彩点,线形 本文以smic18mmrf的display.drf文件进行解析 smic18的PDK包下存在display.drf文件 打开文件display.drf文件后看到如下内容 1. 颜色定义模块 采用了RGB格式定义了颜色变量 2.

gds/网表导入virtuoso注意事项

我正在「拾陆楼」和朋友们讨论有趣的话题,你⼀起来吧?拾陆楼知识星球入口 gds和网表导入到virtuoso中都需要添加参考库,这里需要注意的是如果上层模块/顶层调用下层模块时参考库时,需要把library中的模块cell的单独copy到新的库中,模块的via layout或module schematic和symbol不需要被顶层参考,因为后续更新模块的layout或schematic可