cadence专题

Cadence导出Excel格式的BOM

1.选中需要导BOM的原理图(.dsn文件)。 2.点击工具栏Tools,再点击Bill of Materials。 3.勾选Open in Excel,Header:填写Item\tQuantity\tReference\tPart\tpcb footprint, Combined property string填写{Item}\t{Quantity}\t{Reference}\t{Val

Cadence高速板设计技巧(全志H3)[四]

HDMI常用的ESD器件: 可以看到一个器件可以做两路差分线的TVS防护: 按W键移动会把导线直接移走,这样显然是不行的: cadence中导线调节用的是快捷键e: 因此,虽然在某些场合下 eMMC 被称为 ROM,但从技术和功能角度来看,eMMC 并不属于传统意义上的 ROM,而是一种可读写的闪存存储器。 BUCK电路的三个重要回路:输入回路,输出回路,反馈

cadence ncelab的nonotifier意义

cdnshelp 去搜索关键词“notifier”,就可以了。 大体意思是标准单元库里的时序检查,如果发生时序违反,会使得notifier改变原有值(默认是x值)。如果notifier值发生变化,就会在触发器的输出端口上产生一拍不定态。 也就是说ncelab的-nonotifier,是关掉时序检查产生不定态的功能。

lec(logic equivalence check)--cadence 等价性检查工具理解

文章目录 1. lec是独立的,不基于任何指定的综合工具。key point mappingummapped points有三类 formal functional comparison algorithms两种comparison方式 2. setup mode 和 lec mode3. blackboxsetreport 4. unreachable key points设置选项,尽量避

探索未来科技:Cadence 2024技术研讨会

随着电子系统日益复杂和微型化,单一物理学领域的分析已无法满足对系统整体性能的准确评估需求。系统级多物理场分析通过集成多个物理学领域(如信号、电源、热、电磁等),能够全面捕获不同物理场间的相互影响,从而对系统整体性能进行更加准确的预测和优化。 AI技术在多物理场分析中扮演着越来越重要的角色。Cadence Optimality 工具使用机器学习AI算法,可自动执行多物理场协同分析,快速高效地探索

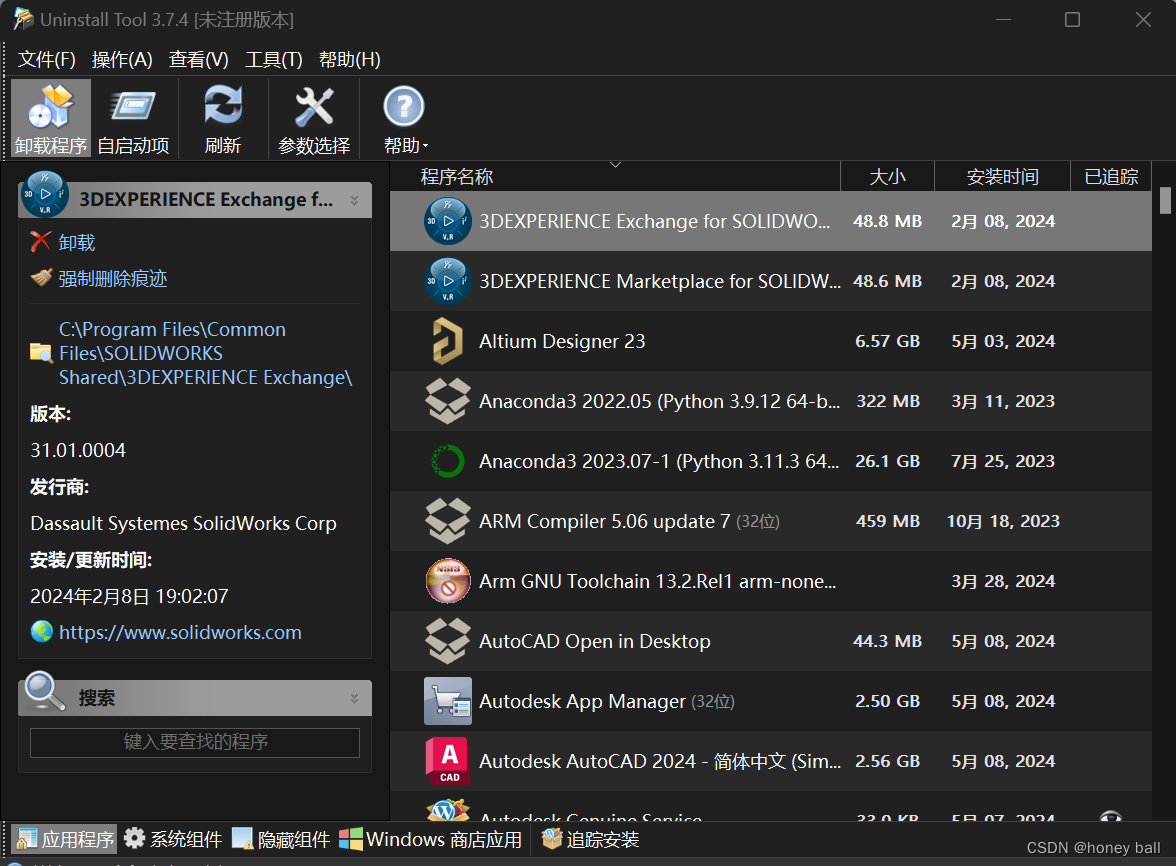

如何彻底将CAD或者Cadence卸载干净

最近因为升级软件需要先彻底删除这两个软件,发现无论如何都不能卸载干净,于是乎找到这样一个软件帮助卸载或查找剩余的软件残留: 官网:https://geekuninstaller.com 支持软件和 UWP 应用的卸载,查看软件注册表和安装目录等。 右键选择程序 -> 强制卸载,即可自动卸载软件并扫描相关残留文件。 但是完全消除注册表收费,可以右键打开注册表手动卸载,这个卸载软件提供了这些

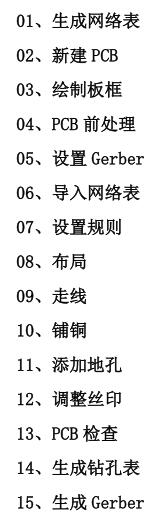

Cadence Allegro基本学习流程的思维导图

Cadence 是一个大型的,强大的EDA 软件,它几乎可以完成电子设计的方方面面,包括ASIC 设计、FPGA 设计和PCB 板设计。Cadence 在原理图仿真、电路图设计、自动布局布线、EMC仿真等方面有着绝对的优势。目前出名的电子厂商,大部分是使用Cadence做设计开发。想入门学习Cadence,不如先通过本思维导图,让学习更有思路。

【chatGPT】我:在Cadence Genus软件中,出现如下问题:......【4】

我 在Cadence Genus中,tcl代码为:foreach clk $clk_list{ set clkName [lindex $clk_list 0] set targetFreq [lindex $clk_list 1] set uncSynth [lindex $clk_list 4] set clkPeriod [lindex “%.3f” [expr 1 / $target

Cadence建立PCB步骤

1、打开PCB Editor-》Allegro PCB Design GXL 2、File-》New 其中Board(wizard)为向导建立PCB File-》Save As 更改PCB存放路径 3、Setup-》Design Parameter… 分别设置使用单位、图纸尺寸、单位精度、工作区域(其中Left X和Lower Y表示左下角坐标,设置为负值使坐标原点

cadence布局布线常见问题详解

cadence布局布线常见问题详解 1.怎样建立自己的元件库? 建立了一个新的project后,画原理图的第一步就是先建立自己所需要的库,所采用的工具就是part developer. 首先在建立一个存放元件库的目录(如mylib),然后用写字板打开cds.lib,定义:Define mylib d:\board\mylib(目录所在路径). 这样就建立了自己的库。在Concept_HDL的c

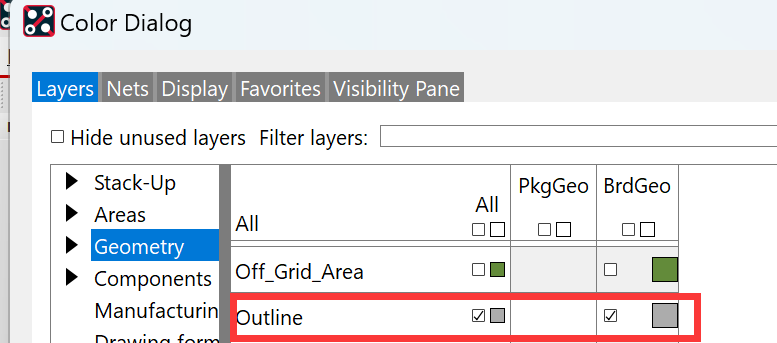

【Cadence Allegro】如何创建光绘层

我们将Netlists网表导入到PCB板框,并把元器件大致放置到板框后,建议首先先将布线相关的一些光绘层给创建出来以便于我们后面布局布线。 首先,菜单栏【Display】→【Color/Visibility...】,将所有层全部关闭显示(如下图)。 一、创建PCB走线光绘层 菜单栏【Display】→【Color/Visibility.

*WARNING* LSF has been configured to use Linux control groups; however, the Cadence daemon starter h

问题描述: WARNING LSF has been configured to use Linux control groups; however, the Cadence daemon starter has not been configured. 该问题会导致JOB跑完,但bjobs查看时还显示RUN的状态。 解决方法: 将LSF的CGROUP关闭,参考链接1。 参考资料: ht

几个有用的cadence网站

1.Introduction to Functional Coverage Rapid Adoption Kit (RAK) (cadence.com) https://support.cadence.com/apex/ArticleAttachmentPortal?id=a1O3w00000AE7ObEAL&pageName=ArticleContenthttps://support.cade

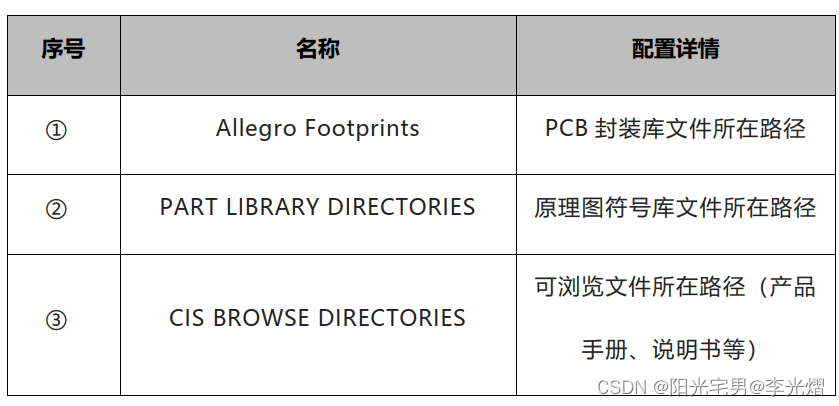

【原理图PCB专题】Cadence 17.4 配置Capture.ini让CIS数据库界面查看PCB封装

在CIS数据库中,如果进行了正确配置是可以查看原理图符号库与PCB封装库的。如下所示: 看到封装库的意义在于一个原理图封装是可以对应多个PCB封装的,如同一个原理图座子,对应了侧插或是竖插,那在没有PCB封装的时候,我们只能通过去看详细资料来判断。如果有PCB封装显示,只要我们了解封装,那就可以一下就知道是什么样的座子了。所以如果有PCB封装我们就能更一目了然了。

Cadence OrCAD使用小技巧

Cadence是公司名,Allegro(俗称阿狸狗)是该公司旗下的EDA工具品牌,OrCAD是该公司收购公司的EDA工具品牌。 OrCAD这个产品线是Cadence收购来的,Allegro才是嫡系。 注意:dsn不能放在中文路径下。 开机选capture and cis CIS:Component Information System,元件信息系统,含有元件库管理之功能。

Cadence 17.4 PCB操作记录

文章目录 画板子边框设置路径导入网表WARNING(SPMHNI-192).WARNING(SPMHNI-194)ERROR(SPMHNI-196)WARNING(SPMHNI-337)Fix/Unfix设置元件高度刷新焊盘修改并更新封装隐藏某一层对齐元件打过孔铺铜连接方式PCB翻转设置旋转快捷键开窗allegro统一更改丝印字体大小走线部分删除蓝色三角形错误负片层网络分割查看布线或者DRC

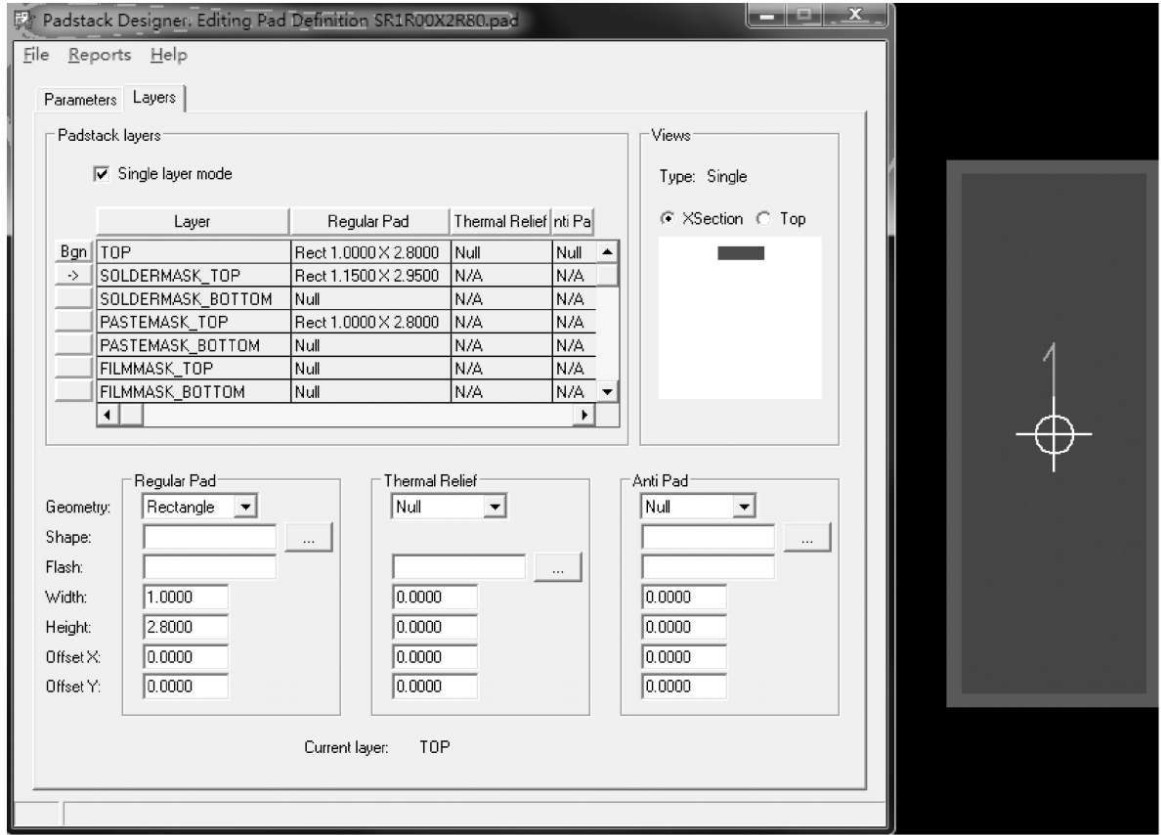

4.6 Cadence Allegro软件中焊盘的结构怎样?Cadence Allegro软件中怎么指定封装库路径?

笔者电子信息专业硕士毕业,获得过多次电子设计大赛、大学生智能车、数学建模国奖,现就职于南京某半导体芯片公司,从事硬件研发,电路设计研究。对于学电子的小伙伴,深知入门的不易,特开次博客交流分享经验,共同互勉!全套资料领取扫描文末二维码! 温馨提示:学而不思则罔,思而不学则殆。实践是检验真理的唯一标准! 目录 4.6 Cadence Allegro软件中焊盘的结构怎样? 4.7 Cade

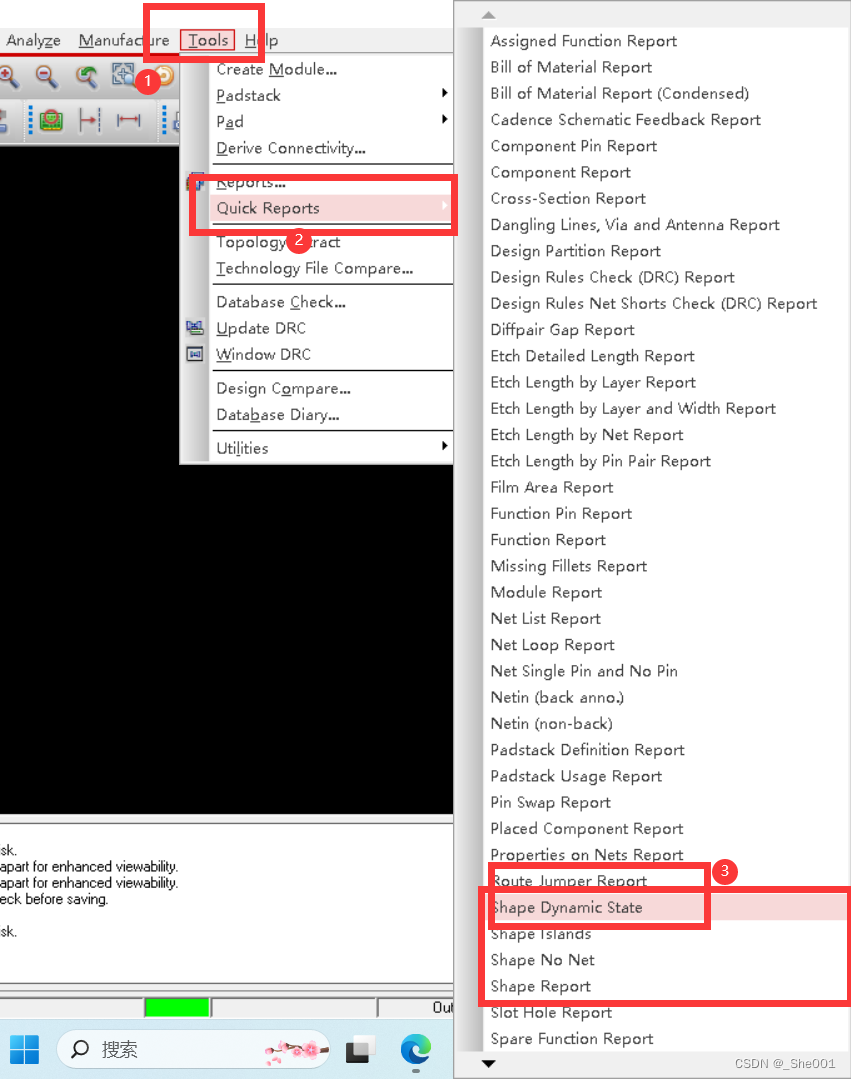

硬件学习件Cadence day15 allegro 查看state 后发现有网络未连接怎么办, shape 有问题怎么办,

1. 当我们查看 state 有问题怎么解决 1. 有问题的图片 2.解决办法: A.网络和节点有问题 如下图所示,点开下面这个窗口进行下面操作,能简单的网络未连接问题。 如下图所示,能进一步解决更难得网络节点未连接问题 如下图所示,能解决更更难得网络节点未连接问题 B. shape 问题 如下图所示解决 shape 问题 参考文章: Allegro使用技巧(3)---

cadence IUS (ncsim) code coverage 流程

1)irun 由irun产生coverage数据。 irun 加-coverage all(表示对所有类型的coverage都产生数据)和-covtest TB_NAME(指定将要产生的数据名称): irun -coverage all -covtest TB_CASE1 ... 跑完仿真,自动生成cov_work/scope/TB_CASE1 覆盖率数据。 2)imc

Cadence招聘IP研发工程师

1. Principal/Lead/Senior Physical Design Engineer Position Description: Focus on high speed digital DDR and HBM IP physical implementation Have good physical design experiences in the digital

Cadence招聘软件研发工程师

1.Lead Software Engineer/ Software Engineer II Position Description: The candidate will be a member of the Innovus placement team in Shanghai, to work on the development and maintenance of global

Cadence OrCAD 17.2 生成网络表出错ERROR (ORCAP-5004):Error initializing COM property pages 的解决办法

以管理员的身份运行C:\Windows\SysWOW64\cmd,依次运行如下两个指令,当然路径与自己装的Cadence17.2路径对应即可。 regsvr32 "C:\Cadence\Cadence\Cadence_SPB_17.2-2016\tools\bin\orTrueReuse64.ocx" regsvr32 "C:\Cadence\Cadence\Cadence_SPB_17.2-20

【原理图与PCB专题】使用Cadence如何在Layout时直接互换相同功能的PIN

在实际的项目中,比如有一些排阻、FPGA、ESD二极管引脚其实是可以互换的,但是如果没有使用PinGroup属性功能,对于大公司原理图设计与PCB Layout分开的情况,我们可能需要按以下步骤: 这个步骤中存在通知和等待过程,如果存在多次(如多个器件,或是修改后调整又觉得不合适)又反复修改,那沟通成本比较高。 为了解决这个问题,使用Cade

cadence视频/allegro视频-小哥Cadence Allegro完整2层板PCB视频

百度网盘下载链接:https://pan.baidu.com/s/1gg-eIuNm5mdelPqtle_fug 非常经典的一套cadence视频,讲解连贯,一气呵成,非常适合学习cadence allegro软件的工程师。 如果是初学pcb设计,建议多看几遍这一套pcb视频,非常的好哦!

小哥Cadence Allegro 132讲字幕版PCB设计视频教程-cadence视频-allegro视频-PCB视频

百度网盘免费下载完整版: 链接:https://pan.baidu.com/s/1uQbStXqzuxRAggny3iOwoA 提取码:t5fw

![Cadence高速板设计技巧(全志H3)[四]](https://i-blog.csdnimg.cn/direct/27edc442fdb84815bc44f79709e3fb86.png)