本文主要是介绍Cadence OrCAD使用小技巧,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

Cadence是公司名,Allegro(俗称阿狸狗)是该公司旗下的EDA工具品牌,OrCAD是该公司收购公司的EDA工具品牌。

OrCAD这个产品线是Cadence收购来的,Allegro才是嫡系。

注意:dsn不能放在中文路径下。

-

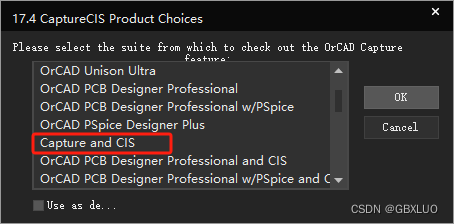

开机选capture and cis

CIS:Component Information System,元件信息系统,含有元件库管理之功能。

-

新建库:

选择菜单File—New—library,新建元件库

-

新建元件:

选中元件库文件(新建olb后缀文件),右键选择New Part新建元件。

-

查找相同的网络标号

选中网络所在的线段,然后鼠标右键,选中signals,左边会显示所有网络标号。

-

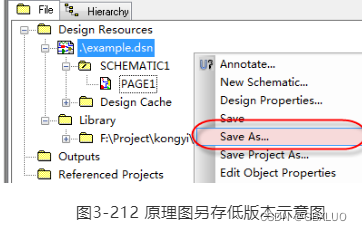

Orcad软件绘制的原理图存为低版本的方法

一种方法是:

第一步,需要选中降低原理图的根目录就是DSN文件,如图3-212所示,选中之后,点击鼠标右键,Save As,就可以存为低的版本:

第二步,在弹出的界面中,如图3-213所示,在保存类型那一栏可以选择低的版本,一般是存为16.2的版本,这样就存为了低的版本了;

第三步,这里可以看到有这样的一个情况,就是Orcad存为低的版本的时候,只能存为一个版本,那就是16.2的版本。其实在Orcad设计的时候,16.2之前的版本,机制都是通用的,都可以打开,16.2以后版本的机制是一样的,所以存为低版本的时候,是以16.2为分界点来处理就可以了。

另一种方法是:

1.将高版本文件输出为EDIF文件,配置自己命名。

2.打开低版本的orcad,导入EDIF文件,配置可自己命名。

Cadence设置单位:inch与mm

milimeter 英/ˈmɪlimiːtə(r)/ n.毫米

mil 英/mɪl/ n.密耳(千分之一英寸)

Cadence格点间距设置

Options》Preference》Grid Display:

左侧的Schematic Page Grid是原理图设计的格点,右侧Part and Symbol Grid是封装库设计的格点;

- Visible选项中,勾选Displayed是在设计时显示格点,不勾选则是不显示格点;

- Grid Style是格点显示的类型,Dots表示格点是点状的。Lines表示格点是线状的,点状简洁些;

- Grid Spacing表示的格点的间距,以Pin到Pin的间距来衡量,一般在设计原理图时选择1:1的关系。格点的间距设置成为1个Pin到Pin的间距。

-

原理图DRC检查

-

执行DRC检查:

选中dsn——在PCB选项下选择Design Rules Check,

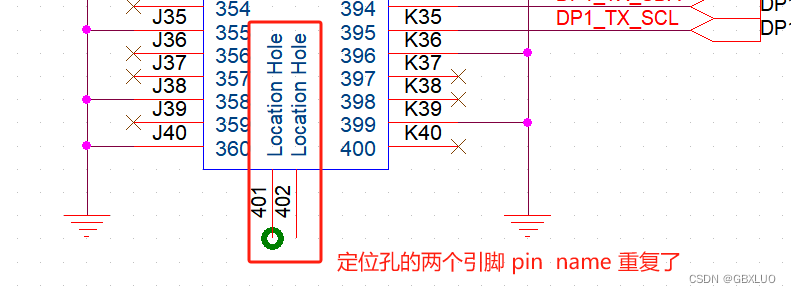

DRC报错pin脚同名

两种解决办法:要么修改pin name,要么给pin name修改类型为power。

举例如下:

DRC检查报错为:

ERROR(ORCAP-36041): Duplicate Pin Name "LOCATION HOLE" found on Package FPMC400_FPGA_0E , XS102E Pin Number 402: SCHEMATIC1, DP2_0_RX (670.56, 121.92). Please renumber one of these. /XS102E/401: SCHEMATIC1, DP2_0_RX (678.18, 233.68)

更改两个pin的type为power类型即可:

注意,DRC报错pin脚同名不影响正常导出给PADS Layout使用的网表文件。

也就是说如果在PADS中有该PCB封装,就能正常导入并layout。

DRC报错非法PCB封装字符

ERROR(ORCAP-2213): Checking Physical Rules

ERROR(ORCAP-36071): Illegal character "Dot(.)" found in "PCB Footprint" property for component instance N102: SCHEMATIC1, DP2_0_TX (190.50, 88.90) . /N102: SCHEMATIC1, DP2_0_TX (190.50, 88.90)

解决办法:

更改PCB Footprint的命名,将“.”更换为“_”或“-”。

但,DRC报错非法PCB封装字符不影响正常导出给PADS Layout使用的网表文件。

也就是说如果在PADS中有该PCB封装,就能正常导入并layout。

因为该非法PCB封装字符并不会影响导出网表给PADS Layout,因此在进行DRC检查时,如果已经基本上排除掉其他错误,可以选择不检查PCB封装属性,如下:

DRC报警:Check Power Ground Mismatch

INFO(ORCAP-2212): Check Power Ground Mismatch

QUESTION(ORCAP-1589): Net has two or more aliases - possible short? N202,GND

报错:2号GND引脚类型为Power,但是连接的网络名为AGND

不报错:2号GND引脚类型为Power,连接的网络名为GND

问题本质是原理图管脚型号的设定问题:

POWER的管脚名称同时为NET名称。

器件的电源引脚标号和电路中电源的网络标号不一样, 存在两个名称。

解决办法:

(1)只要将管脚名和网络名搞成一致就可以了。改其中一个就会引起其他问题,但是管脚名称可以相同,看起来整洁。

(2)把POWER属性改为passive。管脚名称不可以相同,可以从1开始排列,比如GND1,GND2...这是orcad软件设定问题,推荐这种解决方法。

(3)去掉Physical Rules检查。关掉后其他Physical问题同时被屏蔽。

总结:

引脚属性为Passive时,引脚名和网络名可以不相同,但是元器件的引脚名需要是唯一;

引脚属性为Power时,引脚名和网络名需要相同,元器件的引脚名可以相同;

DRC检查或输出网表时出现“Dupicate Pin Name”的错误

参考链接:

Orcad DRC 时出现“Duplicate Pin Name”的错误,怎么处理?_orcad电源pin自动连接到gnd-CSDN博客

GND网络,是电源网络,Orcad系统判定的依据就是除了电源管脚以外的管脚一律不准管脚名称一致,所以我们将这几个GND管脚的管脚属性改为电源属性即可,双击管脚,编辑属性,将Type改为Power,勾选上Pin Visible,将管脚名称显示。

针对于不是电源属性的,出现此类报错的,我们同样的编辑管脚属性,在每一个管脚名称加上1、2、3、4…,依次递增,来区分管脚名称,比如NC1、NC2、NC3等。

将管脚名称一致的都按上述方法修改完成以后,点击右键关闭封装编辑页面,在弹出的界面中选择Update All,这原理图中所有使用这个原理图封装的器件就都全部更新了,这个Duplicate Pin Name的问题也就解决了。

DRC检查报 Possibe pin type conflict,output connected to Power

是引脚类型连接错了,xs21的引脚类型选的output,接到了power类型电源上,因此报错。

绿色圆圈即为ERROR:

Reference is invaid for this part GLOBAL_RESET_N

Report for Invalid References:

[DRC0011] Reference is invalid for this part GLOBAL_RESET_N: SCHEMATIC1, 09_FPGA_DDR4_IF1 (157.48, 187.96)

元件的命令有错误;

可能是元件标示SW后面只能是数字,不能是字母。

把DRC对话框中report invalid packaging选项不勾选,再次执行一下DRC检验,应该没有问题。

-

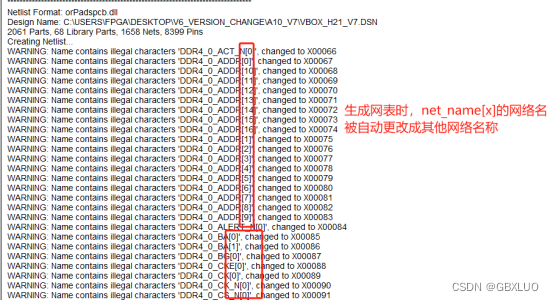

生成网表时网络名自动更改为其他网络名

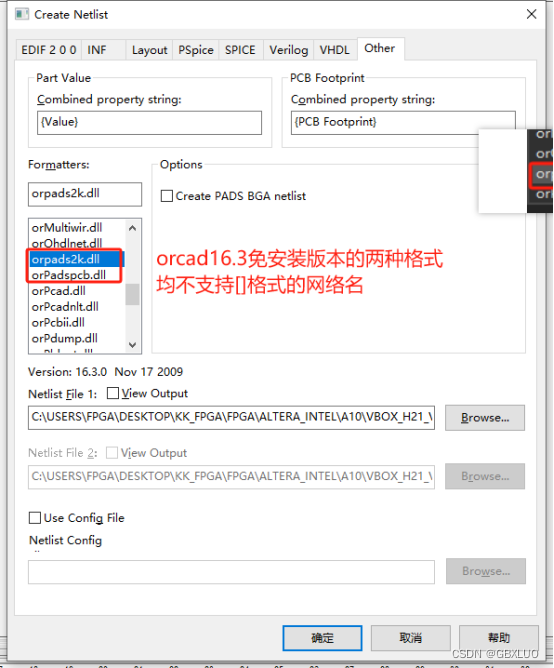

软件:orcad16.3绿色版

orPcadpcb.dll会自动修改网络名:

orcad16.3的两种网表格式不支持net_name[x]的命名形式,要用net_name_x或者net_name-x的形式。

软件:cadence17.4完全版本:

解决办法:orcad导出网表时选择orpads2k64.dll或者orPadspcb64.dll格式即可

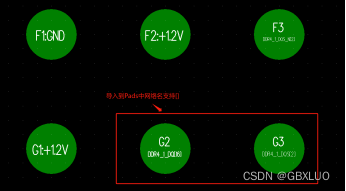

导出网表成功:

导入网表到pads vx2.7中成功支持带[]符号的网络名:

Orcad导出pdf文档:

File > Print,在弹出列表中设置:

1、按纸张大小放大/缩小:Scalet o paper size

2、垂直居中:Center Veritcally

3、设置:Setup

4、导出为WPS PDF文档

5、确定

6、Ok即可导出

Allergo的Orcad原理图软件导出FPGA引脚约束tcl脚本文件:

打开OrCAD Capture CIS,选择Tool 》 Export FPGA,在弹出的FPGA Export弹窗中进行如下设置:

- FPGA Fammily Vendor:有Xilinx与Altera可选

- FPGA Component:选择位号为N1的FPGA芯片

- 勾选Genearate Wrapper File

- 支持Verilog与VHDL

- File format中按需选择Net Name v/s Pin Number或者Pin-Name v/s Pin Number

- File Type中选择Generate TCL File,方便将产生的tcl文件copy到Quartus的prj_name.qsf文件中

产生如下Quatus支持的prj_name.tcl文件:

![]()

内容格式均为:

set_location_assignment PIN_A1 -to TEST_LED

注意:

1、在设置Quartus的顶层文件PORT时要与Net Name v/s Pin Number中的Net Name对应上;

2、导出的tcl文件会将dsn原理图中的网络名均统一成大写字母,也就是如果你的FPGA管脚网络名为小写,导出来的tcl文件网络名被改为大写字母。

这篇关于Cadence OrCAD使用小技巧的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!