本文主要是介绍Cadence 17.4 PCB操作记录,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

文章目录

- 画板子边框

- 设置路径

- 导入网表

- WARNING(SPMHNI-192).

- WARNING(SPMHNI-194)

- ERROR(SPMHNI-196)

- WARNING(SPMHNI-337)

- Fix/Unfix

- 设置元件高度

- 刷新焊盘

- 修改并更新封装

- 隐藏某一层

- 对齐元件

- 打过孔

- 铺铜连接方式

- PCB翻转

- 设置旋转快捷键

- 开窗

- allegro统一更改丝印字体大小

- 走线部分删除

- 蓝色三角形错误

- 负片层网络分割

- 查看布线或者DRC状态

- 导出Gerber

- 导出坐标文件

- PCB生成封装库

- 微信公众号

画板子边框

Board Geometry / Design_Outline, 添加矩形, 右边Options->Corners->选择圆角Round, 倒角3mm, 然后输入左下角坐标(x -45 -20.9)和右上角坐标(x 45 20.9), 这样, 板子边框就生成了.

接着画出Route Keepin(铺铜/负片之类的必须有, 比Outline内缩10mil以上) 和 Package Keepin, 当然也可以用Z-Copy命令.

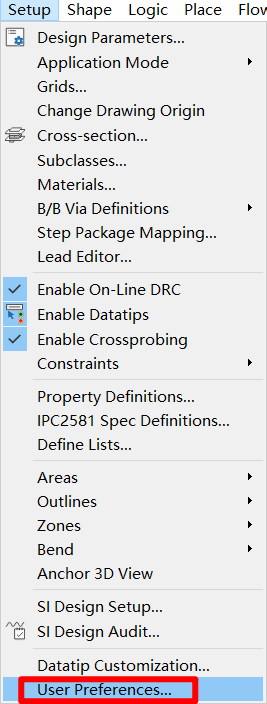

设置路径

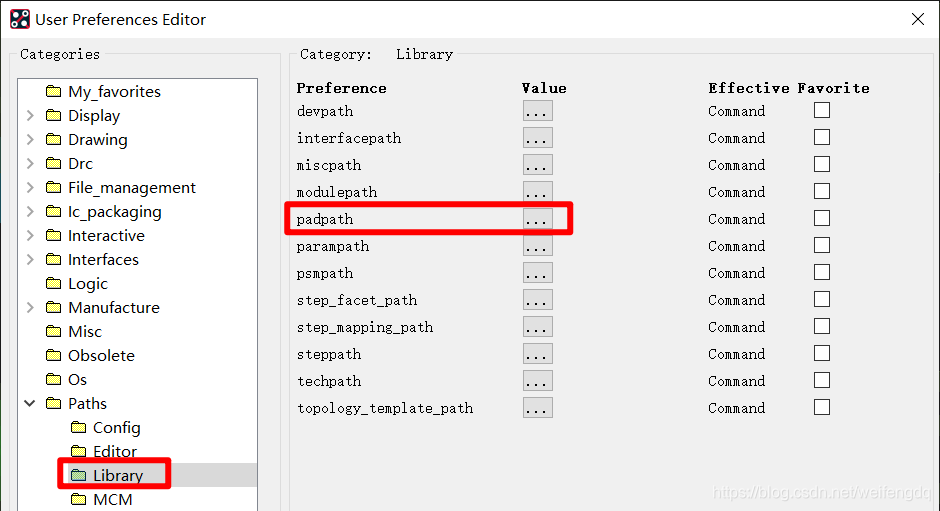

主要是焊盘(pad)和Symbol(psm)的路径.

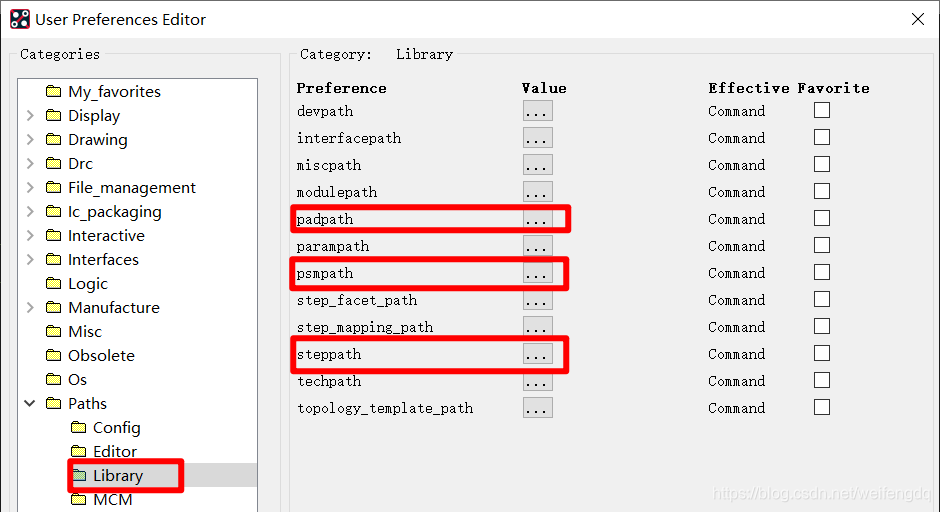

导入网表

导入网表后, netrev.lst文件列出了错误和警告.

WARNING(SPMHNI-192).

WARNING(SPMHNI-192): Device/Symbol check warning detected.

下面一般会给出解释, 继续往下看.

WARNING(SPMHNI-194)

WARNING(SPMHNI-194): Symbol 'DO-214AC' used by RefDes D1 for device 'DIODE_ZENER_DO-214AC_SS54' not found.

The symbol either does not exist in the library path (PSMPATH) or is an old symbol from a previous release.

Set the correct library path if not set or use dbdoctor to migrate old symbols.

到psmpath文件夹下去查看, 发现只有DO-214AC.dra文件, 没有.psm文件, 这个好办, 打开.dra文件, File->Creat Symbol…, 创建同名的.psm文件即可.

一般来讲, 编辑.dra后保存会自动生成.psm文件, 但难免出现些上面的意外吧…

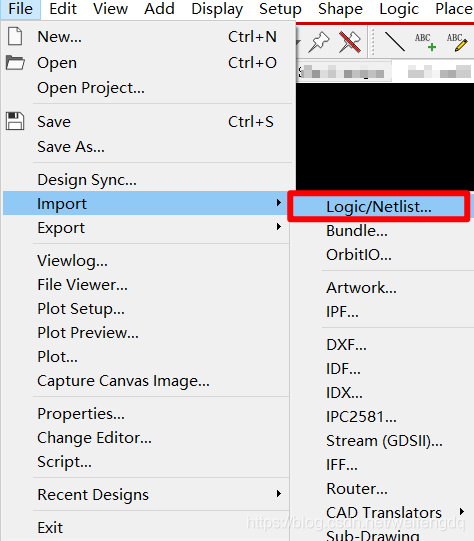

ERROR(SPMHNI-196)

ERROR(SPMHNI-196): Symbol '2-406549-1' for device '2-406549-1_2-406549-1_2-406549-1' has extra pin '0'.

这个是因为封装中多了一个引脚0(用作固定孔, 原理图文件没有对应引脚), 参考这一篇文章:

ERROR(SPMHNI-196)

When netlisting between Capture and PCB editor the total pin count has to match. If the package symbol (footprint) has 39 connect pins, the Capture part has to have 39 pins. Mechanical pins in the package symbol do not count. When you add pins in the package symbol you can choose to add then as connect or mechanical in the Options Tab. You can convert a connect pin to a mechanical by deleting the pin number. The pin number is text so Edit>Delete set the find filter to text and select the text to delete, select another pin or Right Mouse Done.

删除引脚号, 把引脚改成机械孔即可:

然后File->Creat Symbol.

WARNING(SPMHNI-337)

WARNING(SPMHNI-337): Unable to load symbol 'SOT-23-3' used by RefDes Q1 for device 'NPN_SOT-23-3_MJD44H11T4G': WARNING(SPMHUT-127): Could not find padstack R110_60. [help]

这个是少了焊盘, 把焊盘复制到padpath路径下即可.

Fix/Unfix

固定接口,Shape或者关键芯片, 发现删除移动不了需要先Unfix, 再操作

设置元件高度

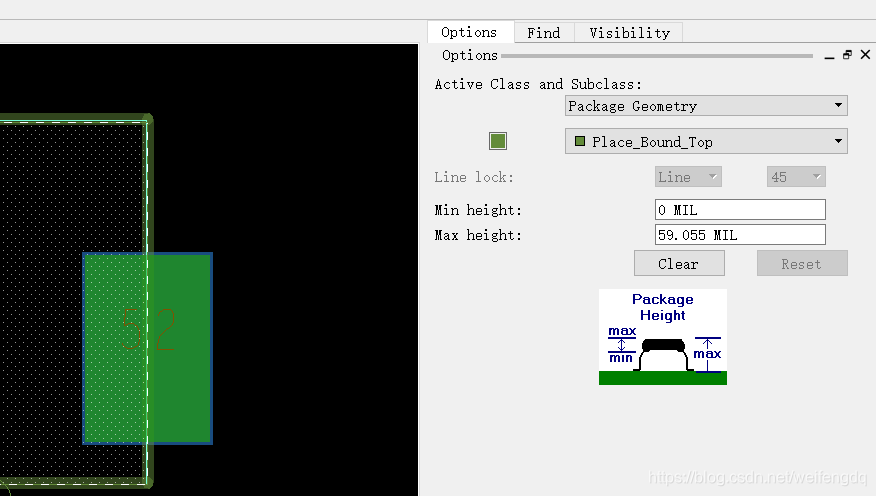

画完Package_Geometry -> Place_Bound_Top后, 可以设置下元件高度: Setup -> Areas -> Package Height, 点选 Package_Geometry -> Place_Bound_Top 的Shape, 可以在Options中修改:

刷新焊盘

直接用:

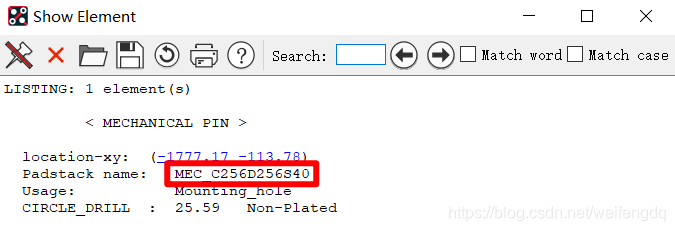

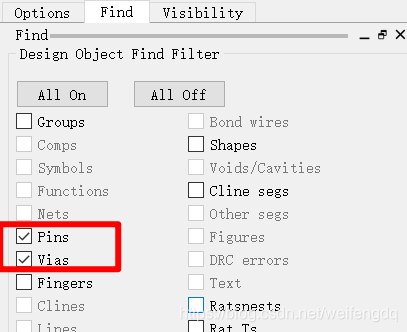

配合Find -> Pins查看引脚焊盘名称, 复制这个名称:

使用everything之类的搜索这个焊盘, 修改保存, Tools -> PadStack -> Refresh:

修改并更新封装

某个接插件的焊盘有些问题, 修改了封装, 如何更新到PCB呢?

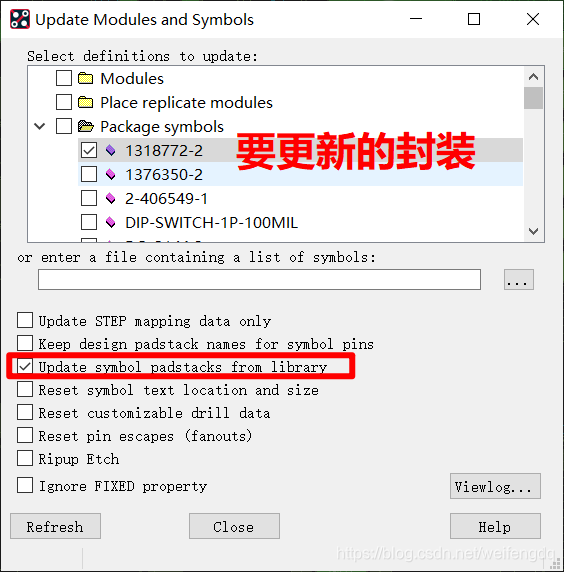

Place -> Update Symbols...:

点击Refresh, 弹出log提示:

------ Symbol Refresh Messages ------

‘1318772-2’ symbol starting to refresh:

ERROR(SPMHDB-243): Cannot modify element; the object or a parent has the FIXED property. [help]

ERROR(SPMHNI-254): Unable to load symbol, ‘1318772-2’: ‘Cannot modify element; the object or a parent has the FIXED property.~

[help]’.

引脚被我固定了, 点击Unfix重新解固定:

然后重新操作刷新即可.

隐藏某一层

比如我想把恶心的Assembly_Top和Assembly_Bottom隐藏:

对齐元件

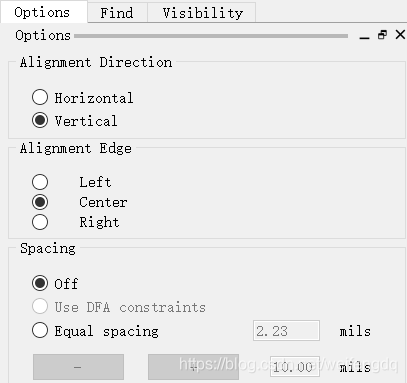

切换到Placement edit模式, 按住Ctrl连续选中元件, 右键Align components:

然后可以在Options中选择水平/竖直, 中心/座/右对齐, 还有间距等.

打过孔

只打过孔不走线, 还是点击Add Connect图标:

然后双击, 右键Done即可.

批量放置过孔可以用 Place -> Via Array.

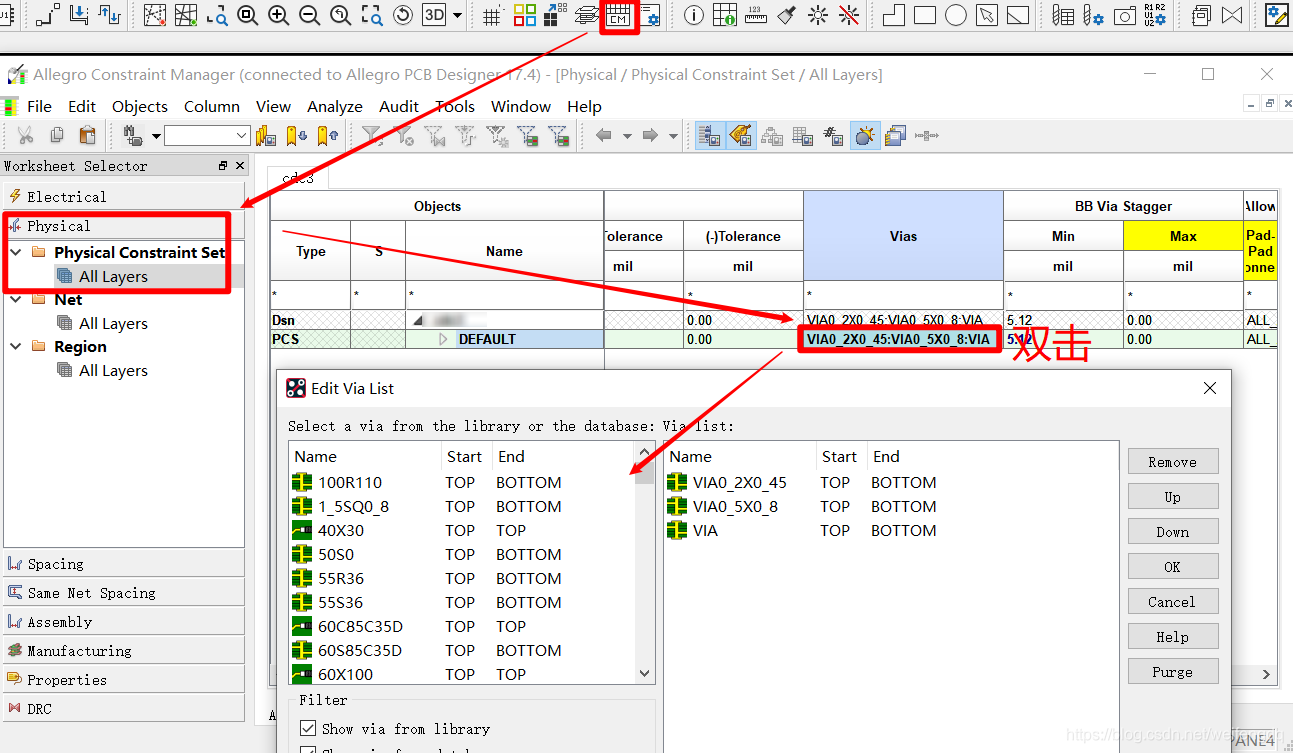

自定义过孔后, 在Setup->User Preferences -> Paths -> Library中设置好过孔的路径, 这里我把自定义的过孔放到了padpath中:

然后在Cmgr中添加自定义过孔:

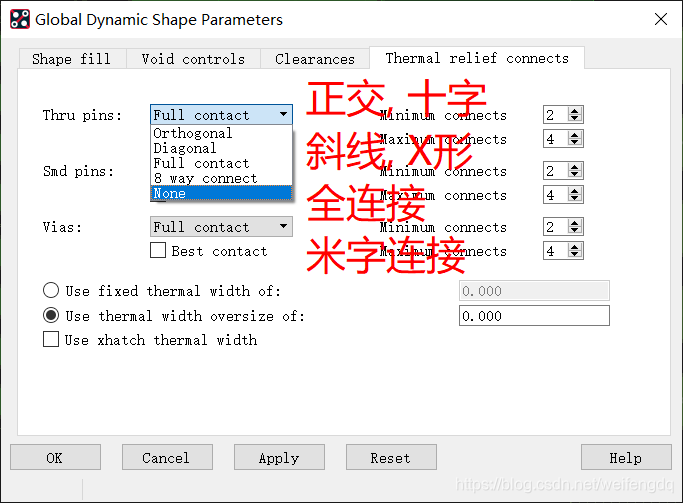

铺铜连接方式

Shape -> Global Dynimic Shape Paramerters

PCB翻转

元件右键Mirror, 可以把元器件放到底层, 然后进行底层布线, 一般会把PCB翻转到背面布局和布线, 这时需要 View -> Flip Design .

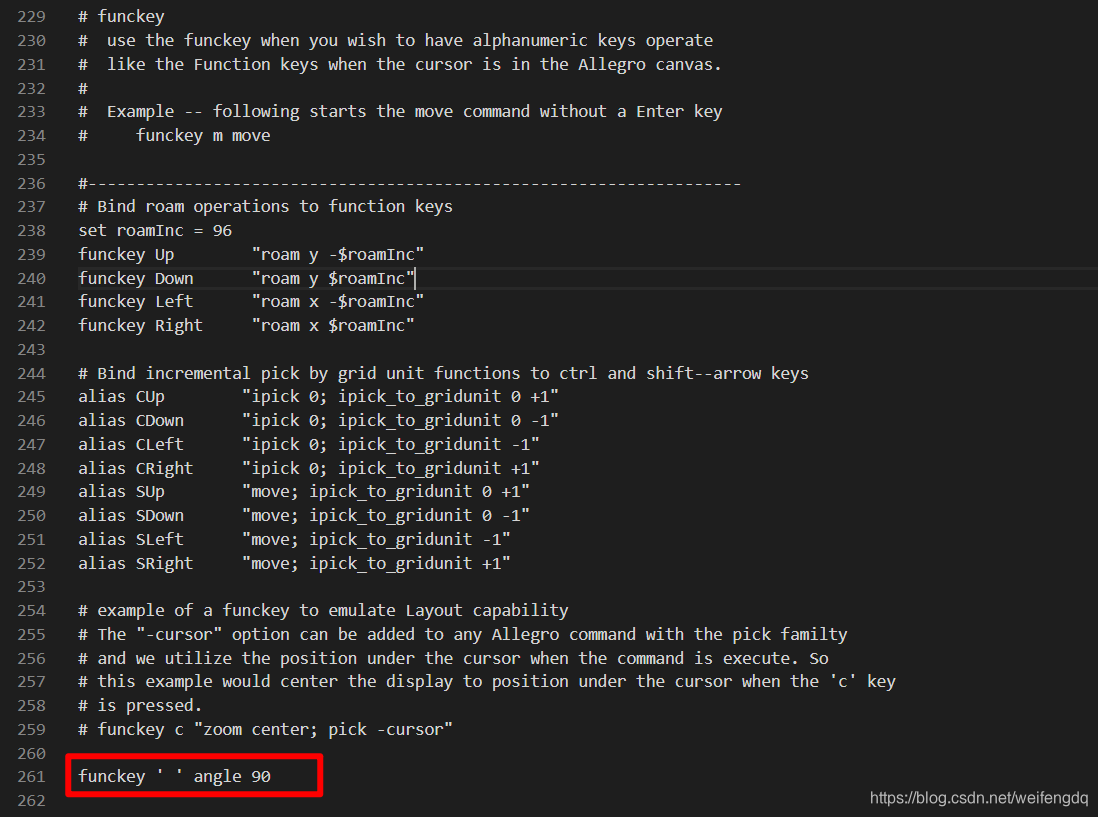

设置旋转快捷键

右键spin, rotate…被折磨的痛不欲生, 其实是可以设置旋转快捷键的, 如直接在Command里面输入:

funckey ' ' iangle 90 #按空格以90度旋转选中的物体, 但单引号里面是空格

funckey ~R iangle 45 #按ctrl+R以45度旋转选中的物体

当然, 这种方法下次打开就没了, 得重新输入. 如果想一劳永逸, 更改安装目录 Cadence_SPB_17.4-2019\share\pcb\text下的env文件, 加上 funckey ' ' angle 90 这一句:

这样, 就可以在移动的时候按空格旋转了.

开窗

Board Geometry 下 Soldermask_Top 或者 Sodermask_Bottom 画 Line 或者 Shape, 就可以让铜皮裸露.

参考 Allegro中设置开窗的方法

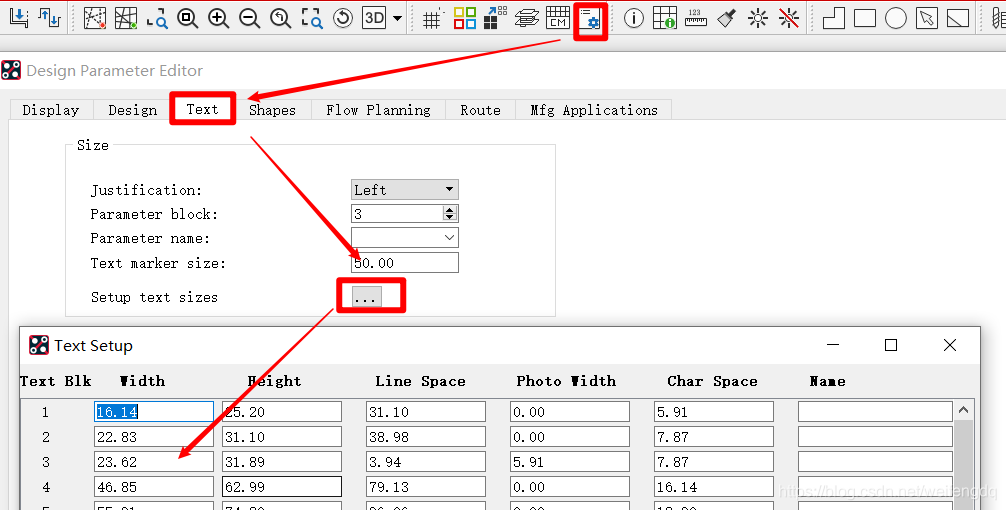

allegro统一更改丝印字体大小

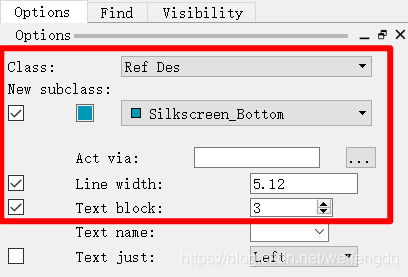

Edit -> Change, 然后在Options选项卡中, Silkscreen_Bottom是底层丝印, Silkscreen-Top是顶层丝印:

之后那鼠标框选整个PCB, 就可以把丝印统一更改成想要的Text block的大小(默认的Text block的3号字体还可以, 与嘉立创的32mil高/6mil线宽相去不远).

走线部分删除

这个需要用到Cut, 直接看图:

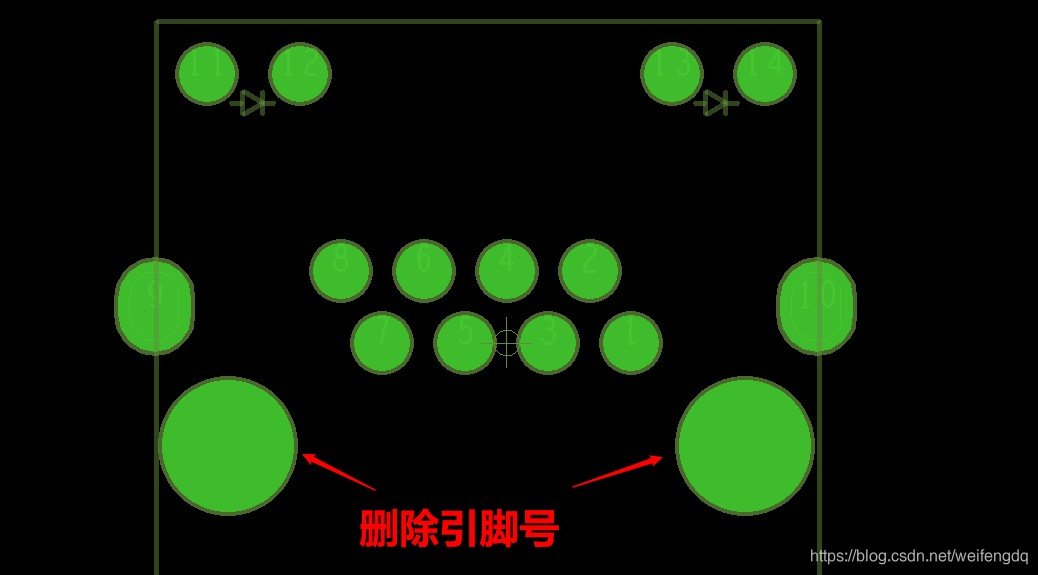

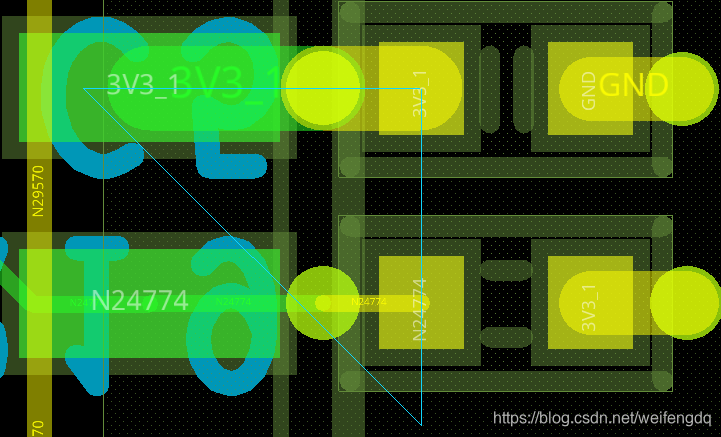

蓝色三角形错误

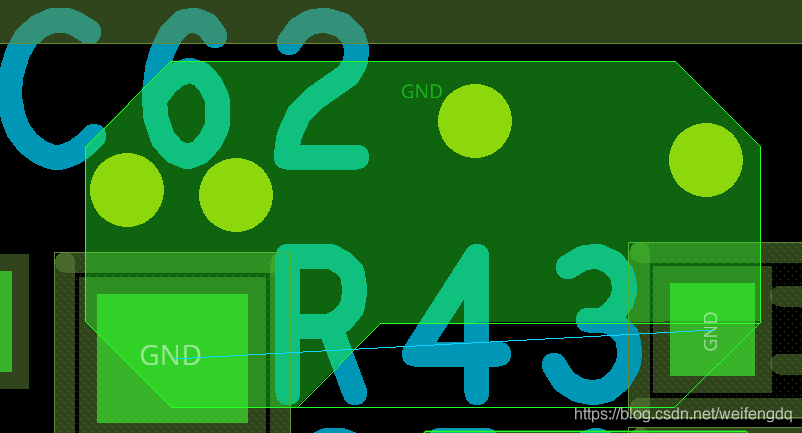

如下图中的直角三角形顶点 3V3_1:

乍一看不知所措, , 走线的时候要把Options面板中的PIN/Vias勾上,这样才会自动捕抓PIN/Vias的中心连接,不然即使线走到焊盘上了也是没连接上, 所以删除原有线, 重新连线, 要勾选Pins和Vias:

下面这个Shape显示未连接也是类似:

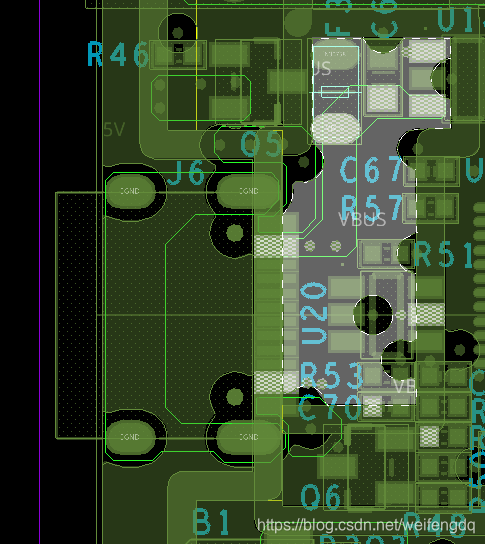

负片层网络分割

Add Line, 在Anti Etch画线分割:

可以Find中只勾选Nets选中某一电源网络高亮作为分割参考:

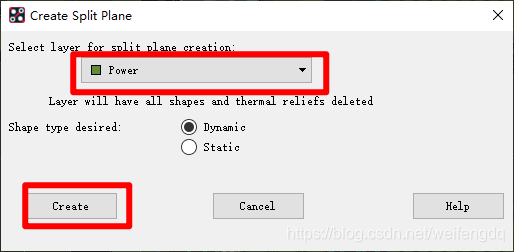

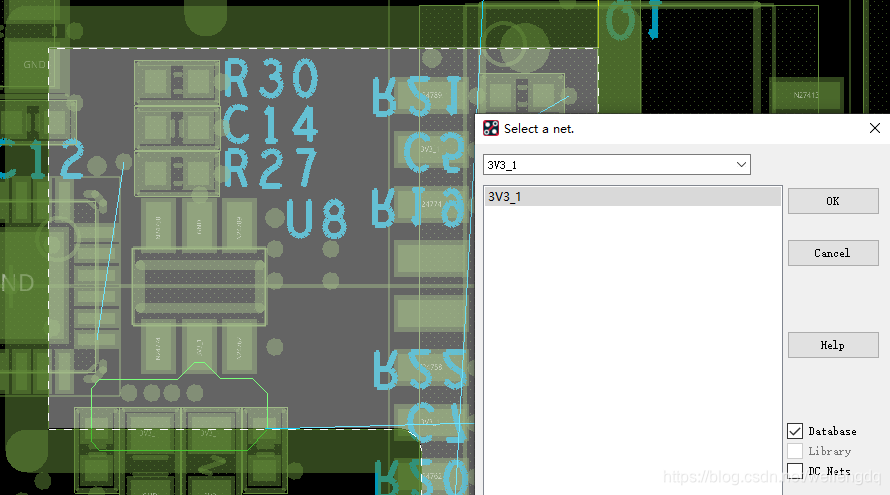

分割完后, Edit -> Split Plane -> Creat, 选中Power层, Creat开始给分割出的负片绑定网络:

依次绑定分割负片的网络:

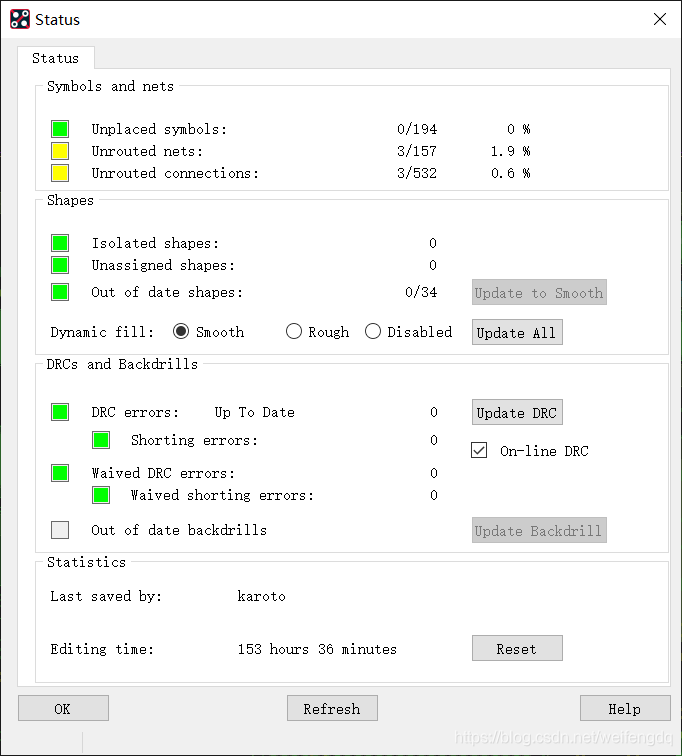

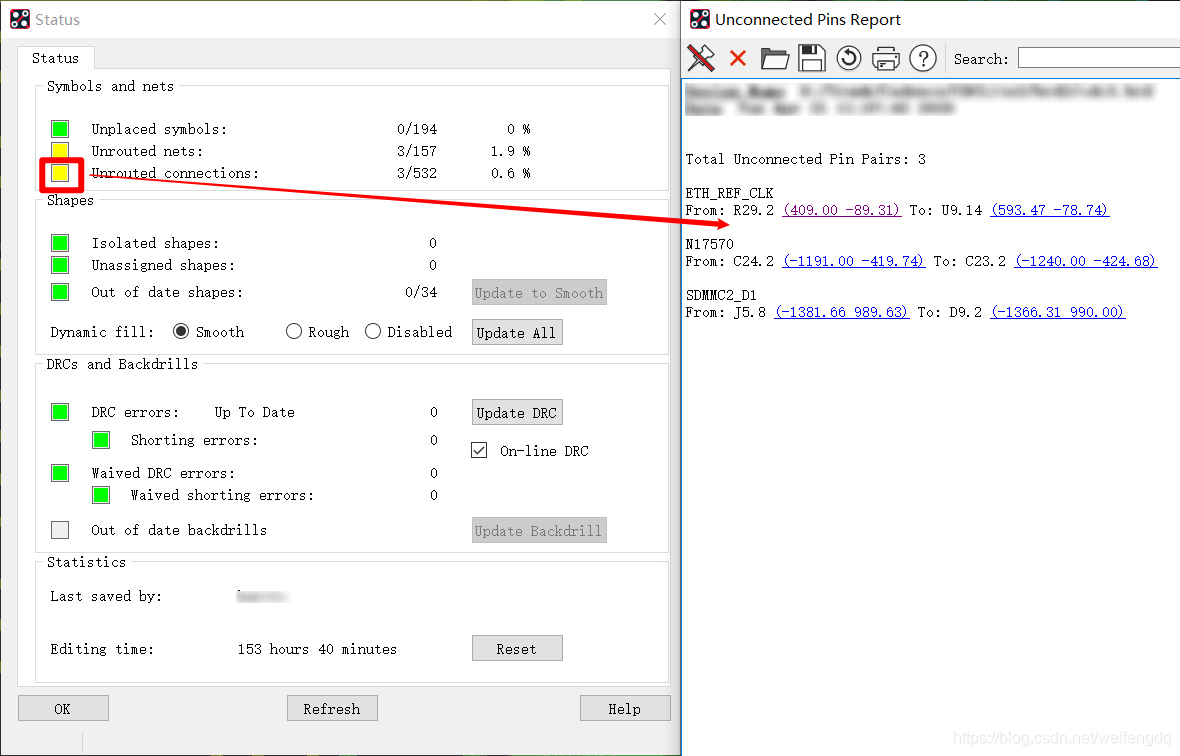

查看布线或者DRC状态

Display -> Status:

都搞到0才好. 点击左侧颜色小格子(有的可以点有的不能点)弹出未布线引脚, 点击蓝色坐标直接跳转到位置:

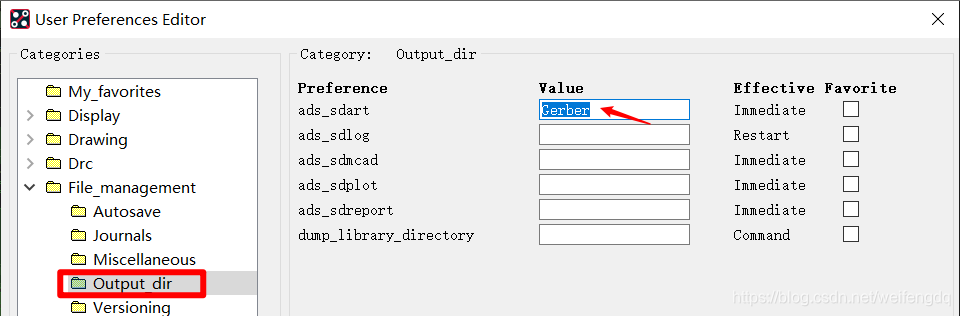

导出Gerber

设置Gerber导出路径: Setup -> User Preference…:

这样Gerber文件会导出到当前PCB所在目录下的Gerber文件夹.

先确保 Display->Status没有错误, 然后Manufacture->Artwork…:

默认的4层板有TOP/GND/POWER/BOTTOM, 右键Add手动添加(此处如有错误, 烦请指正):

| Film Name | Subclasses |

|---|---|

| TOP | BOARD GEOMETRY/DESIGN_OUTLINE ETCH/TOP PIN/TOP VIA CLASS/TOP |

| GND(用的正片) | BOARD GEOMETRY/DESIGN_OUTLINE ETCH/GND |

| POWER(用的正片) | BOARD GEOMETRY/DESIGN_OUTLINE ETCH/POWER |

| BOTTOM | BOARD GEOMETRY/DESIGN_OUTLINE ETCH/BOTTOM PIN/BOTTOM VIA CLASS/BOTTOM |

| TOPPASTE | BOARD GEOMETRY/DESIGN_OUTLINE PIN/PASTEMASK_TOP |

| TOPSOLDER | BOARD GEOMETRY/DESIGN_OUTLINE BOARD GEOMETRY/SOLDERMASK_TOP PACKAGE GEOMETRY/SOLDERMASK_TOP PIN/SOLDERMASK_TOP VIA CLASS/SOLDERMASK_TOP |

| TOPSILK | BOARD GEOMETRY/DESIGN_OUTLINE BOARD GEOMETRY/SILKSCREEN_TOP PACKAGE GEOMETRY/SILKSCREEN_TOP REF DES/SILKSCREEN_TOP |

| BOTTOMPASTE | BOARD GEOMETRY/DESIGN_OUTLINE PIN/PASTEMASK_BOTTOM |

| BOTTOMSOLDER | BOARD GEOMETRY/DESIGN_OUTLINE BOARD GEOMETRY/SOLDERMASK_BOTTOM PACKAGE GEOMETRY/SOLDERMASK_BOTTOM PIN/SOLDERMASK_BOTTOM VIA CLASS/SOLDERMASK_BOTTOM |

| BOTTOMSILK | BOARD GEOMETRY/DESIGN_OUTLINE BOARD GEOMETRY/SILKSCREEN_BOTTOM PACKAGE GEOMETRY/SILKSCREEN_BOTTOM REF DES/SILKSCREEN_BOTTOM |

| DRILL | BOARD GEOMETRY/DESIGN_OUTLINE MANUFACTURING/NCDRILL_FIGURE MANUFACTURING/NCDRILL_LEGEND |

| OUTLINE | BOARD GEOMETRY/DESIGN_OUTLINE BOARD GEOMETRY/CUTOUT |

除了OUTLINE, 其他Film Name的BOARD GEOMETRY/DESIGN_OUTLINE可以不写, 注意下图中Undefined line width可以写个2, 以免板子外形生成不了(参考 关于板外框和Photoplot outline):

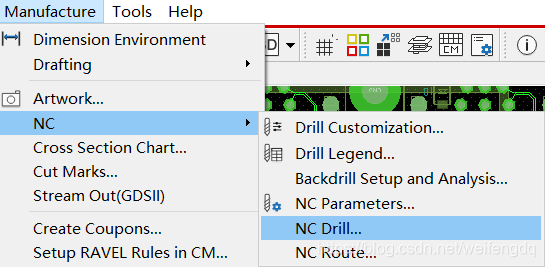

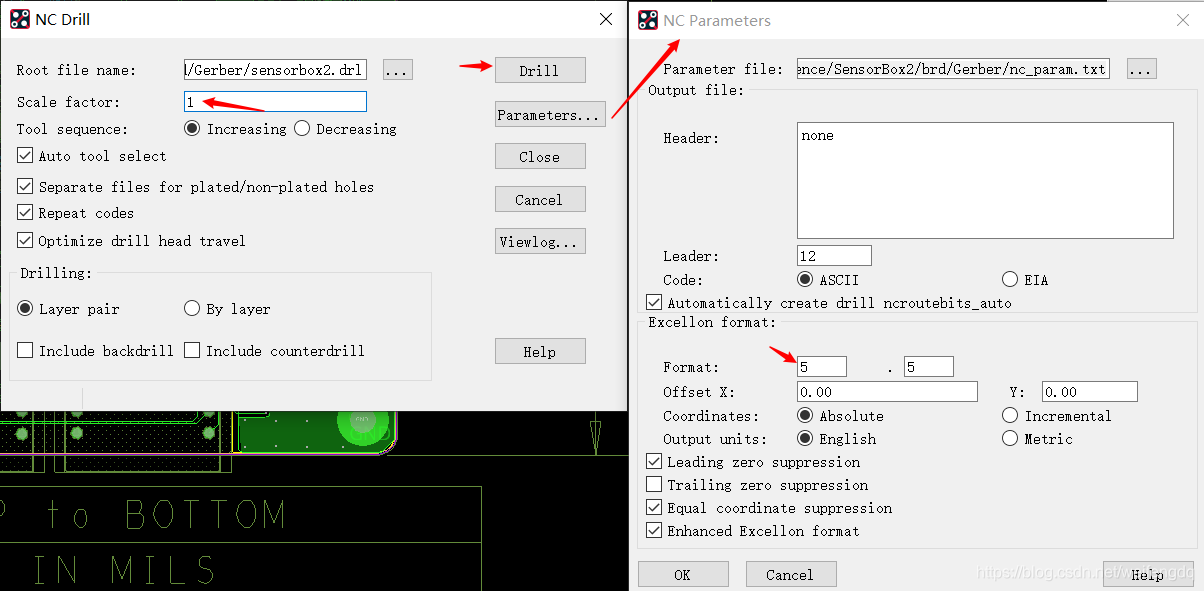

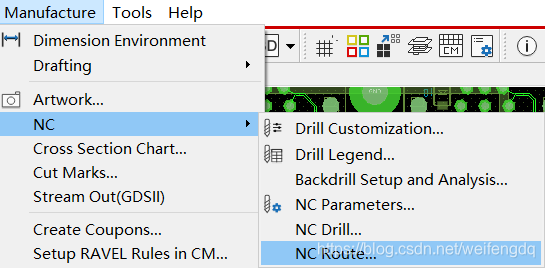

导出的是一堆.art文件, 接下来导出钻孔文件:

先点Parameters…, 设置后, 点Drill, 生成.drl文件:

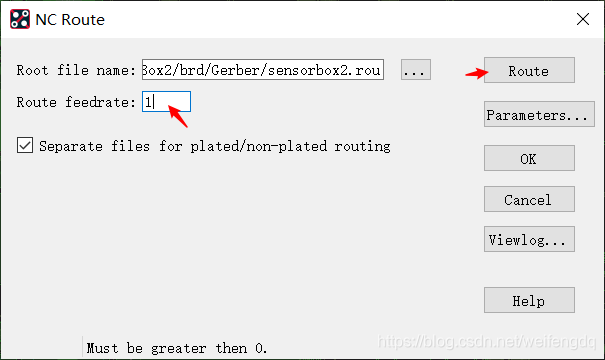

NC Route也导一下, 有时候是没有的:

把整个Gerber文件夹压缩一下.

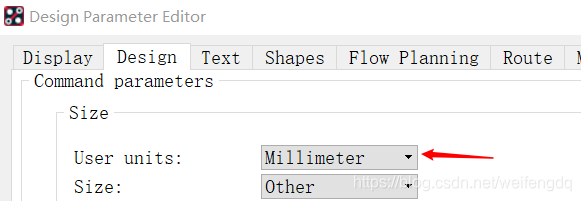

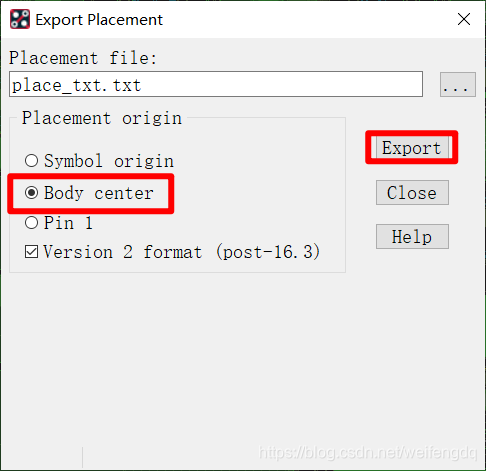

导出坐标文件

Setup -> Design Parameters, 设置单位为mm:

File -> Export -> Placement:

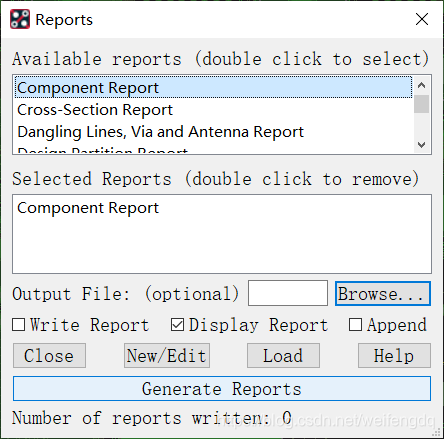

还有一种方法, 也参考自 Allegro 中导出坐标文件的方法

Tools -> Reports:

弹出页面, 自己点击保存命名为.xls文件即可

PCB生成封装库

.brd 是PCB文件, 可以导出焊盘封装等文件, File -> Export -> Libraries…

然后就生成了一大堆文件:

.dra文件是上图中的Device files, 可以由这个生成.psm文件.pad文件是上图中的Padstacks, 焊盘.psm文件是上图中的Package symbols.txt文件.ssm文件是上图中的Shape symbols, 焊盘覆铜层, 用于不规则焊盘.fsm文件是上图中的flash symbols, 热风焊盘, 负片层中会用到.map.log- …

微信公众号

欢迎扫描关注我的微信公众号, 及时获取最新文章:

这篇关于Cadence 17.4 PCB操作记录的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!