pcb专题

Allegro PCB--报错

1。 走线上打孔 问题:在走线上打的Via,我通过"Assign net to Via", 给与网络。成功后。 跑Tools\Database check\ Update all DRC(including batch), Via 网络又没有了 原因& 解决方法: VIA没有和走线完全重合 换个方法: 直接在线上打孔 或者走线change成shape, 或者用细导线把孔连到线路上。

PCB过孔规则排列,还是随机?

在现代电子设备设计中,印刷电路板(PCB)的复杂性不断增加,尤其是在高密度集成电路和多层PCB中,过孔(Via)起到了至关重要的作用。过孔通过将PCB的不同层相互连接,使得电路板不再局限于平面的布线,而是实现了立体化的电气连接结构,从而提升了设计的灵活性和电气性能。 1. 过孔的定义与作用 过孔,顾名思义,是PCB板上的一种孔,用于连接PCB不同层之间的导电路径。由于单层PCB的布线空间有限

猎板pcb研发工程师对HDI板的了解

作为一名电子研发工程师,在猎板PCB公司工作,我对HDI板(High Density Interconnector)的质量等级有着深入的了解。HDI板以其高密度互连的特性,在电子行业中扮演着至关重要的角色。我们通常根据HDI板的制造工艺复杂程度,也就是所谓的“阶数”,来区分其质量等级。 一阶HDI板是最基础的类型,它在标准多层板的基础上增加了一层微盲孔。这种设计相对简单,成本较低,适合大多数常规

Marin说PCB之闲谈设计经验之沟通

今天这期小编我不讲解技术,主要是分享一些个人的工作中的一些经验吧,首先给诸位分享的就是小编我的学的降龙十八掌第一式:沟通,为啥要说沟通是第一个我要说的话题呢,这个说来话长了,小编我就长话短说了。 因为对于一个刚刚接触到PCB行业的小白来说吧,你的画图技术能力是一方面,沟通的能力也是很重要的了,我在之前的国外的那家公司的上班的时候,经常听我们主管说的一局话就是学会有效沟通,这样你做事情就会

【Altium Designer脚本开发】——PCB平面绕组线圈 V1.4

PCB平面绕组线圈工具用于生成平面电机线圈,应用场景可参考平面电机的书籍、CNKI论文或平面电机的视频。此工具运行环境在Altium Designer中,可用于Altium Designer全系列的版本中。 以下工具可以定制和试用 原理图文档处理工具 ➡️物料编码自动查找工具 ➡️元器件参数集操作工具

硬件设计:查找原理图符号、PCB封装

PCB原理图符号和PCB封装 1.国外网站 PCB封装下载网站1:https://www.ultralibrarian.com PCB封装下载网站2:https://www.snapeda.com/home PCB封装下载网站3:https://componentsearchengine.com 原帖子:https://blog.csdn.net/tian362/article/detail

06:网表更新到PCB

1.先了解HDMI设计规范 有4对差分线,1对IIC串行总线信号从芯片---->防静电器件—>HDMI输出 发现错误,没有SDA网络,检查原理图 重新导网表 3.完成信号芯片—>防静电模块—>HDMI布局

电路笔记(PCB): 椭圆形板框绘制

使用 QCAD绘制并导出dxf文件 https://www.qcad.org/en/,QCAD 是一个免费的开源应用程序,用于二维 (2D) 计算机辅助绘图 (CAD)。 导入dxf文件

基于yolov10的PCB检测算法研究

内容:项目将YOLOV10创新后的PCB检测算法成功部署到GD32H757上,实现PCB缺陷的工业产线实时检测。 项目主要支持开源代码:HomiKetalys/gd32ai-modelzoo: Provide deployable deep learning models on gd32 (github.com) (想了解将AI模型部署到边缘MCU设备上,比如STM32/GD32,可以跟着这个

PCB设计中的3W原则、20H原则和五五原则

在现代电子设备中,印刷电路板PCB的设计对于设备的性能和可靠性起着至关重要的作用。随着电子设备向高速和高密度方向的发展,PCB设计中需要考虑的电磁兼容性EMC问题变得越来越复杂。为了减少电磁干扰(EMI)和串扰,工程师们常常遵循一些设计规则和原则,其中包括3W原则、20H原则和五五原则。这些原则能够有效地帮助设计师在PCB设计中优化信号完整性和电磁兼容性。 3W原则 什么是3W原则? 在

Marin说PCB之TP测试的Layout设计要求

提及到TP点这个器件想必诸位道友们肯定不会陌生吧,我们的单板在量产之前都是需要做很多测试的,一般在产品研发的A版本和B版本的时候都是需要在单板上加上这个器件的。小编我最近在做一个改板,项目组为了降本增效,把单板的尺寸缩小了很多,所以很多模块都需要压缩了,小编我在细化压缩一个MCU模块布局,做完了我邮件发给了英国伦敦的同事约翰,他看完飞书给我说了虽然现在的MCU模块的布局看上去是小了很多,到是你的T

嵌入式软件--PCB DAY 3

一、TypeC接口 1.介绍 TypeC接口也是USB接口的一种。 A口给电脑使用,B口给外设使用,诸如打印机。USB A口和B口最初由USB-IF在1996年引入。根据当时的USB协议,A口主要用于主设备(如电脑),而B口则用于从设备(如打印机和摄像头)。随着USB-C接口的日益普及,目前使用B口的设备已经不太常见。 2016年推出了Type C3.0,也就是我们现在普遍使用的接口。

AD原理图Update成PCB时提示Comparator Results的原因

在使用AD20把原理图转换成PCB时,AD提示 【原理图导入PCB时提示ECO的原因】 解释是: 原理图中存在元件未添加PCB封装。 验证 1、从右下角的panels打开messages 2、Validate PCB Project 3、warning中的确提示有元器件缺少封装 在更改添加了原理图中的元件封装后,重新进行PCB转换,ECO顺利通过,转换后的PC

电路笔记(PCB): KICAD 导入 JLC嘉立创项目

KICAD导入JLC嘉立创项目 标准版 对于标准版,得到一个zip文件 在kicad中选择导入即可 在导入标准版时没有正确加载原理图 专业版 安装JLC专业版 由于我的JLC标准版无法导出完整项目文件,需要安装专业版,激活软件在线申请下载即可 导出项目 对于专业版:文件-》另存为-》工程另存为(本地),会得到一个.erpo文件 导入到Kicad中 导入时直接选

电路笔记(PCB):JLC 创建新的原件符号和封装+应用展示

创建新的原件符号和封装 假设有一个特殊封装的电容,封装尺寸为5mm5mm,两个引脚为4mm1.5mm大小的长圆形顶层焊盘 ”文件-》“”新建“-》”符号“ 利用绘图工具绘制符号(别忘了放上引脚)并保存 放置到原理图后单击,选择“封装” 选择封装库 注:创建封装时,下边的焊盘编号别忘了改成2号,否则就成这样了: 使用效果

电路笔记(PCB):数字滤波电路的拉普拉斯变换与零极点分析

拉普拉斯变换基础 拉普拉斯变换 拉普拉斯变换是一种积分变换,用于将一个时间域的函数(通常是信号或系统的响应)转换为一个复频域的函数。这种变换可以简化许多微分方程和线性系统分析的过程。其定义为: L { f ( t ) } = F ( s ) = ∫ 0 ∞ f ( t ) e − s t d t \mathcal{L}\{f(t)\} = F(s) = \int_{0}^{\infty} f

一文带你画PCB板,有手就行

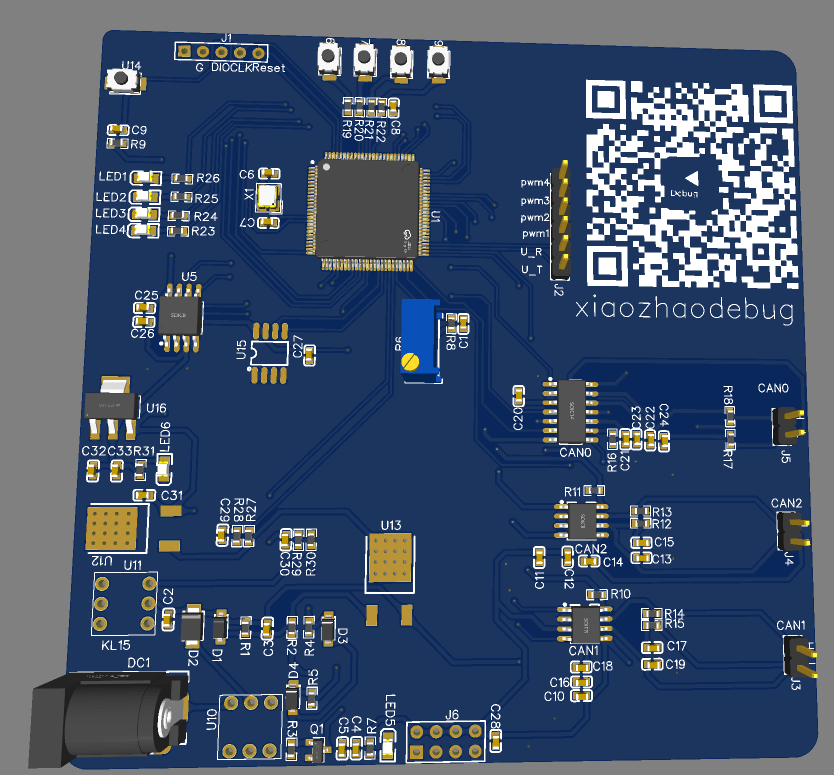

背景 最近写Autosar网络唤醒功能,想在实际硬件上验证,但是市面上没有找到板子验证,只能找人帮忙画PCB板。但是这里遇到比较大的问题,1、整个周期会比较长,板子不太可能一次就能完成,中间会出现修改的地方,反反复复折腾,很花时间。 2、一般找人设计硬件和画板,会比较贵。(身边会做硬件朋友太少了) 小昭在想,我作为软件工程师,我是不是也可以尝试做下,于是,在B站找到一个教程,用的EDA是嘉立创,

西安电子高速PCB学习(五)

感抗(Inductive Reactance)和容抗(Capacitive Reactance)是电感和电容在交流电路中对电流产生阻碍的特性。这两个概念源于交流电路中,电感和电容对交流电流的相应反应。 感抗(Inductive Reactance) 感抗是由电感(如电感线圈)在交流电路中引起的电抗。由于电感的存在,电流在通过电感器时会滞后于电压,从而表现出对交流电流的阻碍,阻碍滤波高频。 感

西安电子高速PCB学习(四)

注意了,信号发生器的不同通路不能并联使用,示波器的信号通路不能并联电源使用,不同信号发生器不能并联使用: 严禁多个电容共用过孔: 多个电容并联时,小容量的电容应更靠近芯片电源引脚,主要原因是为了优化电源去耦性能和滤波效果。具体原因如下: 高频特性更好:小容量电容(如0.1µF或0.01µF)的高频特性比大容量电容(如10µF或100µF)更好,具有较低的等效

西安电子高速PCB课件学习(一)

在放大器电路中,“自激”或“啸叫”通常指的是一种不希望发生的现象,即电路在没有输入信号的情况下,开始产生并放大自身的信号,这些信号会以高频或低频的振荡形式出现。以下是详细解释: ### 1. **自激振荡(Self-Oscillation)**: - **定义**: 自激振荡是指放大器由于反馈不当,产生不受控制的周期性振荡。这种振荡并非来自外部信号,而是由于电路本身的条件(如寄生电容、

以GD32F103C8T6为例的核心板原理图PCB绘制学习笔记简单总结

目录 GD32F103C8T6核心板 设计流程 基础知识 部分原理图解析 排针连接 (H1 - PZ254V-12-8P): 晶振 封装 基础知识 C0603封装 C0805 F1210封装 保险丝 L0603 贴片电感 LED-0603 R0603 HDR-TH_8P-P2.54-V-M-R2-C4-S2.54 排针 按键(SW-SMD-T6

Allegro画异形不规则PCB边框的方法

Allegro画异形不规则PCB边框的方法 前言一、Z-Copy简单介绍二、异形不规则边框的绘制步骤具体步骤 总结 前言 大多数PCB的边框是圆形或者方形的,但是也有一些特殊需求的PCB,会需要各种奇奇怪怪形状的边框,坐标方便定位还好做一点,涉及到圆形、半圆形的异形边框,只是手动去画出来,费时费力,还容易出错。这里我们介绍一种利用Z-Copy来绘制异形边框的方法。 一、