本文主要是介绍cadence SPB17.4 - allegro - DRC - Minimum Line to Shape Angle,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

前言

铺地铜之前, DRC是没问题的.

铺地铜之后, 出现 DRC错误 Minimum Line to Shape Angle

例子如下:

| Constraint Name | DRC Marker Location | Required Value | Actual Value | Constraint Source | Constraint Source Type | Element 1 | Element 2 |

|---|---|---|---|---|---|---|---|

| Minimum Line to Shape Angle | [(989.48 330.10)](xprobe:xy: 989.48 330.10 ) | 90.000000 degree | 78.309000 degree | MINIMUM_LINE_TO_SHAPE_ANGLE | DESIGN | Arc Segment “Gnd_Mcu Etch/Top” | Odd-angle Line Segment “Gnd_Mcu Etch/Top” |

| Minimum Line to Shape Angle | [(1368.36 41.00)](xprobe:xy: 1368.36 41.00 ) | 90.000000 degree | 66.969000 degree | MINIMUM_LINE_TO_SHAPE_ANGLE | DESIGN | Arc Segment “Gnd_Mcu Etch/Top” | Horizontal Line Segment “Gnd_Mcu Etch/Top” |

| Minimum Line to Shape Angle | [(975.34 315.96)](xprobe:xy: 975.34 315.96 ) | 90.000000 degree | 78.282000 degree | MINIMUM_LINE_TO_SHAPE_ANGLE | DESIGN | Arc Segment “Gnd_Mcu Etch/Top” | Odd-angle Line Segment “Gnd_Mcu Etch/Top” |

| Minimum Line to Shape Angle | [(1368.36 81.00)](xprobe:xy: 1368.36 81.00 ) | 90.000000 degree | 66.976000 degree | MINIMUM_LINE_TO_SHAPE_ANGLE | DESIGN | Arc Segment “Gnd_Mcu Etch/Top” | Horizontal Line Segment “Gnd_Mcu Etch/Top” |

这种DRC是说电气线和电气形状之间的角度超标了, 规则是90度, 实际角度小于90度.

只要不走特别大的锐角(e.g. 小于45度), 应该都不是啥大问题.

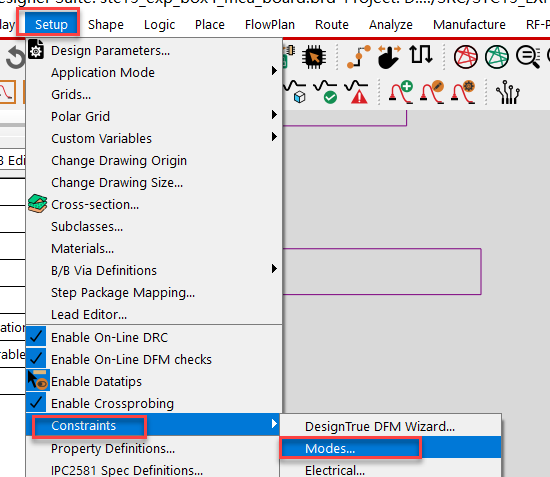

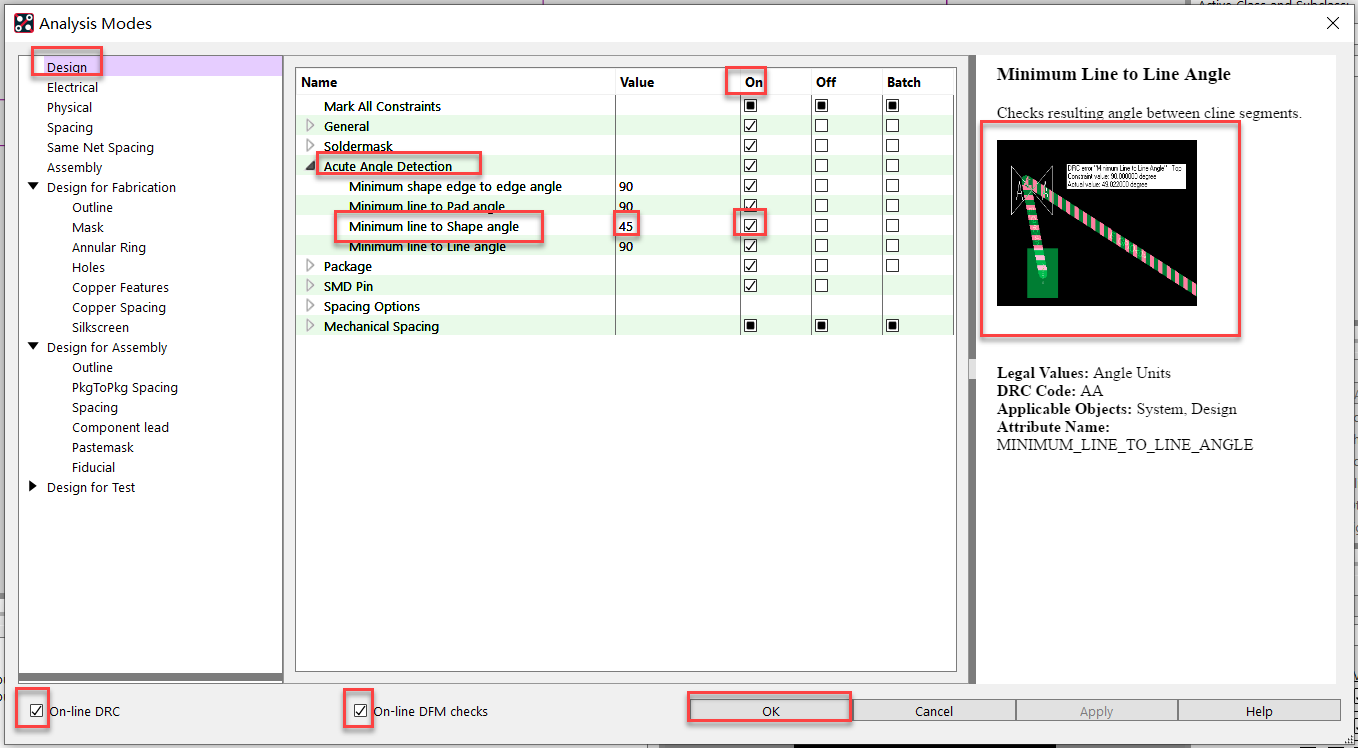

尝试解决

不能将这个DRC规则关了, 如果不是铺铜的电气线走出锐角, 还是要检查的.

尝试在规则中修改90度为45度

再次DRC, 没有这种DRC错误了.

END

mode框中的设置的作用:

- 选择打开/关闭哪些约束规则进行DRC. 这些规则的设置是在约束管理器中设置的. 在这里进行DRC使能.

- 还有一些没有在约束管理器中设置的全局规则, 在这里打开关闭. 可以设置一些全局的值.

铺铜时, 不能选择网格状动态铺铜, 只能选择动态铺铜(连在一起的铜皮). 否则网格状铜皮的线还是会触发很多这种角度DRC.

如果能指定某个网络不应用这种规则就好了.

这篇关于cadence SPB17.4 - allegro - DRC - Minimum Line to Shape Angle的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!