本文主要是介绍在vivado中GTP GTH GTZ使用GTGREFCLK时 Vivado_DRC: (REQP-52) 或Vivado_DRC: (REQP-49)错误解决办法,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

本文首发于hifpga.com

XILINX的手册上明确指出了可以用于测试目的使用GTGREFCLK(实际上量产中也有人这么用,通常是为了省差分晶振,或者是没有频率合适的差分晶振,这么用当然是有一些前提的否则量产翻车怪自己咯,FPGA就是这样,没有什么绝对可行或绝对不可行)。

可是当你真的使用的时候你就发现用常规编译是没法通过的。

首先在run implment 布局布线的时候就会出现Vivado_DRC: (REQP-49)错误

这个时候的解决办法就是在xdc中添加下面这一行,

set_property SEVERITY {Warning} [get_drc_checks {REQP-49}]; # DRC: using the GTGREFCLK port on a QPLL (GTP7)对于GTP和GTX\GTH报的错是不一样的,不同版本的vivado中这个错误号也会不一样,具体如下

# DRC: Change from ERROR to WARNING

#set_property SEVERITY {Warning} [get_drc_checks {REQP-44}]; # DRC: using the GTGREFCLK port on a MGT (GTH7)

#set_property SEVERITY {Warning} [get_drc_checks {REQP-46}]; # DRC: using the GTGREFCLK port on a QPLL (GTH7)

#set_property SEVERITY {Warning} [get_drc_checks {REQP-56}]; # DRC: using the GTGREFCLK port on a QPLL (GTX7)

set_property SEVERITY {Warning} [get_drc_checks {REQP-49}]; # DRC: using the GTGREFCLK port on a QPLL (GTP7)

#set_property SEVERITY {Warning} [get_drc_checks {REQP-1753}]; # DRC: using the GTGREFCLK port on CPLL (GTH7)

#set_property SEVERITY {Warning} [get_drc_checks {UCIO-1}]; # DRC: using the XADC's VP/VN ports接着在generate bitstream的时候又会报Vivado_DRC: (REQP-49)错误

'this connectivity has thelowest performance of the available clocking methods and can degradetransceiver performance'

这个时候仅在xdc加约束是不行的,必须针对generate bitstream这个阶段进行约束,具体操作如下:

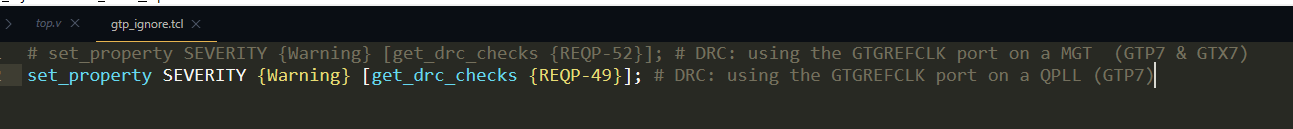

在ignore.tcl中添加如下内容

=======================补充============

在上面一步点OK确定tcl文件后,要先点apply再点OK,才会在当前工程生效,唉。。。。“做FPGA就是给厂家做测试”,这句话真一点没错!

=======================补充============

为避免添加ILA或者是添加时序约束后下面两句被自动清除掉,

set_property SEVERITY WARNING [get_drc_checks REQP-52]

set_property SEVERITY WARNING [get_drc_checks REQP-49]

因此全部改到tcl中,原谅我是个懒人,全部覆盖这个tcl。

这篇关于在vivado中GTP GTH GTZ使用GTGREFCLK时 Vivado_DRC: (REQP-52) 或Vivado_DRC: (REQP-49)错误解决办法的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!