coresight专题

地平线—征程2(Journey 2-J2)芯片详解(11)—CPU+CoreSight

写在前面 本系列文章主要讲解地平线征程2(Journey 2-J2)芯片的相关知识,希望能帮助更多的同学认识和了解征程2(Journey 2-J2)芯片。 若有相关问题,欢迎评论沟通,共同进步。(*^▽^*) 错过其他章节的同学可以电梯直达目录↓↓↓ 地平线—征程2(Journey 2-J2)芯片详解——目录-CSDN博客 4. CPU子系统 4.1 双核A53 CPU 4.

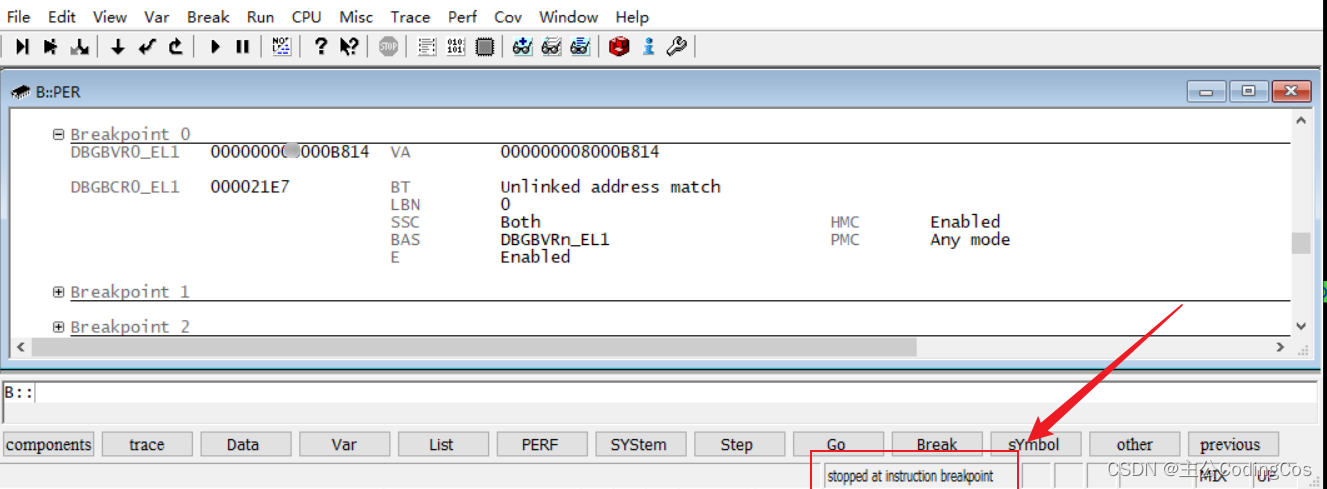

【ARM Coresight Debug 系列 -- ARMv8/v9 软件实现断点地址设置】

请阅读【嵌入式开发学习必备专栏 】 文章目录 ARMv8/v8 软件设置段带你断点地址软件配置流程代码实现 ARMv8/v8 软件设置段带你 在ARMv8/9架构中,可以通过寄存器 DBGBVR0_EL1 设置断点。这个寄存器是一系列调试断点值寄存器中的第一个DBGBVRn_EL1,其中n表示寄存器编号,对于ARMv8/9,通常可以有多个这样的寄存器,具体数量取决于实现

[ARM系列]coresight(一)

原文链接 目的:对复杂SOC实现debug和trace的架构 典型环境 包含:2个ARM core,一个DSP,众多coresight组件 coresight组件实现对core、DSP的debug和trace功能 环境中包含3个通路 trace通路:将core和DSP内部信息输出到外部debug通路:对core和DSP实现debugtrigger通路:用于core 和 core之间,c

【ARM Coresight 系列文章19.3 -- ARM DSU 120 Debug block】

请阅读【ARM Coresight SoC-400/SoC-600 专栏导读】 文章目录 ARM DSU-120 Debug BlockCluster debug components Cache DebugDSU-120 Cache Debug 特性应用场景 Terminology处理元素(PE)调试支持应用场景总结

【ARM Coresight SOC-600 -- ETF 介绍】

请阅读【ARM Coresight SoC-400/SoC-600 专栏导读】 文章目录 SOC ETFSOC ETF REGISTERScss600_tmc_etf RAM Read Data register(RRD)css600_tmc_etf RAM Read Pointer register(RRP)css600_tmc_etf RAM Write Pointer regis

ARM Coresight 系列文章 11.1 -- CoreSight Cortex-M33 CTI 详细介绍】

请阅读【ARM Coresight SoC-400/SoC-600 专栏导读】 文章目录 CTI 的工作原理CTI 主要特点CTI的使用场景 CTI 的工作原理 CTI 允许不同的调试和追踪组件之间基于特定事件进行交互。例如,当一个断点被命中时,CTI 可以用来触发内存的追踪捕捉或者外部仪器的行为,反之亦然。这种交互能够帮助更精确地分析和调试复杂的多核处理器系统。 C

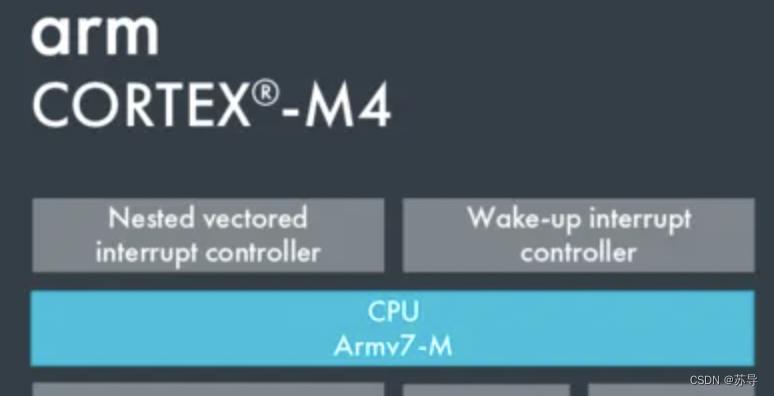

ARM Cortex-M CoreSight调试技术简单记录

简述 嵌入式系统开发中,调试与测试是非常重要的,ARM Cortex M也针对于不同场景和需求,提供了专门的调试技术,一般在ARM Cortex M架构的IC内都会集成CoreSight模块专用于调试。像ARM 7/9/11之类的是更早一类调试技术,ARM CortexA应该有更高速的调试技术了。这些都是和应用需求(速率、系统等)相关的。 CoreSight相关技术 列表如下: 名称详细

CoreSight学习笔记

文章目录 1 Components1.1 ROM Table 2 使用场景2.1 Debug Monitor中断2.1.1 参考资料 2.2 Programming the cross halt2.2.1 编程实现2.2.2 参考资料 2.3 CTI中断2.3.1 编程实现2.3.1.1 准备工作2.3.1.2 触发中断2.3.1.3 中断响应 2.3.2 参考资料 1 Com

【ARM Coresight OpenOCD 系列 3 -- OpenOCD 常用命令与扫描链scan_chain】

文章目录 1.1 TAP Declaration1.1.1 扫描链 1.2 Autoprobing1.3 DAP declaration (ARMv6-M, ARMv7 and ARMv8 targets) 1.1 TAP Declaration 测试访问端口(TAP)是JTAG的核心。TAP扮演许多角色,包括: 调试目标:CPU TAP可以用作GDB调试目标。闪存编程:有些

【ARM Coresight OpenOCD 系列 2 -- OpenOCD 脚本语法详细介绍】

请阅读【ARM Coresight SoC-400/SoC-600 专栏导读】 文章目录 1.1 swj-dp.tcl 介绍1.1.1 source [find target/swj-dp.tcl]1.1.2 swj-dp.tcl catch 命令介绍1.1.3 mem_helper.tcl 文件介绍1.1.4 变量名检查1.1.5 设置大小端模式1.1.6 设置 flash 烧录用到的 r

【ARM Coresight 系列文章 3.5 - ARM Coresight -- JTAG-DP(JTAG Debug Port) 详细介绍】

请阅读【ARM Coresight SoC-400/SoC-600 专栏导读】 文章目录 概述1.1 DP elements1.1.1 外部连接到 JTAG-DP上的信号1.1.2 Debug TAP 状态机 1.2 指令扫描链和指令1.3 DPv3 JTAG-DP 访问AP示意图 概述 本节内容主要介绍 JTAG Debug Port 、Debug Test Access P

【ARM Coresight 系列文章 3.5 - ARM Coresight -- JTAG-DP(JTAG Debug Port) 详细介绍】

请阅读【ARM Coresight SoC-400/SoC-600 专栏导读】 文章目录 概述1.1 DP elements1.1.1 外部连接到 JTAG-DP上的信号1.1.2 Debug TAP 状态机 1.2 指令扫描链和指令1.3 DPv3 JTAG-DP 访问AP示意图 概述 本节内容主要介绍 JTAG Debug Port 、Debug Test Access P

【ARM Coresight 系列文章 3.4 - ARM Coresight JTAG 详细介绍】

请阅读【ARM Coresight SoC-400/SoC-600 专栏导读】 文章目录 JTAG 背景介绍引脚输出配置 1. JTAG 简介1.1 Boundary-Scan 边界扫描1.2 TAP状态机的工作原理1.2.1 TAP 介绍1.2.2 TAP 状态机1.2.3 TAP 状态机 状态解析1.2.4 寄存器访问过程 1.3 JTAG 框架1.3.1 指令寄存器1.3.2 数据寄存

【ARM Coresight 系列文章 3.3 - ARM Coresight SWD 协议详细介绍】

文章目录 1.1 SWD 协议框图1.2 读/写时序及命令1.2.1 SWD 时序1.2.2 SWD 命令详情 1.3 芯片探测1.3.1 获取芯片 ID 1.4 读/写操作 1.1 SWD 协议框图 SWD协议可以配置SoC内部几乎所有的寄存器。时钟信号由SWCLK 管脚输入,数据信号从SWDIO管脚输入输出。首先 HOST 对SW-DP 进行操作,确定 AP 寄存器的参数

【ARM Coresight 系列文章19.2 -- Cortex-A720 AMU 详细介绍】

文章目录 1.1 PMU 与 AMU1.2 AMU 介绍1.2.1 AMU 编程模型1.2.2 AMU 的访问1.2.3 Activity monitors counters 1.1 PMU 与 AMU A-Prolifile 构架中的 Performance Monitoring Unit(PMU)和Activity Monitoring Unit(AMU)都具有性能计数器

【ARM Coresight 系列文章 15.2 – components power domain 详细介绍】

【ARM Coresight SoC-400/SoC-600 专栏导读】 文章目录 1.1. Coresight 电源域模型1.1.1 CDBGPWRUPREQ 和 CDBGPWRUPACK1.1.2 CSYSPWRUPREQ 和 CSYSPWRUPACK1.1.3 Power Domain ID In RomTable1.1.4 Power domain entries1.1.5 Alg

ARM CoreSight相关模块简介

最近在学习ARM CPU软硬件开发,对于CoreSight看到很多模块,简单总结了下。 1. DAP ARM DAP (Debug Access Port) 的主要作用是为调试工具提供直接访问 ARM 处理器和其它相关硬件的途径。DAP 是 ARM CoreSight 调试和追踪技术的一部分,它允许开发者进行实时调试和分析。 以下是 DAP 的具体功能和作用: 内存和寄存器访问: DAP

ARM CoreSight相关模块简介

最近在学习ARM CPU软硬件开发,对于CoreSight看到很多模块,简单总结了下。 1. DAP ARM DAP (Debug Access Port) 的主要作用是为调试工具提供直接访问 ARM 处理器和其它相关硬件的途径。DAP 是 ARM CoreSight 调试和追踪技术的一部分,它允许开发者进行实时调试和分析。 以下是 DAP 的具体功能和作用: 内存和寄存器访问: DAP

【ARM Coresight 系列文章19.1 -- Cortex-A720 PMU 详细介绍】

文章目录 概述Cortex-A720 PMU Features 1.1 PMU 使用介绍1.2 Performance monitors events1.3 Performance Monitors Extension registers1.3.1 Performance monitors program 1.4 Performance monitors interrupts1.5 Inte

【ARM Coresight Debug 系列 17 -- ARM Debug Vector Catch 详细介绍】

文章目录 1.1 Cortex-M Debug Mode1.1.1 停机模式1.1.2 调试监视器模式 1.2 Vector Catch(向量抓捕)1.2.1 AArch64 下的 Vector Catch1.2.2 Vector Catch 使能配置 1.1 Cortex-M Debug Mode 在 Cortex-M7 中的调试操作模式分为两种: 第一种称为“halt”

【ARM Coresight SoC-400/SoC-600 专栏导读】

文章目录 1. ARM Coresight SoC-400/SoC-600 专栏导读目录1.1 Coresight 专题1.1.1 Performance Profiling1.1.2 ARM Coresight DS-5 系列 1. ARM Coresight SoC-400/SoC-600 专栏导读目录 本专栏全面介绍 ARM Coresight 系统 及SoC-400

【ARM Coresight Debug 系列 17 -- ARM Debug Vector Catch 详细介绍】

文章目录 1.1 Cortex-M Debug Mode1.1.1 停机模式1.1.2 调试监视器模式 1.2 Vector Catch(向量抓捕)1.2.1 AArch64 下的 Vector Catch1.2.2 Vector Catch 使能配置 1.1 Cortex-M Debug Mode 在 Cortex-M7 中的调试操作模式分为两种: 第一种称为“halt”

【ARM Coresight Debug 系列 -- Linux 断点 BRK 中断使用详细介绍】

文章目录 1.1 ARM BRK 指令1.2 BRK 立即数宏定义介绍1.3 断点异常处理流程1.3.1 el1_sync_handler1.3.2 el1_dbg 跟踪 1.4 debug 异常处理函数注册1.4.1 brk 处理函数的注册 1.1 ARM BRK 指令 ARMv8 架构的 BRK 指令是用于生成一个软件断点的。当处理器执行到 BRK 指令时,会触发一个断点

【ARM Coresight 系列文章 4.1 - ARM Coresight AHB-AP 使用详细介绍】

文章目录 AHB-AP 介绍AHB-AP 的连接 AHB-AP 介绍 AHB-AP位于Cortex-M 的存储器系统和调试接口模块(SWJ-DP/SW_DP)之间,充当一个总线桥的角色,它把串行线/SWJ 接口的命令转换成 AHB 数据传送。对于大多数基本的在调试主机和Cortex-M系统之间的数据传输,只需要使用AHB-AP中的3个寄存器,它们是: 控制及状态字(CSW)

【ARM Coresight 系列文章 20.1 -- linux perf event 的注册】

文章目录 1.1 Perf 类型1.1.1 struct perf_event1.1.2 struct pmu 1.2 事件注册1.2.1 software 事件注册1.2.2 cpu_clock 事件注册1.2.2 task_clock 事件注册1.2.3 tp 事件注册1.2.3.1 tracepoint 事件 1.2.4 breakpoint 事件注册 1.3 Perf sys1.3.

【ARM Coresight 系列文章 9 -- ETM 介绍 1】

文章目录 ARM Coresight ETM 介绍1.1.1 ARM Coresight ETM 版本介绍1.1.2 ARM Coresight 常见术语 1.2 ARM Coresight ETM 常用寄存器介绍1.2.1 TRCVIIECTLR(ViewInst Include-Exclude Control Register)1.2.2 TRCVISSCTLR(ViewInst Sta

![[ARM系列]coresight(一)](https://img-blog.csdnimg.cn/direct/245c7881174f43dd990c83f0d531bac7.png)