本文主要是介绍基于IM模型的SNN脉冲神经网络的verilog程序开发,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

目录

1.SNN脉冲神经网络概述

2.verilog核心程序

1.SNN脉冲神经网络概述

脉冲神经网络大体上可以和传统的人工神经网络一样被用在信息处理中,而且脉冲神经网络可以对一个虚拟昆虫寻找食物的问题建模,而不需要环境的先验知识。并且,由于它更加接近现实的性能,使它可以用来学习生物神经系统的工作,电生理学的脉冲和脉冲神经网络在电脑上的模拟输出相比,决定了拓扑学和生物神经学的假说的可能性。

在实践中脉冲神经网络和已被证明的理论之间还存在一个主要的不同点。脉冲神经网络已被证明在神经科学系统中有作用,而在工程学中还无建树,一些大规模的神经网络已经被审计来利用脉冲神经网络中发现的脉冲编码,这些网络根据储备池计算 的原则,但是现实中,大规模的脉冲神经网络计算由于所需计算资源多而产能小被限制了,造成了只有很少的大规模脉冲神经网络被用来解决复杂的计算问题,而这些之前都是由第二代神经网络解决的。第二代神经网络模型中难以加入时间,脉冲神经网络(特备当算法定义为离散时间时)相当容易观察其动力学特征。我们很难建立一个具有稳定行为的模型来实现一个特定功能。

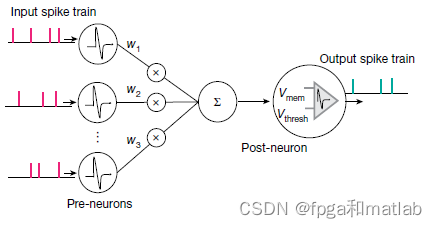

脉冲神经网络(SNN,Spiking Neural Network)是一种生物神经系统启发的神经网络模型,它使用脉冲事件(神经元之间的离散时间突触事件)来传递信息,与传统的人工神经网络(例如前馈神经网络和循环神经网络)不同。SNN的主要思想是模拟神经元之间的离散事件传递,这种传递方式更接近生物神经系统的工作方式。

IM模型(Integrate-and-Fire模型)是一种常用于描述神经元行为的数学模型之一。在IM模型中,神经元接收来自其他神经元的输入,将这些输入积累起来,当累积的电位超过某个阈值时,神经元会发放脉冲。

将IM模型与SNN相结合,可以创建基于IM模型的脉冲神经网络。这种模型通常由以下几个关键组件构成:

神经元模型(Integrate-and-Fire模型):每个神经元都使用IM模型来模拟其电位的积累和脉冲的发放。电位积累的速度取决于输入脉冲的权重和输入脉冲的时刻。一旦电位超过阈值,神经元会发放脉冲,并将电位重置为基线值。

突触权重:突触权重表示来自其他神经元的输入脉冲对目标神经元的影响程度。这些权重可以在训练过程中进行调整,以实现网络的学习。

时钟模拟:SNN模型通常需要一个时钟来模拟离散时间步骤。在每个时间步骤中,神经元接收来自其他神经元的输入,并根据IM模型更新其电位。

编码和解码:SNN通常使用不同于传统神经网络的编码和解码方案来处理输入和输出。例如,输入可以通过脉冲编码进行表示,而输出可以通过脉冲解码进行解释。

基于IM模型的SNN可以用于模拟生物神经系统中的信息处理和学习过程,尤其适用于事件驱动的任务,如感知、决策和控制。这种网络模型的应用领域包括神经计算、生物医学工程、感知计算等。需要注意的是,构建和训练SNN可能比传统神经网络更具挑战性,因为涉及到脉冲编码和时钟驱动的计算。

2.verilog核心程序

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2020/07/21 07:25:33

// Design Name:

// Module Name: SNN_IM

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module SNN_IM(

input i_clk,

input i_rst,

input[9:0]i_X,

input[9:0]i_Y,

output signed[31:0]o_v,

output signed[31:0]o_u,

output signed[31:0]o_vL,

output checker,

output[15:0]cntc,

output [15:0]cnt2

);

wire[9:0]xy;

assign xy=i_X[9:1]+i_Y[9:1];

wire signed[15:0]o_stn1,o_stn2,o_stn3;

LUT LUT_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_xy (xy),

.o_stn1 (o_stn1),

.o_stn2 (o_stn2),

.o_stn3 (o_stn3)

);

//FIFO

wire signed[15:0]Spike1,Spike2,Spike3;

fifo_generator_0 fifo_generator_0_u1 (

.clk(i_clk), // input wire clk

.srst(i_rst), // input wire srst

.din(o_stn1), // input wire [15 : 0] din

.wr_en(1'b1), // input wire wr_en

.rd_en(1'b1), // input wire rd_en

.dout(Spike1), // output wire [15 : 0] dout

.full(), // output wire full

.empty() // output wire empty

);

fifo_generator_0 fifo_generator_0_u2 (

.clk(i_clk), // input wire clk

.srst(i_rst), // input wire srst

.din(o_stn2), // input wire [15 : 0] din

.wr_en(1'b1), // input wire wr_en

.rd_en(1'b1), // input wire rd_en

.dout(Spike2), // output wire [15 : 0] dout

.full(), // output wire full

.empty() // output wire empty

);

fifo_generator_0 fifo_generator_0_u3 (

.clk(i_clk), // input wire clk

.srst(i_rst), // input wire srst

.din(o_stn3), // input wire [15 : 0] din

.wr_en(1'b1), // input wire wr_en

.rd_en(1'b1), // input wire rd_en

.dout(Spike3), // output wire [15 : 0] dout

.full(), // output wire full

.empty() // output wire empty

);

wire clkk;

IM IM_u(

.i_clk(~i_clk),

.i_rst(i_rst),

.Isyn0 (32'd50000),

.i_stn1 (Spike1),

.i_stn2 (Spike2),

.i_stn3 (Spike2),

.o_v (o_v),

.o_u (o_u),

.o_vL (o_vL),

.cnt2(cnt2)

);

通过spike模块控制模块产生最后的识别判决输出结果

controller2 controller2_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_Vtn1 (o_vL[24:9]),

.i_lvl (16'd5000),//5000

.i_reg (16'd6000), //10000

.cntc (cntc),

.checker (checker)

);

endmodule

A05-107

这篇关于基于IM模型的SNN脉冲神经网络的verilog程序开发的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!