本文主要是介绍FPGA(二):Vivado 软件中RTL详细描述(RTL ANALYSIS)板块分析,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

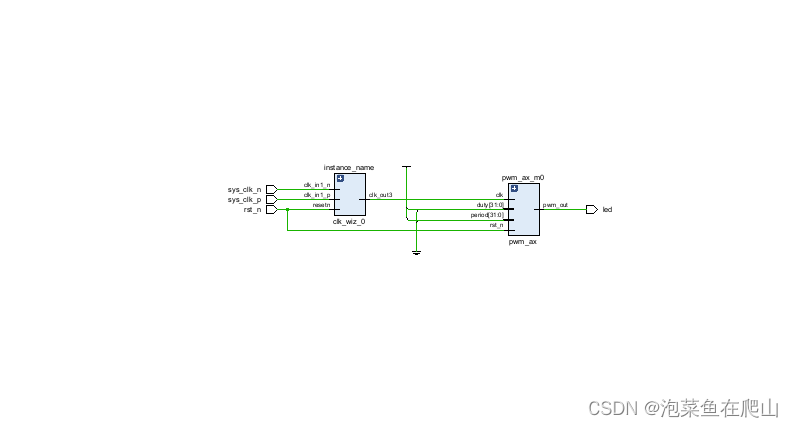

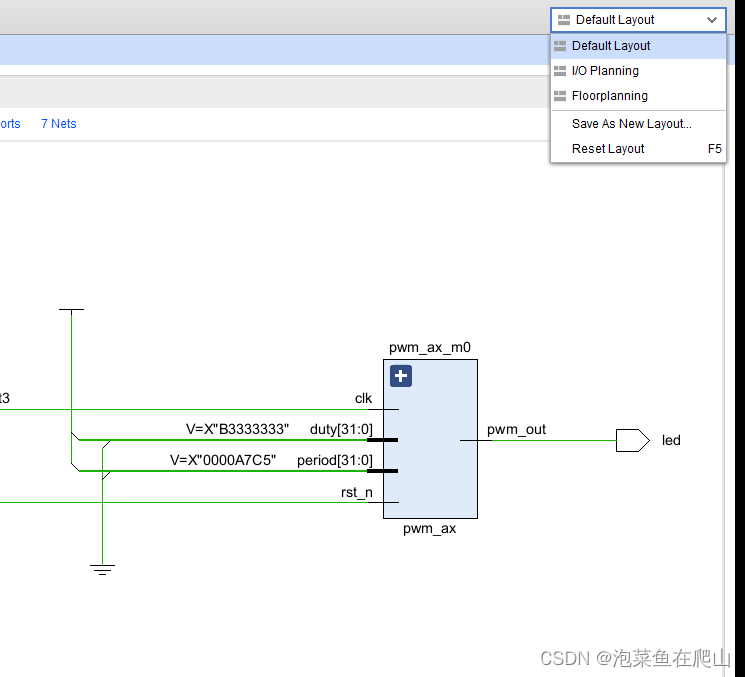

通俗来说,RTL 分析就是看到自己通过硬件描述语言写的程序,转换成基本电路(这里声明基本电路是指不经过任何转换的,取反就是非门,不涉及查找表之类,后续会有综合,综合中叫高级电路),可以看到原理图,这一步可以进行I/O口的绑定。

详细描述(ELABORATED)是指将RTL优化到FPGA技术。在软件中主要有以下功能:

1.人员导入和管理RTL源文件。

2.通过RTL修改源文件

3.源文件视图。

在基于RTL的设计中,当用户打开一个详细描述的RTL时,开发环境会加载RTL网表(包含单元、引脚、端口和网络)

1.详细描述(Elaborated)的实现

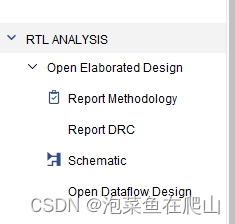

当点击完"Open Elaborated Design"后会自动打开Schematic 界面,也可以看到对应生成的网表结构。

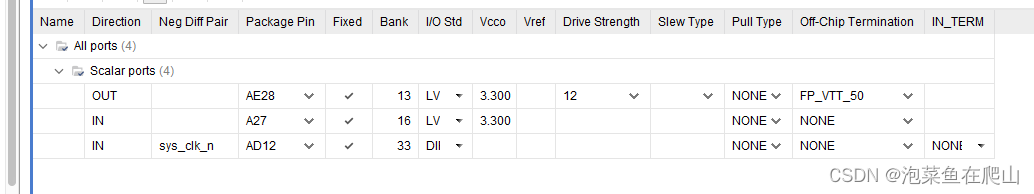

这一步后进行I/O口绑定,相关菜单栏如下所示。

绑定管脚时候要注意,电瓶的选择以及FPGA管脚,在这里需要注意,原理图,一些外设的引脚在底板上寻找,时钟、DDR等在核心板上寻找。

2.其他功能

这RTL ANALYSIS 这个板块中,还有一些检查类的功能。比如

Report DRC:运行设计检查规则,并报告检查结果。

Report Noise: 基于XDC文件,在设计上检查SSO(同时开关输出)

3.生成HDL定制化模板

在传统的ISEK开发环境中,提供了从用户自己设计的Verilo HDL 代码中生成HDL 例化模板,在vivado 中需要通过TCL命令才能从用户自己设计的代码中生成例化模板。

这篇关于FPGA(二):Vivado 软件中RTL详细描述(RTL ANALYSIS)板块分析的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!