本文主要是介绍硬件描述语言:elaborate和synthesis电路图的区别、latch问题、always组合逻辑默认值写法、Vivado和Quartus的电路图区别,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

题目来自:Ringer - HDLBits

Suppose you are designing a circuit to control a cellphone’s ringer and vibration motor. Whenever the phone needs to ring from an incoming call (input ring), your circuit must either turn on the ringer (output ringer = 1) or the motor (output motor = 1), but not both. If the phone is in vibrate mode (input vibrate_mode = 1), turn on the motor. Otherwise, turn on the ringer.

下面使用Vivado来elaborate(详细描述)和synthesis(综合),也是用Quartus来Analysis & Synthesis

一、assign写法

module top_module (input ring,input vibrate_mode,output ringer, // Make soundoutput motor // Vibrate

);assign ringer = ring & !vibrate_mode;assign motor = ring & vibrate_mode;

endmodule

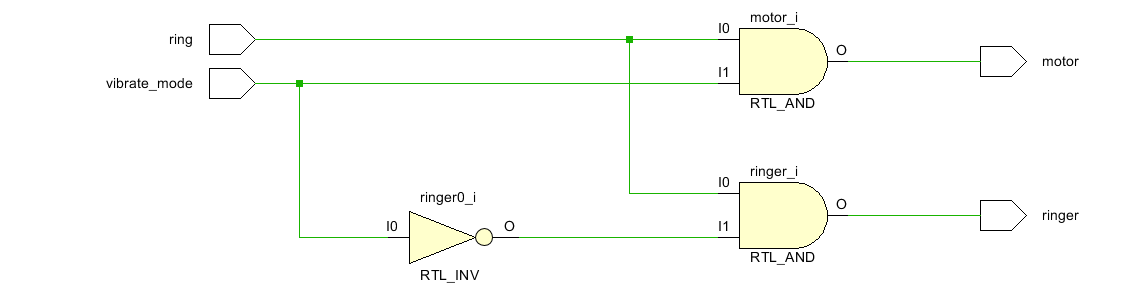

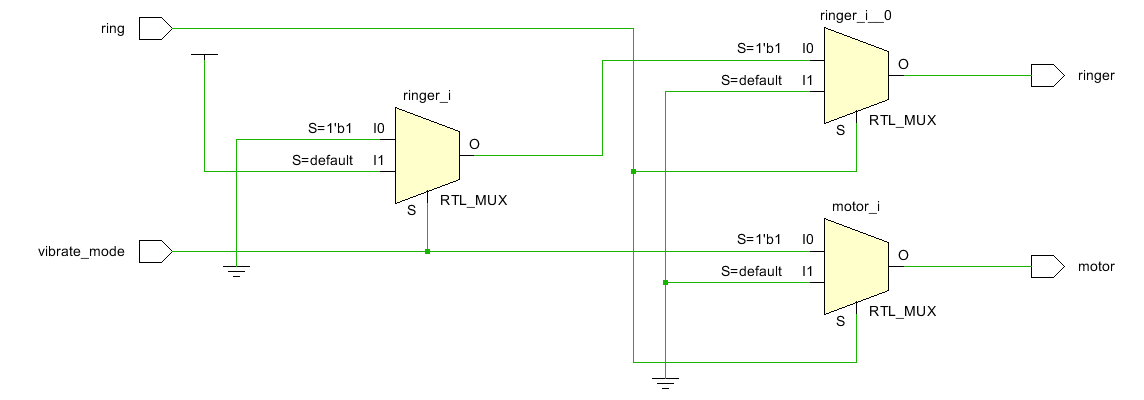

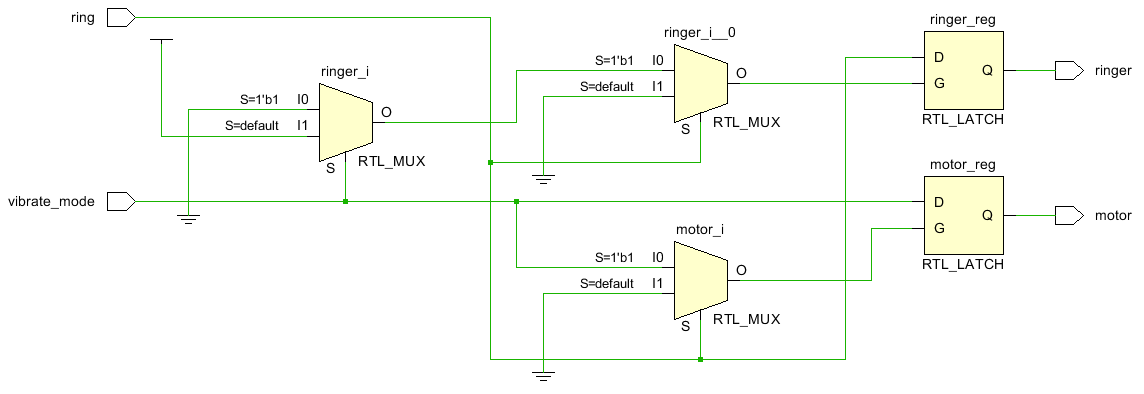

elab电路图

黄色的图是Vivado的elaborate步骤出的电路图;

蓝色的图是Quartus的RTL Viewer出来的图;

Vivado和Quartus的电路图区别:Quartus的图看起来会稍微简洁一点点;

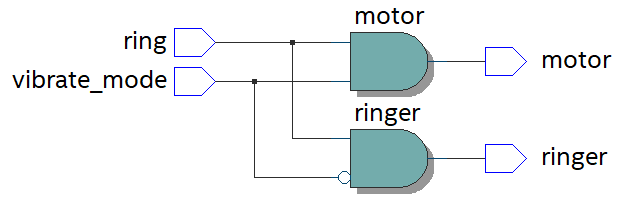

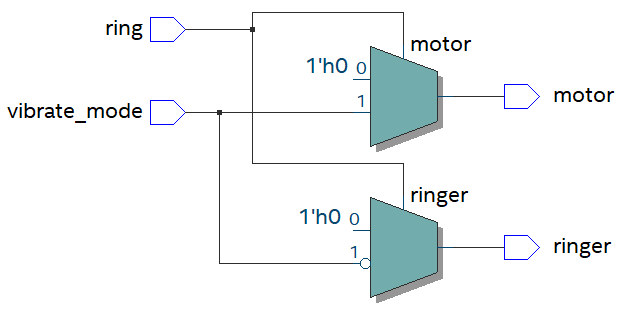

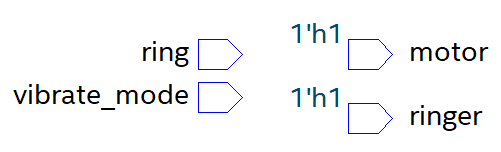

synth电路图

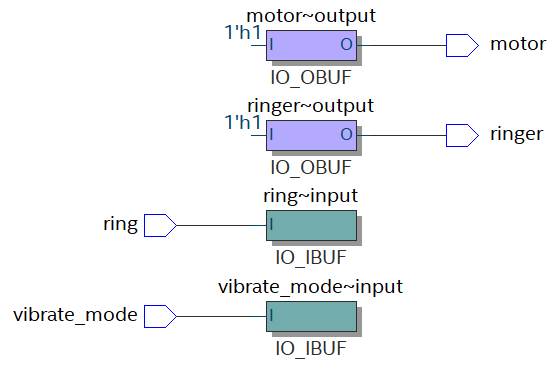

黄色的图是Vivado的synthesis步骤出的图;

紫色这张图是Quartus的Technology Map Viewer (Post-Mapping)出来的图;

图里的IBUF和OBUF可以忽略掉,这是综合工具自动加上去的。

二、always @(*)组合逻辑写法

module top_module (input ring,input vibrate_mode,output reg ringer, // Make soundoutput reg motor // Vibrate

);always @(*) beginringer = 0; motor = 0;if (ring)if (vibrate_mode)motor = 1;elseringer = 1;end

endmodule

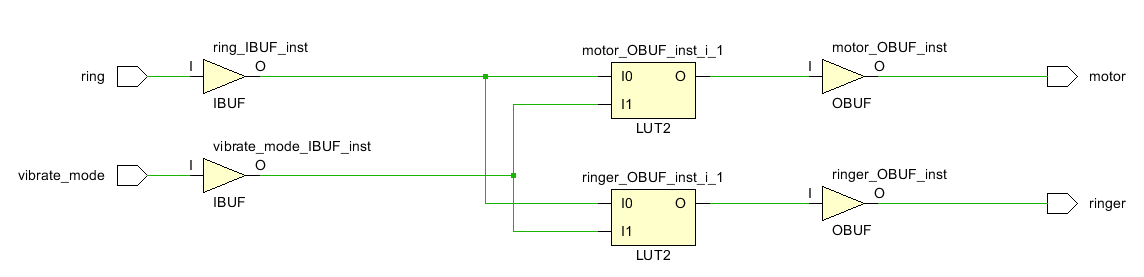

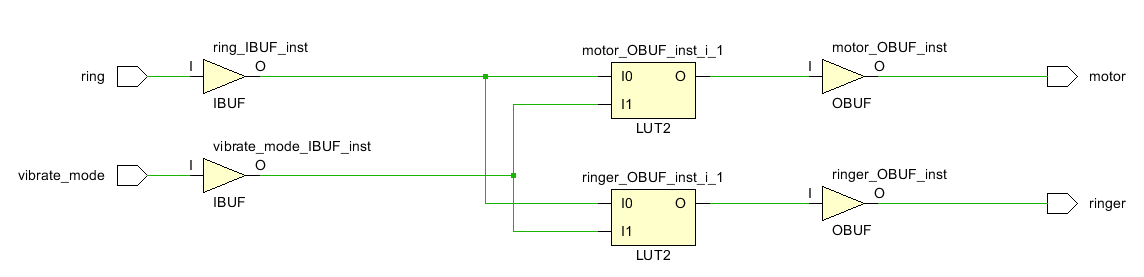

elab电路图

synth电路图

这两个电路图是第一种写法的图是一样的。

小结论:elaborate和synthesis电路图的区别

对比一和二两种写法,可以看到elab阶段的电路图是从RTL代码分析的,所以两个电路图看起来有点不一样(仔细看可以发现功能是一样的),而综合synth阶段的电路图是一样的,因为综合的确是分析了电路的功能,用具体的器件来实现功能了。

三、latch问题

module top_module (input ring,input vibrate_mode,output reg ringer, // Make soundoutput reg motor // Vibrate

);always @(*) begin// ringer = 0; motor = 0;if (ring)if (vibrate_mode)motor = 1;elseringer = 1;end

endmodule

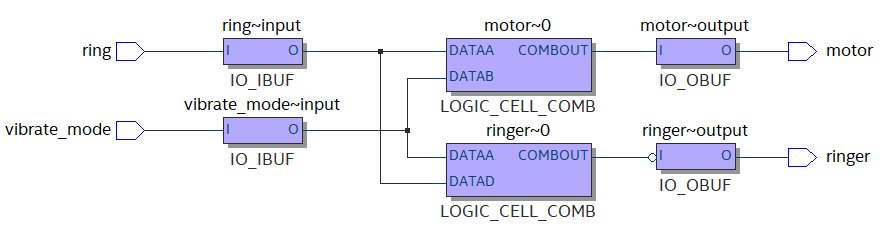

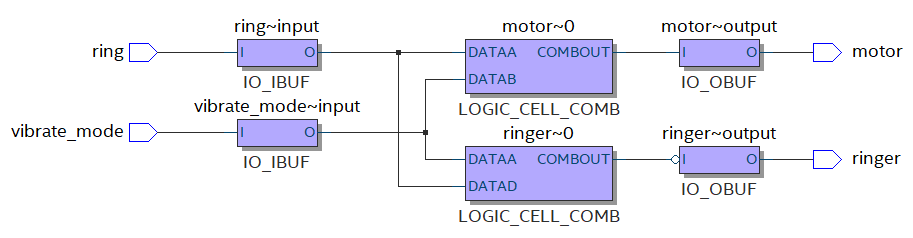

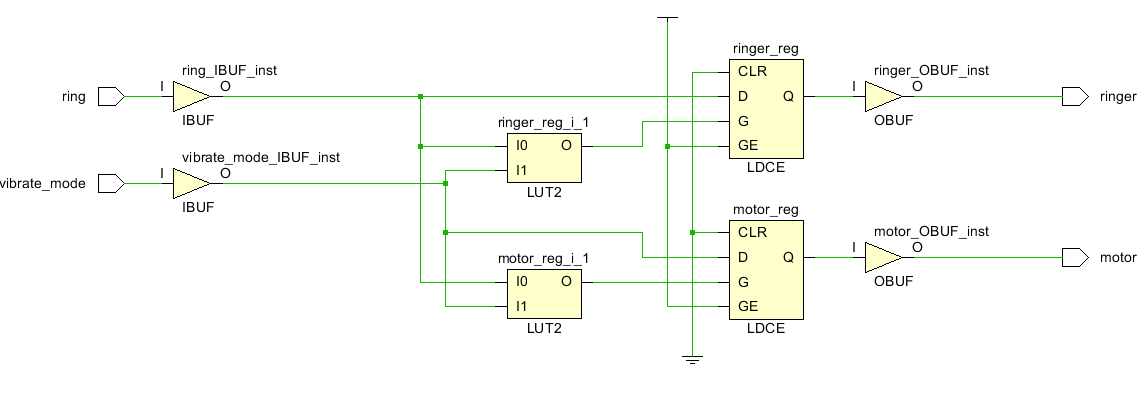

elab电路图

Quartus出的这个图很简洁,直接给了输出1。两个工具都发现了Latch的存在,报了Warning。

synth电路图

小结论:latch问题、always组合逻辑默认值写法

可以看到,如果不把 if else 或 case 写完整的话,会产生latch。

always @(*)组合逻辑写法中,默认值的写法可以学一下。下面再举一个默认值写法的例子:Always nolatches - HDLBits。

module top_module (input [15:0] scancode,output reg left,output reg down,output reg right,output reg up ); always @(*) beginleft = 0; down = 0; right = 0; up = 0; // 这里是默认值,节省了很多default写法case (scancode)16'he06b: left = 1;16'he072: down = 1;16'he074: right = 1;16'he075: up = 1;endcaseend

endmodule

注:CSDN博客竟然不支持Verilog的高亮???其他语言,例如C/C++可以

这篇关于硬件描述语言:elaborate和synthesis电路图的区别、latch问题、always组合逻辑默认值写法、Vivado和Quartus的电路图区别的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!