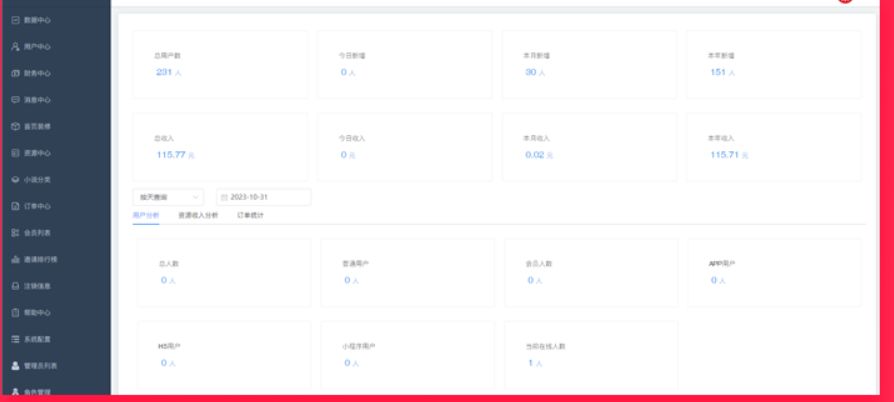

本文主要是介绍阅读日记:computer organization and design——RISC-V——chapter4-2,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

4.2 Logic Design Conventions

为了讨论计算机的设计,我们必须决定实现计算机的硬件逻辑是如何工作的,以及计算机是如何计时的。本节回顾了数字逻辑中的一些关键思想,我们将在本章中广泛使用这些思想。如果你很少或没有数字逻辑的背景,你会发现在继续之前阅读附录A是有帮助的

RISC-V实现中的数据路径元素由两种不同类型的逻辑元素组成:elements that operate on data values and elements that contain state.

1)The elements that operate on data values are all combinational,(An operational element, such as an AND gate or an ALU

)这意味着它们的输出只依赖于当前的输入。给定相同的输入,组合元素总是产生相同的输出。因为它没有内部存储器。

2)elements that contain state. :我们可以选择保存并恢复状态元素,就好像计算机从未断电一样。因此,这些状态元素完全表征了计算机。在图4.1中,指令和数据存储器以及寄存器都是状态的例子

状态元素至少有两个输入和一个输出。The required inputs are the data value to be written into the element and the clock, which determines when the data value is written.

The output from a state element provides the value that was written in an earlier clock cycle.

包含状态的逻辑组件也被称为顺序的,因为它们的输出依赖于它们的输入和内部状态的内容。例如,表示寄存器的功能单元的输出既取决于提供的寄存器号,也取决于先前写入寄存器的内容。

Clocking Methodology

The approach used to determine when data are valid and stable relative to the clock.

定义何时可以读取和何时可以写入信号。指定读和写的时间是很重要的,因为如果在读信号的同时写入信号,则读的值可能与旧值、新写入的值或两者的某些混合值相对应!计算机设计不能容忍这种不可预测性。为了使硬件具有可预测性,设计了一种时钟方法是必要的。

edge-triggered clocking:一种时钟方案,其中所有的状态变化都发生在时钟边缘。

为了简单起见,我们假设一个边缘触发时钟方法论。边缘触发时钟方法意味着存储在顺序逻辑元件中的任何值仅在时钟边缘上更新,时钟边缘是从低到高或从低到高的快速转换(见图4.3)。因为只有状态元素才能存储数据值,所以任何组合逻辑集合的输入都必须来自一组状态元素,其输出必须写入一组状态元素。输入是在前一个时钟周期中写入的值,而输出是可以在下一个时钟周期中使用的值。

图4.3显示了在一个时钟周期内工作的组合逻辑块周围的两个状态元素:所有信号必须在一个时钟周期内从状态元素1通过组合逻辑传播到状态元素2。信号到达状态元件2所需的时间定义了时钟周期的长度。

control signal:用于多路复用器选择或指示功能单元的操作;与包含由功能单元操作的信息的数据信号形成对比

时钟信号和写入控制信号都是输入,并且只有当写入控制信号是逻辑高并且时钟边缘发生时,状态元素才被改变。我们将使用asserted这个词来表示逻辑上高的信号,assert指定一个信号应该被逻辑上高的驱动,deassert或deasserted表示逻辑上低的

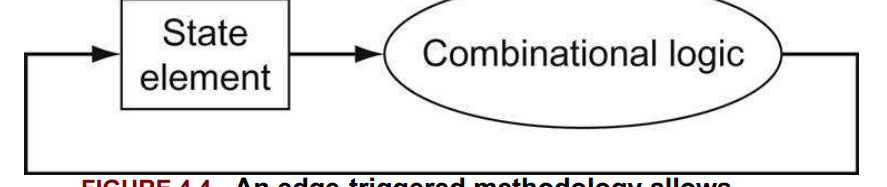

An edge-triggered methodology允许我们读取寄存器的内容,通过某种组合逻辑发送值,并在同一个时钟周期内写入该寄存器。图4.4给出了一个通用示例。不管我们假设所有写操作都发生在上升的时钟边缘(从低到高)还是下降的时钟边缘(从高到低)(since the inputs to the combinational logic block cannot change except on the chosen clock edge.)在这本书中,我们使用上升的时钟边缘。

4.4

FIGURE 4.4 An edge-triggered methodology allows a state element to be read and written in the same clock cycle without creating a race that could lead to indeterminate data values. Of course, the clock cycle still must be long enough so that the input values are stable when the active clock edge occurs. 一个周期内是可读可写的,但是时钟周期要足够长,因为必须保证当时钟边缘来的时候输入值是稳定的。

说明:

对于64位RISC-V体系结构,几乎所有这些状态和逻辑元素都有64位宽的输入和输出.当一个单元的输入或输出的宽度不是64位时,我们会说清楚。有时,我们希望组合多个总线以形成更宽的总线;例如,我们可能希望通过组合两个32位总线来获得64位总线。Finally, color indicates a control signal contrary to a signal that carries data

这篇关于阅读日记:computer organization and design——RISC-V——chapter4-2的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!