risc专题

RISC-V (十二)系统调用

系统模式:用户态和内核态 当前的代码都是实现在machine模式下。 系统模式的切换 epc寄存器的值存放的是ecall指本身的地址 。 用ecall指令 系统调用的执行流程 mret这条指令会利用status的mpp值恢复到之前的特权级别。 蓝色的线表示涉及到权限切换。 系统调用的传参

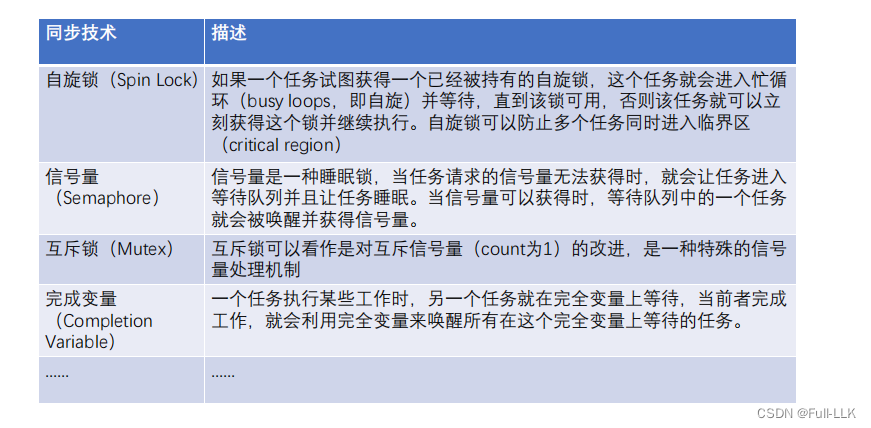

RISC-V (十)任务同步和锁

并发与同步 并发:指多个控制流同时执行。 多处理器多任务。一般在多处理器架构下内存是共享的。 单处理器多任务,通过调度器,一会调度这个任务,一会调度下个任务。 共享一个处 理器一个内存。 单处理器任务+中断: 同步: 是为了保证在并发执行的环境中各个控制流可

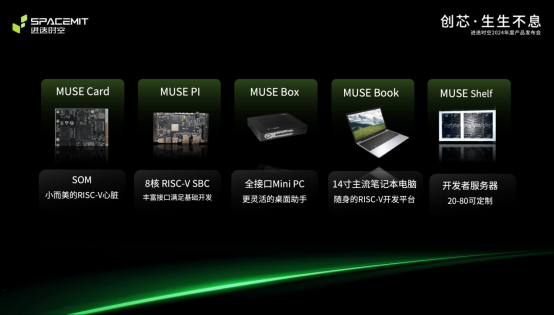

Banana Pi BPI-F3 进迭时空RISC-V架构下,AI融合算力及其软件栈实践

RISC-V架构下,AI融合算力及其软件栈实践 面对未来大模型(LLM)、AIGC等智能化浪潮的挑战,进迭时空在RISC-V方向全面布局,通过精心设计的RISC-V DSA架构以及软硬一体的优化策略,将全力为未来打造高效且易用的AI算力解决方案。目前,进迭时空已经取得了显著的进展,成功推出了第一个版本的智算核(带AI融合算力的智算CPU)以及配套的AI软件栈。 软件栈简介 AI算法部署旨

RISC-V (八)定时器中断

riscv中断的分类 Core local INTerrupt: CLINT CLINT编程接口-寄存器 mtime寄存器,由中断触发的时钟,按照固定频率计数。

RISC-V汇编实现矩阵阶乘

1) 源代码 long long fact(long long n) {if (n < 1) return 1;else return (n*fact(n - 1));} 2) 汇编代码 fact:addi sp, sp, -16 // adjust stack for 2 itemssd x1, 8(sp) // save the return add

推动RISC-V CPU性能快速提升并向上打开更多的高价值市场

作者:Imagination Technologies 8月21-23日,2024年RISC-V中国峰会在杭州黄龙饭店举行。作为已推出多款Imagination Catapult系列RISC-V CPU半导体知识产权(IP)的提供商,以及全球领先的GPU和AI加速器IP厂商,Imagination Technologies积极参与了此项中国大陆规格最高、规模和影响力最大的专业会议之一,并在大会现

RISC-V (七)外部设备中断

中断的分类 -本地中断 -software interrupt(软终端) -timer interrupt(定时器中断) -全局中断 -external interrupt(外部中断 ) qemu主要是参考FU540-C000这款芯片做

RISC-V全志D1多媒体套件文章汇总

提示 此开发板的任何问题都可以在我们的论坛交流讨论 https://forums.100ask.net/c/aw/d1/57 文章目录汇总 教程共计4章,下面是章节汇总: 第0章_RISC-V全志D1多媒体套件 第1章_快速启动 第2章_安装并配置开发环境 第3章_Tina-SDK开发 为了更好的阅读体验,我们提供了在线文档阅读https://dshanpi.100ask.net/

RISC-V vector(1) --- vector的引入与register说明

Vector相较于SIMD的优势 这两种实现方案,都是为了实现数据级并行性(存在大量的数据可供程序同时计算); SIMD(Single Instruction Multiple Data) SIMD是将数据宽度和操作类型,都放在了指令中; SIMD技术最初通过将64位寄存器的数据拆分成多个8位、16位、32位的形式来实现byte、half word、

RISC-V中的acquire和release

RISC-V中,有两类原子操作指令: ⚫ 内存原子操作(AMO) ⚫ 加载保留/条件存储(load reserved / store conditional) 此处我们先看下LR和SC指令; 引入的原因 编程语言的开发者会假定体系结构提供了原子的比较-交换(compare-and-swap)操作: 比较一个寄存器中的值和另一个寄存器中的内存地址指向的值,如果

RISC-V教学内容及短视频吸引因素

RISC-V 教学内容 在我的认知中,大多数人对RV仍然了解甚少,我想本实习岗位主要面向对 RV 不了解或了解很少的同学,帮助大家更好入门。 因此教学内容为: RISC-V 简要介绍;RISC-V 指令集知识简要讲解,指令集介绍,各个指令集的指令规则及指令运行演示,可以结合模拟器运行结果讲解更为直观;常见 RV 模拟器介绍,分别适用的场景。对于一些简单的 RV 模拟器可以展开讲解安装部署使用

【Rust日报】2020-10-28 RustSBI项目已进入RISC-V SBI标准

RustSBI项目已进入RISC-V SBI标准 RISC-V指令集的SBI标准规定了类Unix平台下,操作系统运行环境的规范。目前,RustSBI项目已获得SBI编号4,代表它已经被收录入RISC-V SBI标准。 RISC-V架构中,存在着定义于操作系统之下的运行环境。这个运行环境不仅将引导启动RISC-V下的操作系统,还将常驻后台,为操作系统提供一系列二进制接口,以便其获取和操作硬件信息。

【Rust日报】2021-01-26 太素桌面系统:基于RISC-V架构的Rust系统内核

太素桌面系统:基于RISC-V架构的Rust系统内核(十二) 编写“太素”桌面操作系统的文章更新到第十二期。本期文章在前文成果的基础上,开始编写一个简单的桌面系统结构。这包括桌面、窗口和其中的控件,以及文字标签的显示方式。 太素OS是一个RISC-V架构、Rust编写的操作系统内核。作者在系列文章中介绍,“太素”的名字来源于道家五太之一,可以演化万物。这个项目实现了包含图形处理器在内的外部设备控

deepin 加入甲辰计划,共建 RISC-V 繁荣生态

内容来源:deepin(深度)社区 今日,deepin(深度)社区宣布正式加入甲辰计划,致力于在下一个丙辰年(2036龙年)之前,基于RISC-V实现从数据中心到桌面办公、从移动穿戴到智能物联网全信息产业覆盖的开放标准体系及开源系统软件栈,使RISC-V软硬件生态达到作为主流指令集架构所需的生态成熟度。 deepin(深度)社区成立于2008年,在电脑操作系统开发领域经验沉

01_RISC-V 入门及指令集学习

参考文档 risc-v入门:https://blog.csdn.net/bebebug/article/details/128039038RISC-V OS:https://blog.csdn.net/bebebug/article/details/130551378riscv-spec文档:https://riscv.org/wp-content/uploads/2019/12/riscv-s

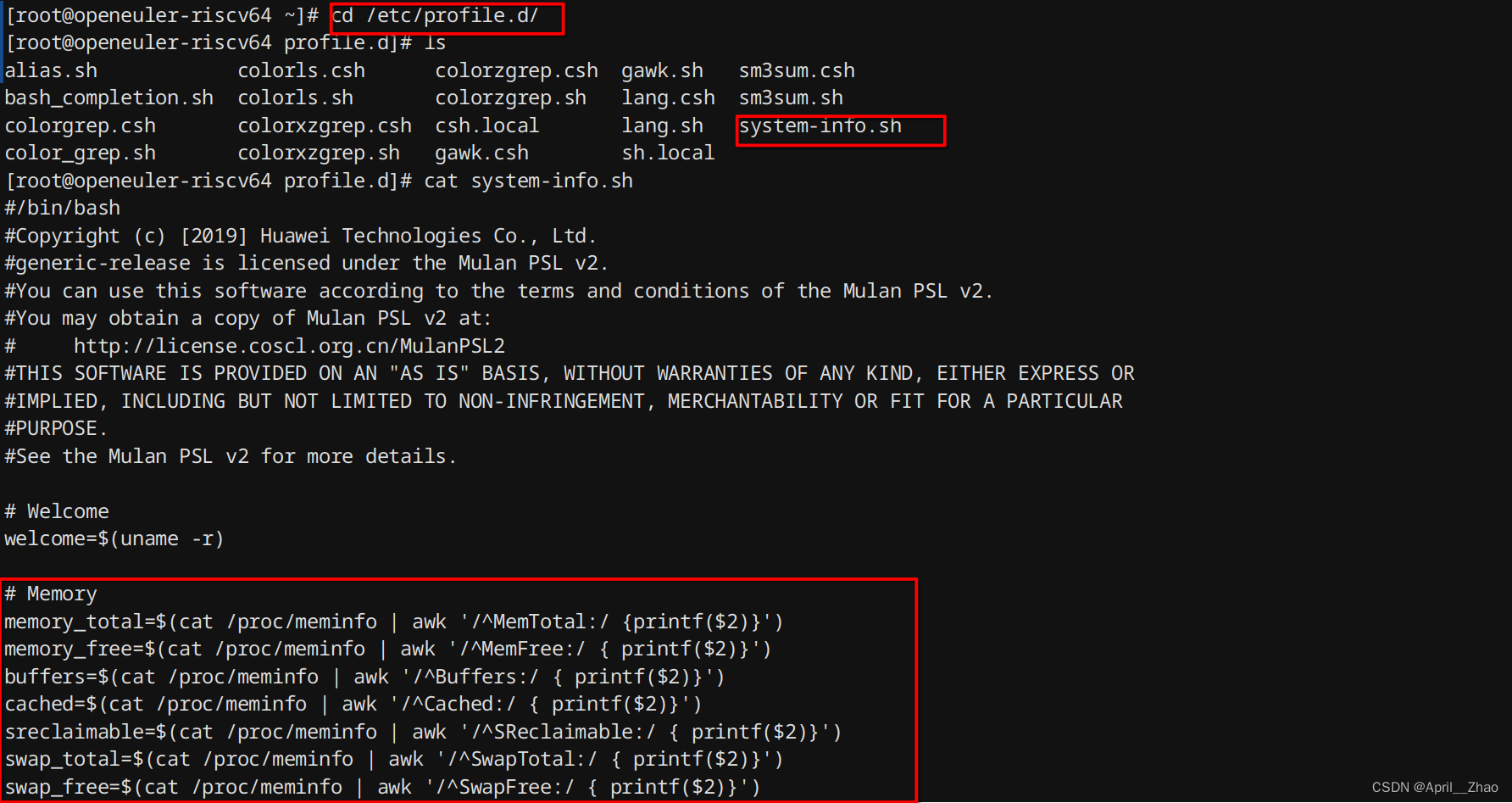

【跟我学RISC-V】(三)openEuler特别篇

写在前面 这篇文章是跟我学RISC-V指令集的第三期,距离我上一次发文已经过去一个多月了,在这个月里我加入了oerv的实习项目组,并且还要准备期末考试,比较忙。 在这篇文章里我会隆重、详细地介绍一个对RISC-V支持非常友好的Linux发行版,同时也是国产操作系统 — openEuler.在此之前我都是使用我最熟悉的Fedora,在x86上Fedora确实非常好用、体验好,但是在RISC-V上总

Linux Kernel入门到精通系列讲解(RV-Kernel 篇) 5.1 从零移植 Linux kernel,基于RISC-V

1. 概述 上一章节我们已经将u-boot部署好了,本章节,我们将从零移植Naruto-Pi的Linux kernel,移植通用RISCV很简单,在移植之前,大家也可以参考我之前写的文章,Linux ARM平台开发系列讲解(QEMU-体验篇) 1.1 编译QEMU 构建RISC-V64架构 运行Linux kernel 2. Linux kernel 下载地址 本章节下载的是最新的Lin

RISC-V基础编译

RISCV编译 1、 编译步骤2、重要配置3、elf-gcc和linux-gnu-gcc的区别 1、 编译步骤 mkdir build installcd build../riscv-gnu-toolchain/configure--prefix=/xxx/install --with-arch=rv32gc --with-abi=ilp32d --enable-debug

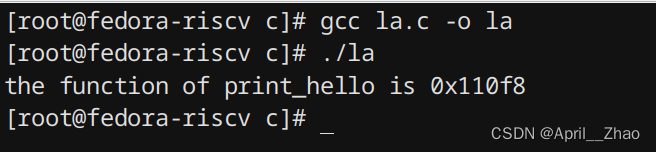

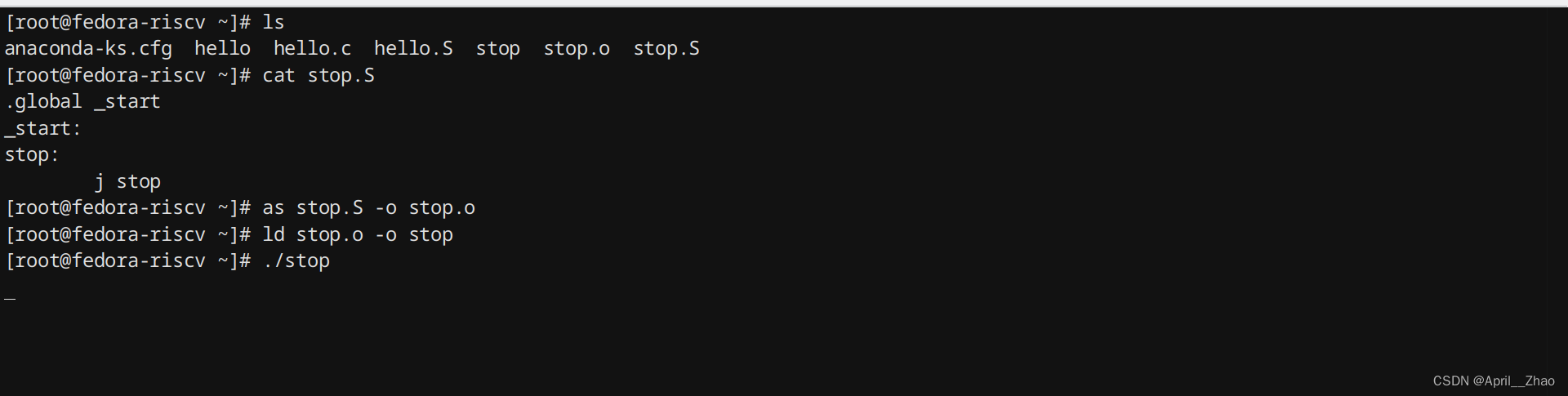

【跟我学RISC-V】(二)RISC-V的基础知识学习与汇编练习

写在前面: 这篇文章是跟我学RISC-V的第二期,是第一期的延续,第一期主要是带大家了解一下什么是RISC-V,是比较大体、宽泛的概念。这一期主要是讲一些基础知识,然后进行RISC-V汇编语言与c语言的编程。在第一期里我们搭建了好几个环境,你可以任意选一个你喜欢的RISC-V环境(能够执行RV机器码的平台),然后进行代码编写、编译、汇编、链接、运行、观察现象的这一过程。同样地,在这一篇里我也会拿

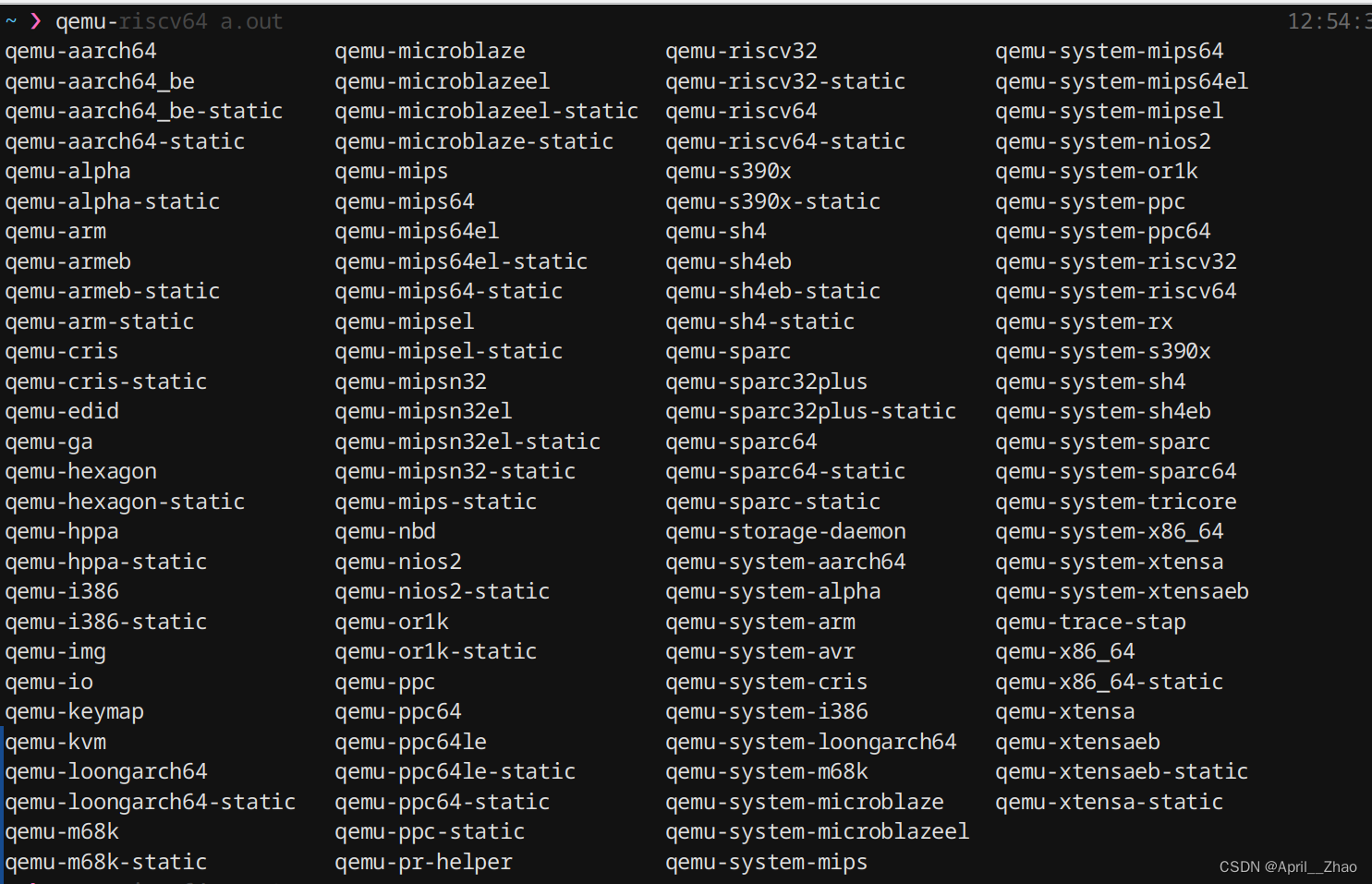

【跟我学RISC-V】(一)认识RISC-V指令集并搭建实验环境

写在前面 现在计算机的体系架构正是发展得如火如荼的时候,占领桌面端市场的x86架构、占领移动端市场的arm架构、在服务器市场仍有一定地位的mips架构、国产自研的指令集loongarch架构、还有我现在要讲到的新型开源开放的RISC-V指令集架构。 我先说一说我的学习经历,三年前我开始学习x86架构,不得不说x86架构这么多年的发展变得是真的非常复杂和难以概括,它为了兼容性,不得不保留一些早期

RT-thread移植指南-RISC-V

目录 RT-thread移植指南-RISC-V 1. 概述 1.1 移植资料参考 1.2 移植开发环境准备 2. 移植步骤 2.1 全局中断开关函数 2.2 线程上下文切换函数 2.3 线程栈的初始化 2.4 时钟节拍的配置 2.5 中断函数(中断时现场保护、中断注册和使能) 2.5.1 interrupt_gcc.S: 2.5.2 中断注册、使能、和分发 2.6 R

【跟我学RISC-V】认识RISC-V指令集并搭建实验环境

写在前面 现在计算机的体系架构正是发展得如火如荼的时候,占领桌面端市场的x86架构、占领移动端市场的arm架构、在服务器市场仍有一定地位的mips架构、国产自研的指令集loongarch架构、还有我现在要讲到的新型开源开放的RISC-V指令集架构。 我先说一说我的学习经历,三年前我开始学习x86架构,不得不说x86架构这么多年的发展变得是真的非常复杂和难以概括,它为了兼容性,不得不保留一些早期

进迭时空宣布开源RISC-V芯片的AI核心技术

仟江水商业电讯(4月29日 北京 委托发布)4月29日,在“创芯·生生不息——进迭时空2024年度产品发布会”上,进迭时空CEO、创始人,陈志坚博士宣布将开源进迭时空在自研RISC-V AI CPU上的核心技术,包括AI扩展指令和全部AI软件栈代码,助力RISC-V生态建设。为了RISC-V开发者们便捷使用这些AI代码,进迭时空正在做代码整理,预计最晚将在今年Q4季度开源所有AI软

WCH RISC CH32V303RCT6 单片机的SDI Printf 虚拟串口功能 类似RTT打印功能 简单分析

参考: 有关于 SDI printf 更多的信息和资料吗? 关于 CH32 系列 MCU SDI 虚拟串口功能的使用 【CH32X035 评估板测评】+ 教你使用 SDI 接口重定向 printf 0.前言 有段时间没有看CH32V单片机的开发了,今天帮新来的同事调试时候看到debug.c里面有新的函数SDI_Printf_Enable: 大概看了下,感觉有点像RTT,去wch官方那个

制作一个RISC-V的操作系统十四-任务同步和锁

文章目录 并发与同步临界区和锁锁死锁解决死锁自旋锁(spin lock)原子性问题原子操作实现amoswap.w.aq例子 另一种方法自旋锁的注意事项代码其他同步技术 并发与同步 控制流:可理解为任务或进程 中断也可以理解为一个切换到另一个任务(中断处理程序),于是宏观上认为同时执行了 同步:可以理解要求某个任务的某个操作与某个任务的某个操作的先后顺序有要求 临界区和锁

在RISC-V64架构的CV1811C开发板上应用perf工具进行多线程程序性能分析及火焰图调试

CV1811C环境编译 SDK目录结构 .├── build // 编译目录,存放编译脚本以及各board差异化配置├── buildroot-2021.05 // buildroot开源工具├── freertos // freertos系统├── fsbl // fsbl启动固件,prebuilt形