本文主要是介绍#systemverilog# 之 event region 和 timeslot 仿真调度(三)Verdi 辅助查看,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

前面的几篇文章,我们对SV仿真调度进行了理论分析和实战演练。那么工具厂商,对该类问题有没有提供相应的支持。这个应该是肯定的。因为我们知道,SV只是出于定义标准的角度,规定了仿真调度事件原理。但是具体实施细节,应是每家EDA仿真工具厂商根据自家的软件开发算法而定的。所以,EDA厂商也是很容易来做这件事的。VCS+Verdi工具,便提供了相应的feature,今天我们来学习和总结一下。

一 event sequence

为了想观测某个timeslot 处的所有event 的执行具体顺序是什么样子的,我们可以在仿真阶段通过传递 VCS 仿真参数 +fsdb+sequential ,其主要用于记录同一时刻下,信号变化的先后顺序。

.simv ... +fsdb+sequential ....

大家可以自行拿自己身边的例子来跑跑看,这里就不在贴具体代码。直接分析结果:

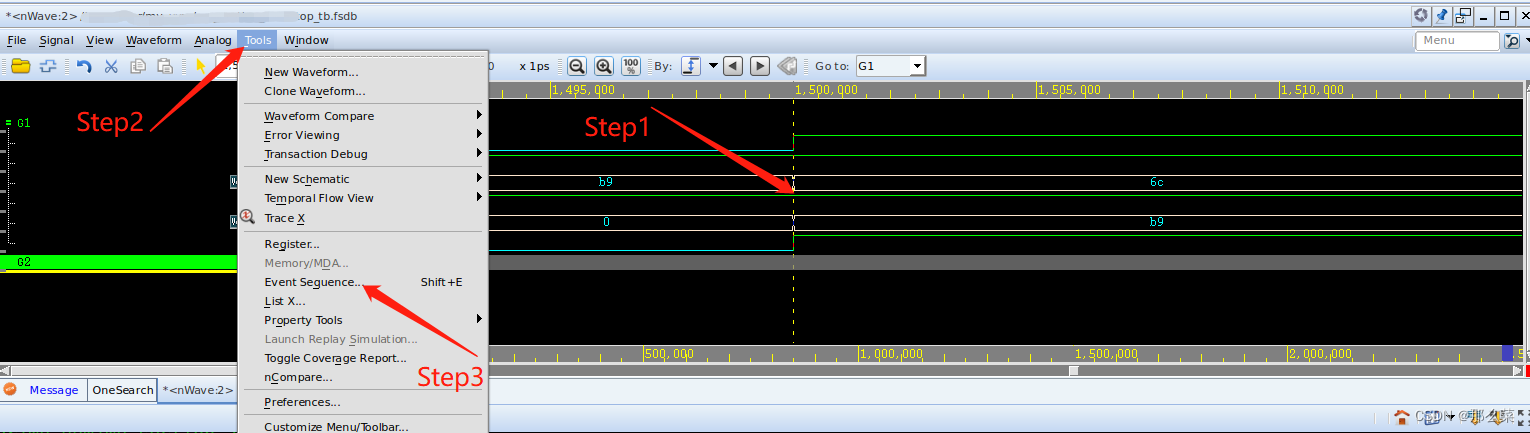

如上图所示,我们分别按照 step1:鼠标左键单击选中要分析的波形时间点; Step2: 点击 nWave窗口中的 tool菜单,并找到Event Sequence... 选项, 点击按钮,然后窗口弹出下图指示的event sequence 执行序列。

这篇关于#systemverilog# 之 event region 和 timeslot 仿真调度(三)Verdi 辅助查看的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!