verdi专题

verdi windows版本[使用debussy 5.4]

linux下习惯用cadence的ncverilog电路图方式,分析代码信号的drive和load。 windows下,可以学习一下debussy(verdi前身)。听说大公司,都推荐verdi,所以即便不是最喜欢,也要了解。因为很多人给你讲解代码的时候,他们使用verdi,fxxk。 so,let’s enjoy it。改变不了环境,就适应它。 百度云,真是个好东西。很多eda工具的破解版

ubuntu 20.04 安装 VCS + Verdi

Ubuntu16.04安装VCS和Verdi Ubuntu 16.04 VCS+Verdi安装总结 - 灰信网(软件开发博客聚合)

verdi编译vhdl文件时,报出warning:*Warn* Unknown argument –vhdl08的解决 办法

原因分析: verdi -help打印出的帮助信息中可找到-vhdl08,但根据上下文可看到该选项是 nTrace工具的选项。所以命令如“verdi -vhdl08 -f include.f"会报出warning。解决办法: 使用verdi的vhdlcom工具来编译vhdl。例如: vhdlcom -vhdl08 top_design.vhd 然后再通过库调用的方式打

verdi加载vhdl和verilog混合RTL设计的方法

采用三步法完成混合语言RTL设计的加载。 step1. 用vhdlcom将所有的VHDL RTL代码编译成库 1.1 将所有的vhdl文件放到vhdl.f文件中,如: vhdl.f --------- my_design.vhd my_lib.vhd tb_my_design.vhd 1.2 编译成库

vcs编译systemverilog并且用verdi查看波形

转载自:http://blog.chinaaet.com/weiqi7777/p/5100017757 对于编写的systemverilog代码,在linux下,可以使用vcs编译,但是编译的时候,要注意,要加入几个选项。 整个过程,linux使用的是64位的redhat,vcs使用的是vcs2015,verdi使用的是verdi2015。如以下的systemverilog代码。

个人使用verdi技巧(持续更新)

1.找到Verdi的signal list 方便查看信号 方法:打开上面菜单栏的window,然后打开signal_list的开关,然后就可以方便的查看信号。

Makefile脚本启动VCS+Verdi

文章目录 一、快速入门二、Makefile的语法1.语法格式2.命令执行3.变量 三、VCS仿真1.VCS常用命令2.Makefile实现自动化仿真 四、VCS+Verdi的使用1.编译2.仿真3.Verdi 查看fsdb文件的命令4.Makefile启动VCS+Verdi的实例 注:主要侧重于Makefile调用VCS和Verdi联合仿真。 一、快速入门 Mak

Verdi常用参数说明

Verdi是一个用于数字信号处理的仿真和调试工具。在Verdi中,可以使用各种参数来配置仿真和调试行为。以下是一些常用的Verdi参数及其说明: 参数作用-f文件列表-ssf指定fsdb的路径-l设置仿真日志的输出级别,如"none"、“errors”、“info”、“debug”-top指定顶层设计-nologo用于禁用Verdi启动时的Logo显示,加快启动速度。-autoalias自动为未

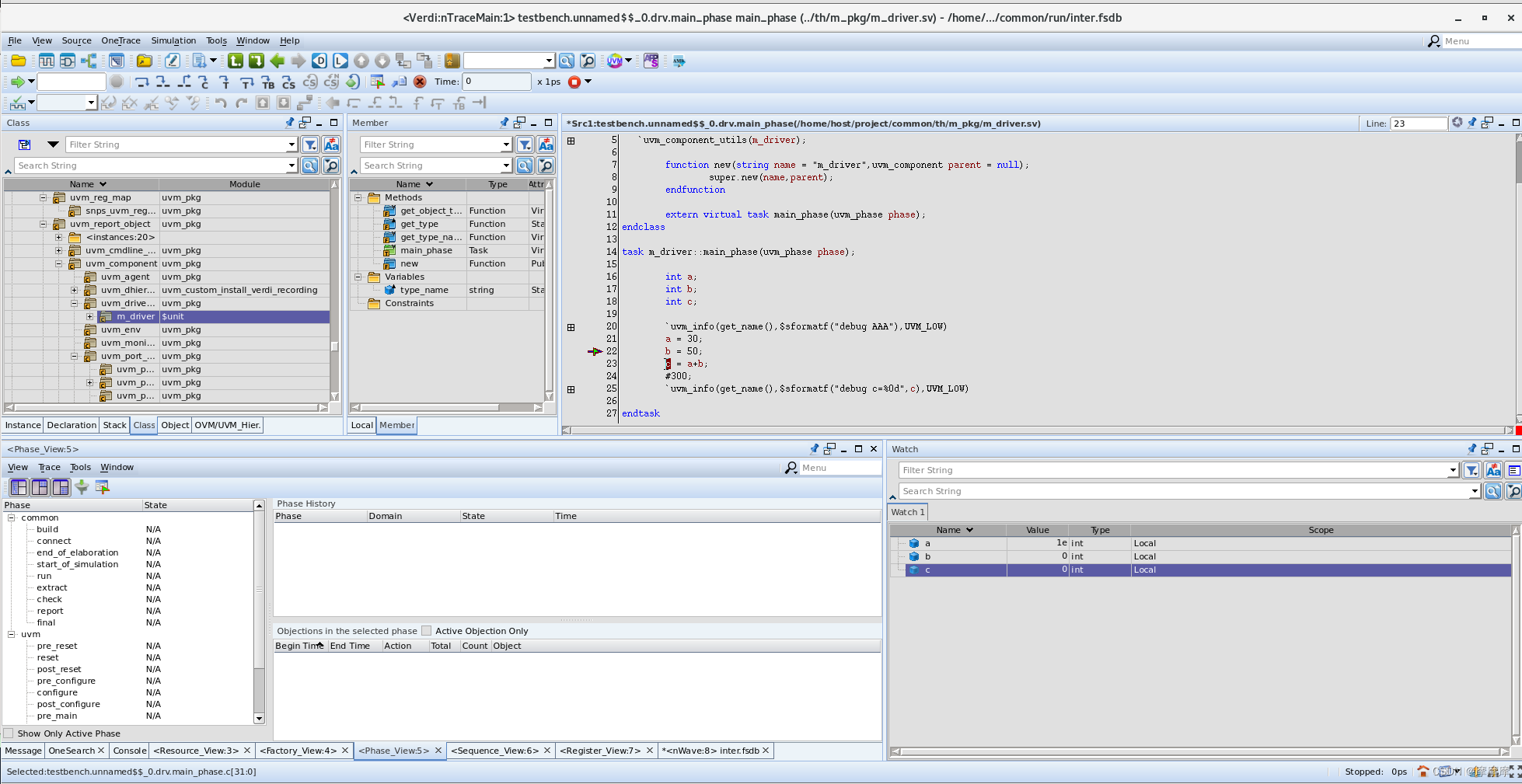

vcs+verdi+uvm单步调试及问题记录

编译 编译选项如下: vcs -ntb_opts uvm -sverilog -f $PROJ_ROOT/tb/option.f -debug_access+all -kdb -lca -full64 -fsdb_old -timescale=1ns/10ps 其中最重要的是要加上这四项 -debug_access+all -kdb -lca -full64 option.f里面的内容如

Verdi使用filelist打开.v工程文件

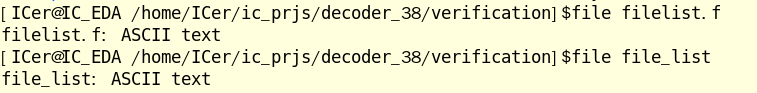

在学习Verdi的过程中发现下载的工程文件中,很多在Makefile中使用了filelist来引用design的所有.v工程文件,但有些Makefile中是使用“-f filelist.f”,而另一些是使用“-f file_list”,其实两者并无差异,使用file指令发现两者的文件格式均为ASCII text。

nc-sim (irun)和verdi ncverilog,

- irun有意思的地方,其帮助命令 irun -helphelp irun -helpall --------------- yxr:简单点说,就是添加动态库的路径名,LD_LIBRARY_PAH,然后调用时添加 -loadpli1 debpli:novas_pli_boot 或者 +loadpli1=debpli:novas_pli_boot 原文:https:

#systemverilog# 之 event region 和 timeslot 仿真调度(三)Verdi 辅助查看

前面的几篇文章,我们对SV仿真调度进行了理论分析和实战演练。那么工具厂商,对该类问题有没有提供相应的支持。这个应该是肯定的。因为我们知道,SV只是出于定义标准的角度,规定了仿真调度事件原理。但是具体实施细节,应是每家EDA仿真工具厂商根据自家的软件开发算法而定的。所以,EDA厂商也是很容易来做这件事的。VCS+Verdi工具,便提供了相应的feature,今天我们来学习和总结一下。 一 even

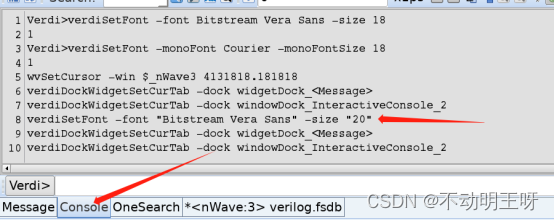

verdi如何打开时可以加载配置比如字体

打开tcl使能 找到配置字体的命令 其实其他有需要的文件配置都可以在这里找到对应的指令 存储文件 新建verdi001.tcl文件 输入想要调整的字体以及大小 verdiSetFont -font "Bitstream Vera Sans" -size "18"verdiSetFont -monoFont "Courier" -monoFontSize "18" 打开

linux环境下vcs+verdi的使用

文章目录 前言一、vcs编译过程二、vcs常用指令1、常用(1)编译文件(2)debug选项(3)目录(4)使用verdi时需要在vcs里面添加的编译选项(5)仿真选项(加在sim里面)(6)其他(7)完整版本 2、覆盖率相关3、波形相关4、仿真命令和仿真环境之间传递参数4.1 宏定义4.2 条件编译函数 \$test$plusargs4.3 参数传递函数 \$value$plusargs

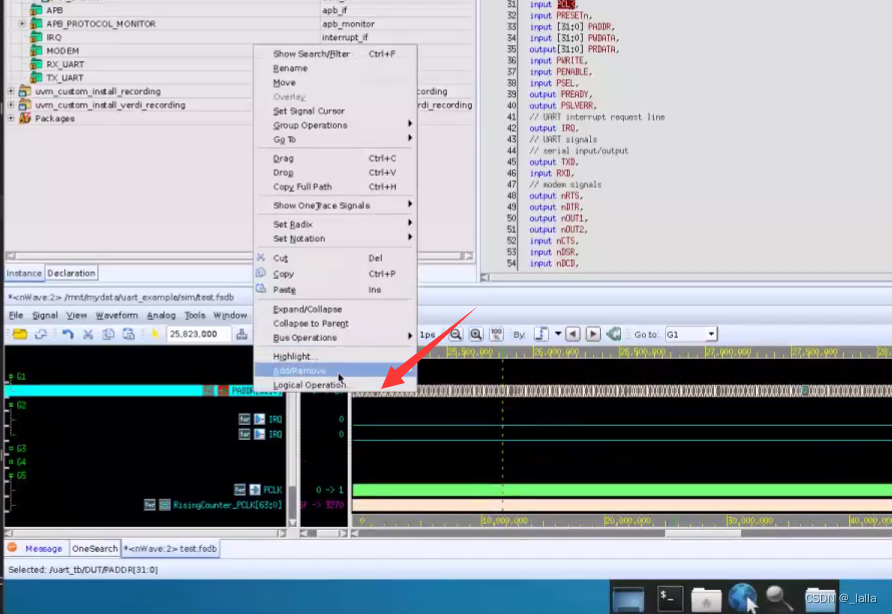

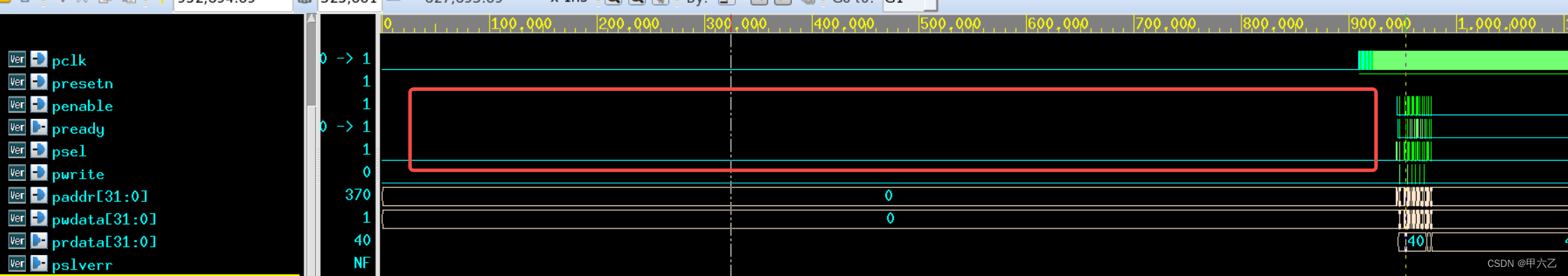

verdi -ssf verilog.vf打开多个波形,有的信号显示不完整

在使用verdi -ssf verilog.vf打开波形的时候,有的信号的波形会显示不完整,如下图所示 前面的一段信号是空的,显示不出来。 但是如果用verdi -ssf verilog.fsdb,直接打开波形就不会遇到这个问题 我的EDA平台如下: 1. linux os 2. vcs version: vcs S-2021.09 3. verdi version: verd

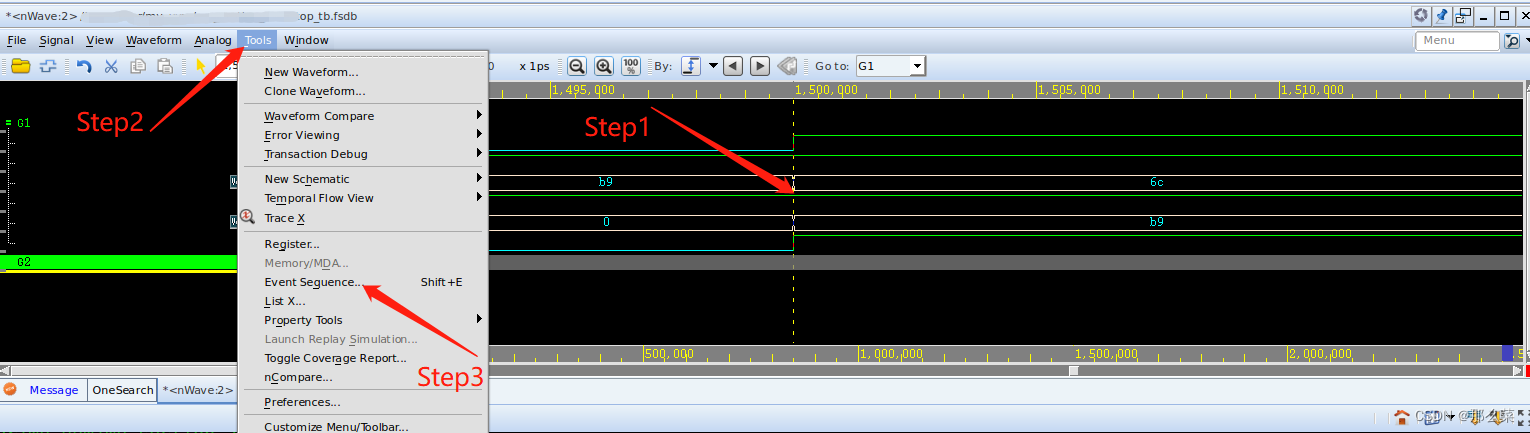

在verdi波形中显示状态机名字

背景 在RTL中,状态机编码一般是用parameter常量,变量名是大写,变量的值一般是onehot或者格雷码,为了波形中清楚地识别每个状态,最好在波形中显示状态机名字。 方法一 在verdi的顶层菜单窗口,选择tools-->Extract Interactive FSM,如下图 选择First State或者All Stages皆可,区别是First State仅展开目前的所指定的F

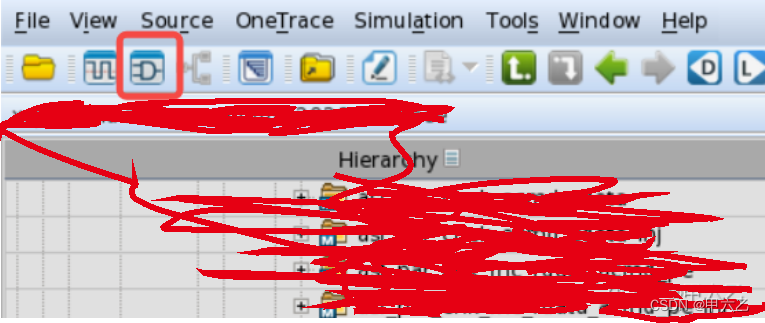

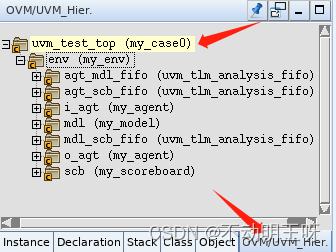

verdi显示OVM/UVM Hierarchy View

verdi显示OVM/UVM Hierarchy View 背景 使用vcs+verdi+UVM进行UVM debug的时候,verdi加载的时候看不到UVM树形结构图 解决办法 simv +UVM_VERDI_TRACE=“UVM_AWARE+HIER” -gui=verdi 2023-10-9 打开界面后,并不会直接显示树形层级 需要先仿真一定时间(自己定),然后就可以常看树形结构了 最后

![verdi windows版本[使用debussy 5.4]](/front/images/it_default2.jpg)