本文主要是介绍嵌入式异质结体二极管的3.3 kV 4H-SiC MOSFET用于低开关损耗,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

题目:3.3 kV 4H-SiC MOSFET with embeded hetero junction body diode for low switching loss

阅读日期:2023.6.23

受到的启发:

The Ron-sp of the SH-HJD MOSFET is 9.60 mΩ∙cm2, which is about 21.6% lower than the 12.25 mΩ∙cm2 of the C-MOFSET. This is due to the difference in the expansion of the depletion width in the JFET region.In Fig. 5, since the P+ base region of the SH-HJD MOSFET is smaller than that of the C-MOSFET, the extended depletion width WP in the JFET region is smaller. Therefore, the path of the current flowing to the N-drift becomes wider, and Ron-sp decreases as the JFET resistance decreases.

The Baliga’s FOM (BFOM) can be calculated by the following equation:

B F O M = B V 2 R o n − s p B F O M=\frac{B V^2}{R_{o n-s p}} BFOM=Ron−spBV2

研究了什么

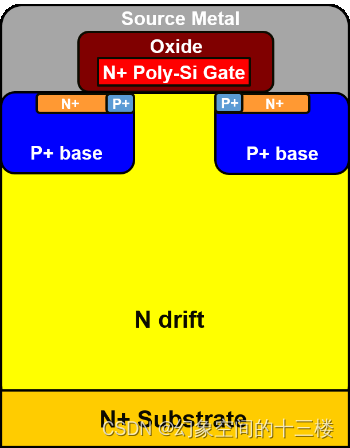

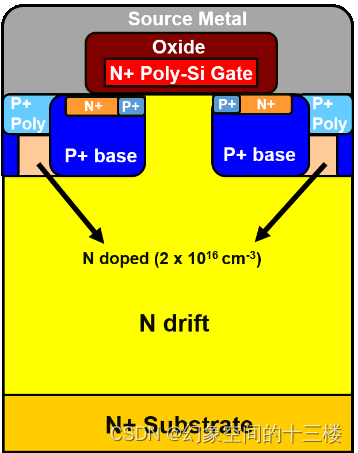

该论文提出了一种3.3 kV级别的屏蔽异质结4H-SiC MOSFET器件,具有改进的开关损耗和反向恢复特性。该器件采用P+多晶硅嵌入在分离的4H-SiC P+基底之间的结构。论文通过TCAD模拟研究了所提出的器件的性能,并与传统MOSFET(C-MOSFET)进行了比较。

文章创新点

该论文的创新点包括:

提出了一种具有改进的开关损耗和反向恢复特性的3.3 kV级别的屏蔽异质结4H-SiC MOSFET器件。

引入了P+多晶硅嵌入在分离的4H-SiC P+基底之间的结构,以保护P+多晶硅免受高漏电压的影响,并使其在高电压下稳定运行。

利用P+多晶硅和N漂移层之间的异质结作为单极二极管,以改善反向恢复特性。

进行TCAD模拟,评估所提出的器件的性能,并将其与传统MOSFET(C-MOSFET)进行比较。

证明所提出的器件将BFOM提高了19.12%,将反向恢复电荷降低了93.7%,并将开关损耗降低了61.86%,相比于C-MOSFET。

研究方法

该论文的研究方法是TCAD模拟。通过TCAD模拟评估所提出的器件的性能,并将其与传统MOSFET(C-MOSFET)进行比较。模拟结果表明,所提出的器件在BFOM、反向恢复电荷和开关损耗方面比C-MOSFET表现更好。

得出的结论

该论文得出的结论包括:

所提出的具有改进的开关损耗和反向恢复特性的3.3 kV级别的屏蔽异质结4H-SiC MOSFET器件比传统MOSFET(C-MOSFET)表现更好。

所提出的器件采用P+多晶硅嵌入在分离的4H-SiC P+基底之间的结构,以保护P+多晶硅免受高漏电压的影响,并使其在高电压下稳定运行。

P+多晶硅和N漂移层之间的异质结作为单极二极管,改善了反向恢复特性。

所提出的器件将BFOM提高了19.12%,将反向恢复电荷降低了93.7%,并将开关损耗降低了61.86%,相比于C-MOSFET。

所提出的器件可通过体二极管配置应用于高电压功率系统中。

这篇关于嵌入式异质结体二极管的3.3 kV 4H-SiC MOSFET用于低开关损耗的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!