本文主要是介绍SS928官方vo例子适配mipi屏,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

这里写目录标题

- 背景

- 硬件原理

- 测试代码

- LCD复位和背光使能信号控制(即GPIO输出控制)

- mipi屏幕初始化序列

- mipi 配置参数

- 计算时序参数

- 计算时钟

- 输入图像设置

- 参考文件

背景

最近新购一款SS928的开发板,但其外部只提供了HDMI显示接口,官方未适配MIPI屏,考虑到调试的时候每次找HDMI显示器不方便,就自己画了个板子匹配了一款mipi的显示屏,屏幕为:8.0 inch IPS MIPI 800x1280 AML08021016-31D Amelin Electronic Technology。

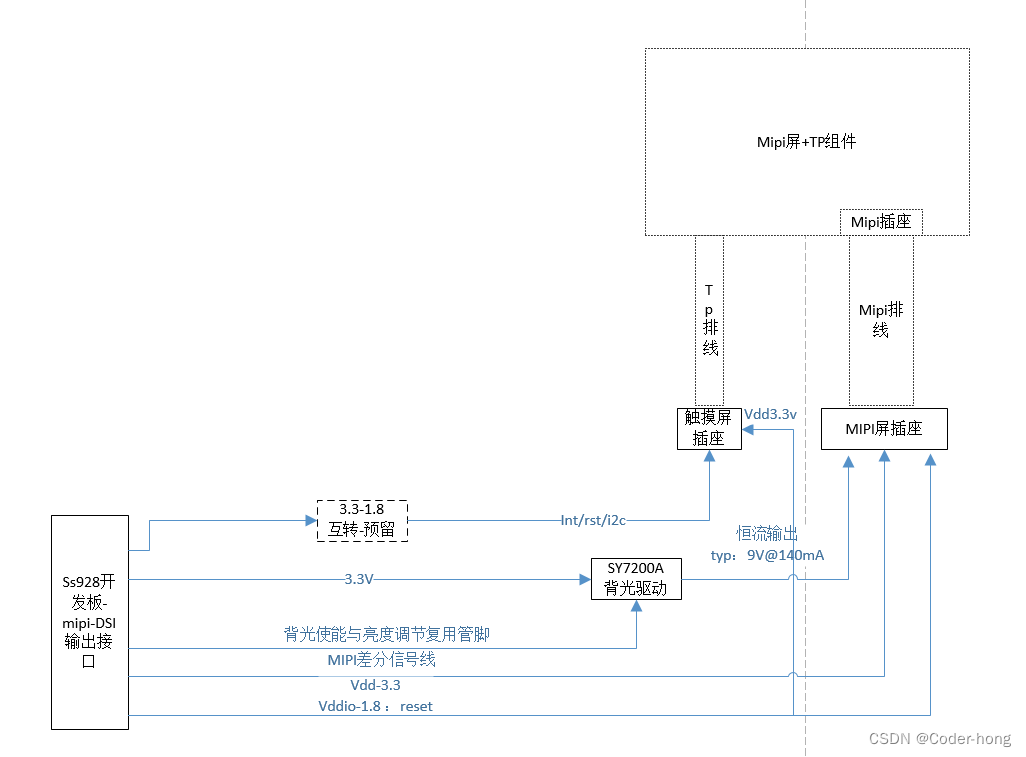

硬件原理

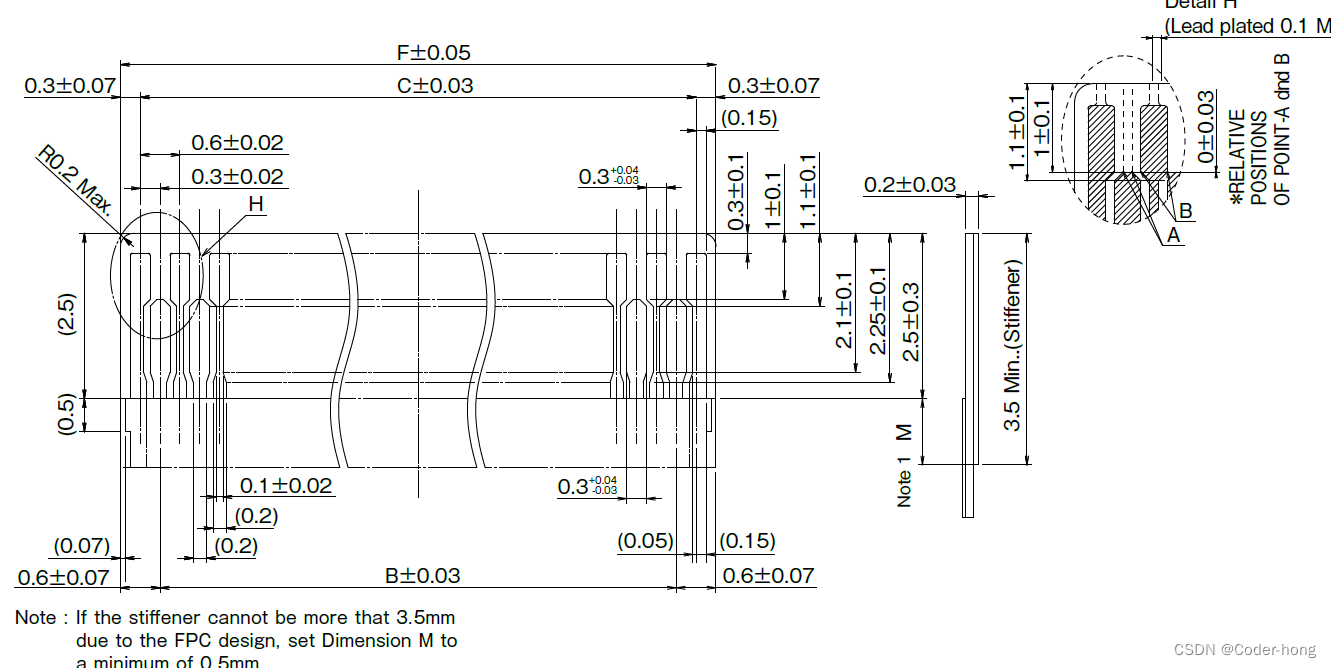

自己设计打板测试,主要在mipi屏幕插座上出了点问题,该连接器为0.3mm间距的FPC排线,大体结构示意如下:

为双排触点,设计时一定要注意,再一点就是该连接器封装焊盘往连接器外侧稍微做长些,要不然没法手工焊,当然如果自己做钢网焊接是无所谓的。

测试代码

基于海思官方sdk中的vo例程修改,所在路径:~/ss928v100_sdk/SS928V100_SDK_V2.0.2.1/smp/a55_linux/mpp/sample/vo/sample_vo.c,完整代码:ss928驱动mipi 800x1280显示屏测试代码

原例子只有1个参数0,将输入vi视频通过1200*1920的显示屏输出,再不修改原例子的情况下主要增加了参数1 :

static hi_s32 sample_vo_mipi_tx_800x1280_user(hi_void)

{return sample_vo_mipi_tx(&g_vo_tx_cfg_800x1280_user);

}

static hi_s32 sample_vo_execute_case(hi_s32 index)

{if (index == 0) {return sample_vo_mipi_tx_1200x1920_user();}if (index == 1) {return sample_vo_mipi_tx_800x1280_user();}sample_print("the index %d is invalid!\n", index);return HI_FAILURE;

}

LCD复位和背光使能信号控制(即GPIO输出控制)

首先需要用vi命令修改开发板/app目录下的pinmux文件,配置管脚复用,该复用配置脚本上电会自动运行,还有另一种可以通过修改uboot配置参数实现:

/app # vi pinmux.sh

主要增加以下复用信息,该配置寄存器地址可以在“21AP10_PINOUT_CN.xlsx”文件中查到。

#mipi_lcd

bspmm 0x0102F00F8 0x1201 #LCD_RST GPIO9_7

bspmm 0x0102F01EC 0X120 #BACKLIGHT GPIO17_0

大概的控制方法如下:

//export gpiofp = fopen("/sys/class/gpio/export", "w");fprintf (fp, "%d", 79);//lcd_reset io79==gpio9_7==9x8+7fclose(fp);//set gpio directionfp = fopen("/sys/class/gpio/gpio79/direction", "rb+");fprintf(fp, "out");fclose(fp);//RST == HIGHTfp = fopen("/sys/class/gpio/gpio79/value", "rb+");strcpy(buf,"1");fwrite(buf, sizeof(char), sizeof(buf)-1, fp);fclose(fp);//RST == lowfp = fopen("/sys/class/gpio/gpio79/value", "rb+");strcpy(buf,"0");fwrite(buf, sizeof(char), sizeof(buf)-1, fp);fclose(fp);

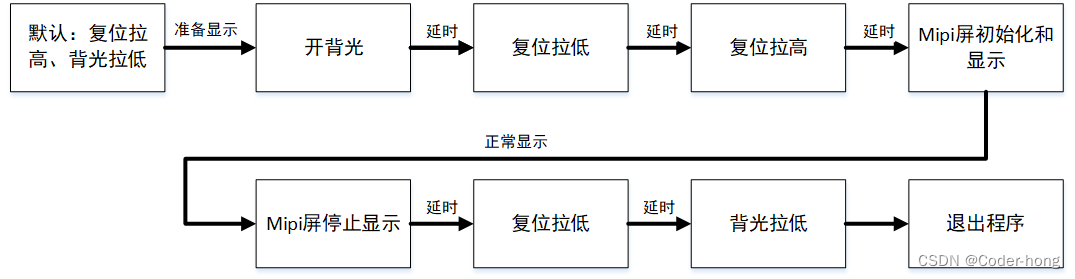

控制流程为,默认延时我设置的200ms:

mipi屏幕初始化序列

一般由厂家提供,主要通过mipi命令模式向屏幕写入寄存器配置信息,我这个屏幕参数组成为{地址,长度,数据1,… 数据n},厂家提供的初始化序列为:

//800x1280

//VS_VBP_VFP=2/16/16

//HS_HBP_HFP=4/138/24REGISTER,FF,03,98,81,03//GIP_1REGISTER,01,01,00

REGISTER,02,01,00

REGISTER,03,01,5D //STVA

REGISTER,04,01,17 //STVB

REGISTER,05,01,00 //STVC

REGISTER,06,01,0E //STVA_Rise

REGISTER,07,01,00 //STVB_Rise

REGISTER,08,01,00 //STVC_Rise

REGISTER,09,01,21 //FTI1R(A) 21

REGISTER,0a,01,21 //FTI2R(B)

REGISTER,0b,01,00 //FTI3R(C)

REGISTER,0c,01,06 //FTI1F(A) 06

REGISTER,0d,01,06 //FTI2F(B)

REGISTER,0e,01,00 //FTI2F(C)

REGISTER,0f,01,22 //CLW1(ALR) 玡玠

REGISTER,10,01,22 //CLW2(ARR) 玡玠

REGISTER,11,01,00

REGISTER,12,01,00

REGISTER,13,01,05 //CLWX(ATF) 玠

REGISTER,14,01,00

REGISTER,15,01,00 //GPMRi(ALR)

REGISTER,16,01,00 //GPMRii(ARR)

REGISTER,17,01,00 //GPMFi(ALF)

REGISTER,18,01,00 //GPMFii(AFF)

REGISTER,19,01,00

REGISTER,1a,01,00

REGISTER,1b,01,00

REGISTER,1c,01,00

REGISTER,1d,01,00

REGISTER,1e,01,40 //CLKA 40笆は C0も笆は(X8把σCLKB)

REGISTER,1f,01,C0 //C0

REGISTER,20,01,0E //CLKA_Rise

REGISTER,21,01,09 //CLKA_Fall

REGISTER,22,01,0F //CLKB_Rise(keep toggle惠砞CLK A)

REGISTER,23,01,00 //CLKB_Fall

REGISTER,24,01,8A //CLK keep toggle(AL) 8X┕オ

REGISTER,25,01,8A //CLK keep toggle(AR) 8X┕オ

REGISTER,26,01,00

REGISTER,27,01,00

REGISTER,28,01,77 //CLK Phase KEEP Toggle 7F

REGISTER,29,01,77 //CLK overlap

REGISTER,2a,01,00

REGISTER,2b,01,00

REGISTER,2c,01,02 //GCH R

REGISTER,2d,01,02 //GCL R

REGISTER,2e,01,07 //GCH F

REGISTER,2f,01,07 //GCL F

REGISTER,30,01,00

REGISTER,31,01,00

REGISTER,32,01,22 //GCH/L ext2/1︽ 5E 01:31 5E 00:42

REGISTER,33,01,00

REGISTER,34,01,00 //VDD1&2 non-overlap 04:2.62us

REGISTER,35,01,0A //GCH/L 跋丁 00:VS玡 01:VS 10:阁VS 11:frameい

REGISTER,36,01,00

REGISTER,37,01,08 //GCH/L

REGISTER,38,01,3C //VDD1&2 toggle 1sec

REGISTER,39,01,00

REGISTER,3a,01,00

REGISTER,3b,01,00

REGISTER,3c,01,00

REGISTER,3d,01,00

REGISTER,3e,01,00

REGISTER,3f,01,00

REGISTER,40,01,00

REGISTER,41,01,00

REGISTER,42,01,00

REGISTER,43,01,08 //GCH/L

REGISTER,44,01,00 //GIP_2

REGISTER,50,01,01

REGISTER,51,01,23

REGISTER,52,01,45

REGISTER,53,01,67

REGISTER,54,01,89

REGISTER,55,01,AB

REGISTER,56,01,01

REGISTER,57,01,23

REGISTER,58,01,45

REGISTER,59,01,67

REGISTER,5a,01,89

REGISTER,5b,01,AB

REGISTER,5c,01,CD

REGISTER,5d,01,EF //GIP_3

REGISTER,5e,01,00

REGISTER,5f,01,02 //FW_CGOUT_L[1] VGL

REGISTER,60,01,02 //FW_CGOUT_L[2] VGL

REGISTER,61,01,06 //FW_CGOUT_L[3] VST_R

REGISTER,62,01,0F //FW_CGOUT_L[4] XCLK_R4

REGISTER,63,01,0F //FW_CGOUT_L[5] XCLK_R4

REGISTER,64,01,13 //FW_CGOUT_L[6] CLK_R4

REGISTER,65,01,13 //FW_CGOUT_L[7] CLK_R4

REGISTER,66,01,0E //FW_CGOUT_L[8] XCLK_R3

REGISTER,67,01,0E //FW_CGOUT_L[9] XCLK_R3

REGISTER,68,01,12 //FW_CGOUT_L[10] CLK_R3

REGISTER,69,01,12 //FW_CGOUT_L[11] CLK_R3

REGISTER,6a,01,0D //FW_CGOUT_L[12] XCLK_R2

REGISTER,6b,01,0D //FW_CGOUT_L[13] XCLK_R2

REGISTER,6c,01,11 //FW_CGOUT_L[14] CLK_R2

REGISTER,6d,01,11 //FW_CGOUT_L[15] CLK_R2

REGISTER,6e,01,0C //FW_CGOUT_L[16] XCLK_R1

REGISTER,6f,01,0C //FW_CGOUT_L[17] XCLK_R1

REGISTER,70,01,10 //FW_CGOUT_L[18] CLK_R1

REGISTER,71,01,10 //FW_CGOUT_L[19] CLK_R1

REGISTER,72,01,00 //FW_CGOUT_L[20] D2U 00

REGISTER,73,01,16 //FW_CGOUT_L[21] U2D 01

REGISTER,74,01,08 //FW_CGOUT_L[22] VENDREGISTER,75,01,02 //BW_CGOUT_L[1]

REGISTER,76,01,02 //BW_CGOUT_L[2]

REGISTER,77,01,08 //BW_CGOUT_L[3]

REGISTER,78,01,0F //BW_CGOUT_L[4]

REGISTER,79,01,0F //BW_CGOUT_L[5]

REGISTER,7a,01,13 //BW_CGOUT_L[6]

REGISTER,7b,01,13 //BW_CGOUT_L[7]

REGISTER,7c,01,0E //BW_CGOUT_L[8]

REGISTER,7d,01,0E //BW_CGOUT_L[9]

REGISTER,7e,01,12 //BW_CGOUT_L[10]

REGISTER,7f,01,12 //BW_CGOUT_L[11]

REGISTER,80,01,0D //BW_CGOUT_L[12]

REGISTER,81,01,0D //BW_CGOUT_L[13]

REGISTER,82,01,11 //BW_CGOUT_L[14]

REGISTER,83,01,11 //BW_CGOUT_L[15]

REGISTER,84,01,0C //BW_CGOUT_L[16]

REGISTER,85,01,0C //BW_CGOUT_L[17]

REGISTER,86,01,10 //BW_CGOUT_L[18]

REGISTER,87,01,10 //BW_CGOUT_L[19]

REGISTER,88,01,17 //BW_CGOUT_L[20]

REGISTER,89,01,01 //BW_CGOUT_L[21]

REGISTER,8A,01,06 //BW_CGOUT_L[22] //CMD_Page 4

REGISTER,FF,03,98,81,04REGISTER,6E,01,2A //2B /VGH 15V

REGISTER,6F,01,37 // reg vcl + pumping ratio VGH=3x VGL=-3x

REGISTER,3A,01,A4 //POWER SAVING

REGISTER,8D,01,25 //VGL -13V

REGISTER,87,01,BA //ESD

REGISTER,B2,01,D1

REGISTER,88,01,0B

REGISTER,38,01,01

REGISTER,39,01,00

REGISTER,B5,01,07 //gamma bias

REGISTER,31,01,75 //source bias

REGISTER,3B,01,98 //CMD_Page 1

REGISTER,FF,03,98,81,01

REGISTER,22,01,0A //BGR, SS

REGISTER,31,01,0A //Z inversion

REGISTER,35,01,07 //chopper

REGISTER,52,01,00 //VCOM1[8]

REGISTER,53,01,73 //VCOM1[7:0]

REGISTER,54,01,00 //VCOM2[8]

REGISTER,55,01,3D //VCOM2[7:0]

REGISTER,50,01,D0 //VREG1OUT 5.208V

REGISTER,51,01,CB //VREG2OUT -5.208V

REGISTER,60,01,14 //SDT=2.0

REGISTER,62,01,01 //EQ

REGISTER,63,01,01 //PC//============Gamma START=============//Pos Register

REGISTER,A0,01,00

REGISTER,A1,01,18

REGISTER,A2,01,28

REGISTER,A3,01,17

REGISTER,A4,01,1C

REGISTER,A5,01,30

REGISTER,A6,01,24

REGISTER,A7,01,24

REGISTER,A8,01,85

REGISTER,A9,01,1C

REGISTER,AA,01,26

REGISTER,AB,01,66

REGISTER,AC,01,19

REGISTER,AD,01,18

REGISTER,AE,01,4F

REGISTER,AF,01,24

REGISTER,B0,01,2B

REGISTER,B1,01,4A

REGISTER,B2,01,59

REGISTER,B3,01,23//Neg Register

REGISTER,C0,01,00

REGISTER,C1,01,18

REGISTER,C2,01,28

REGISTER,C3,01,17

REGISTER,C4,01,1B

REGISTER,C5,01,2F

REGISTER,C6,01,22

REGISTER,C7,01,22

REGISTER,C8,01,87

REGISTER,C9,01,1C

REGISTER,CA,01,27

REGISTER,CB,01,66

REGISTER,CC,01,19

REGISTER,CD,01,1A

REGISTER,CE,01,4E

REGISTER,CF,01,24

REGISTER,D0,01,2A

REGISTER,D1,01,4C

REGISTER,D2,01,5A

REGISTER,D3,01,23//============ Gamma END=========== //CMD_Page 0

REGISTER,FF,03,98,81,00

REGISTER,11,01,00

Delay,120

REGISTER,29,01,00

REGISTER,35,01,00代码如下,主要注意多字节命令与单字节命令不同,保险期间每次换页增加延时。

const unsigned char ATTRIBUTE cmd_page0[4] = {0xFF,0x98,0x81,0x00};

const unsigned char ATTRIBUTE cmd_page1[4] = {0xFF,0x98,0x81,0x01};

const unsigned char ATTRIBUTE cmd_page2[4] = {0xFF,0x98,0x81,0x02};

const unsigned char ATTRIBUTE cmd_page3[4] = {0xFF,0x98,0x81,0x03};

const unsigned char ATTRIBUTE cmd_page4[4] = {0xFF,0x98,0x81,0x04};

static mipi_tx_cmd_info g_cmd_info_800x1280[CMD_COUNT_800x1280] = {/* {devno work_mode lp_clk_en data_type cmd_size cmd}, usleep_value */

{{0, 0, 0, 0x39, 0x0004, cmd_page3}, USLEEP_6000},

{{0, 0, 0, 0x23, 0x0001, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0002, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x5D03, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x1704, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0005, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0E06, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0007, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0008, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x2109, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x210a, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x000b, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x060c, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x060d, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x000e, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x220f, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x2210, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0011, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0012, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0513, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0014, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0015, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0016, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0017, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0018, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0019, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x001a, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x001b, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x001c, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x001d, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x401e, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0xC01f, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0E20, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0921, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0F22, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0023, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x8A24, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x8A25, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0026, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0027, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x7728, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x7729, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x002a, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x002b, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x022c, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x022d, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x072e, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x072f, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0030, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0031, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x2232, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0033, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0034, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0A35, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0036, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0837, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x3C38, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0039, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x003a, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x003b, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x003c, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x003d, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x003e, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x003f, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0040, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0041, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0042, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0843, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0044, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0150, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x2351, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x4552, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x6753, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x8954, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0xAB55, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0156, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x2357, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x4558, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x6759, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x895a, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0xAB5b, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0xCD5c, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0xEF5d, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x005e, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x025f, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0260, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0661, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0F62, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0F63, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x1364, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x1365, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0E66, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0E67, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x1268, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x1269, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0D6a, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0D6b, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x116c, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x116d, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0C6e, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0C6f, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x1070, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x1071, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0072, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x1673, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0874, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0275, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0276, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0877, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0F78, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0F79, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x137a, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x137b, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0E7c, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0E7d, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x127e, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x127f, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0D80, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0D81, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x1182, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x1183, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0C84, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0C85, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x1086, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x1087, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x1788, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0189, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x068A, NULL}, USLEEP_50},

{{0, 0, 0, 0x39, 0x0004, cmd_page4}, USLEEP_6000},

{{0, 0, 0, 0x23, 0x2A6E, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x376F, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0xA43A, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x258D, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0xBA87, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0xD1B2, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0B88, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0138, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0039, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x07B5, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x7531, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x983B, NULL}, USLEEP_50},

{{0, 0, 0, 0x39, 0x0004, cmd_page1}, USLEEP_6000},

{{0, 0, 0, 0x23, 0x0A22, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0A31, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0735, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0052, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x7353, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0054, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x3D55, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0xD050, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0xCB51, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x1460, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0162, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0163, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x00A0, NULL}, USLEEP_50},//Gamma

{{0, 0, 0, 0x23, 0x18A1, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x28A2, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x17A3, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x1CA4, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x30A5, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x24A6, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x24A7, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x85A8, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x1CA9, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x26AA, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x66AB, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x19AC, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x18AD, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x4FAE, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x24AF, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x2BB0, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x4AB1, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x59B2, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x23B3, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x00C0, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x18C1, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x28C2, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x17C3, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x1BC4, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x2FC5, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x22C6, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x22C7, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x87C8, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x1CC9, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x27CA, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x66CB, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x19CC, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x1ACD, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x4ECE, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x24CF, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x2AD0, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x4CD1, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x5AD2, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x23D3, NULL}, USLEEP_50},

{{0, 0, 0, 0x39, 0x0004, cmd_page0}, USLEEP_6000},

{{0, 0, 0, 0x23, 0x0011, NULL}, USLEEP_120000},

{{0, 0, 0, 0x23, 0x0029, NULL}, USLEEP_50},

{{0, 0, 0, 0x23, 0x0035, NULL}, USLEEP_50},

};

mipi 配置参数

/* VO: USER 800x1280_60, TX: USER 800x1280 */

static const sample_vo_mipi_tx_cfg g_vo_tx_cfg_800x1280_user = {.vo_config = {.vo_dev = SAMPLE_VO_DEV_UHD,.vo_intf_type = HI_VO_INTF_MIPI,.intf_sync = HI_VO_OUT_USER,.bg_color = COLOR_RGB_BLACK,.pix_format = HI_PIXEL_FORMAT_YVU_SEMIPLANAR_420,.disp_rect = {0, 0, 800, 1280},//从image中扣取[800x1280]进行显示,x/y测试无效.image_size = {800, 1280},//将vi输入图像缩放到[800x1280]大小.vo_part_mode = HI_VO_PARTITION_MODE_SINGLE,.dis_buf_len = 3, /* 3: def buf len for single */.dst_dynamic_range = HI_DYNAMIC_RANGE_SDR8,.vo_mode = VO_MODE_1MUX,.compress_mode = HI_COMPRESS_MODE_NONE,.sync_info = {.syncm = 0,.iop = 1,.intfb = 1,.vact = 1280,//.vbb = 18,//.vfb = 16,//.hact = 800,//.hbb = 142,//.hfb = 24,//.hmid = 1,.bvact = 1,.bvbb = 1,.bvfb = 1,.hpw = 4,//.vpw = 2,//.idv = 0,.ihs = 0,.ivs = 0},.user_sync = {.user_sync_attr = {.clk_src = HI_VO_CLK_SRC_PLL,//从PLL FOUTPOSTDIV pin脚引出时钟,范围:[16.326531, 594]MHz.vo_pll = { /* if hdmi, set it by pixel clk and div mode */ // .fb_div = 80, /* 80 fb div */ // 当frac == 0时:pll_oclk = 24MHz * fb_div / ref_div = 1920MHz (应在800~3200MHz之间).frac = 0, //0.ref_div = 1, /* 1 ref div */.post_div1 = 6, /* 6 post div1 */.post_div2 = 4, /* 4 post div2 */ // fpost = pll_oclk /post_div1 / post_div2 = 80MHz},},.pre_div = 1, /* if hdmi, set it by pixel clk */.dev_div = 1, /* if rgb, set it by serial mode */.clk_reverse_en = HI_TRUE,},.dev_frame_rate = SAMPLE_VO_DEV_FRAME_RATE,},.tx_config = {/* for combo dev config */.intf_sync = HI_MIPI_TX_OUT_USER,/* for screen cmd */.cmd_count = CMD_COUNT_800x1280,.cmd_info = g_cmd_info_800x1280,/* for user sync */.combo_dev_cfg = {.devno = 0,.lane_id = {0, 1, 2, 3},.out_mode = OUT_MODE_DSI_VIDEO,.out_format = OUT_FORMAT_RGB_24BIT,.video_mode = BURST_MODE,.sync_info = {.hsa_pixels = 4, /* 4 pixel */.hbp_pixels = 138, /* 138 pixel */.hact_pixels = 800, /* 800 pixel */.hfp_pixels = 24, /* 24 pixel */.vsa_lines = 2, /* 2 line */.vbp_lines = 16, /* 16 line */.vact_lines = 1280, /* 1280 line */.vfp_lines = 16, /* 16 line */},.phy_data_rate = 999, /* 999 Mbps */ //800MHz试了也可以正常显示.pixel_clk = 80000, /* 160000 KHz */ //"RGB_MIPI屏幕时钟时序计算器"计算时钟频率有小数位,我直接向上取整,否则按表格中的pll配置参数无法写入,报参数超差的错误},},

};

计算时序参数

采用官方提供的 《RGB_MIPI屏幕时钟时序计算器.xlsx》获得,按厂家建议配置如下,填入以上代码。

计算时钟

这里配置花费了很多时间,按表格计算的时钟频率和锁相环参数填入总会报参数错误,总结大体的计算思路如下:

- 按表格计算出像素时钟为76160,向上取整,我取的80MHz(实际我也测试了其他频率如100MHz、160MHz也可以显示,只是160MHz时屏幕有噪点)

- 设置:frac == 0,去除小数位以方便计算,按下面2个公式计算pll频率和输出频率:

pll_oclk = 24MHz * fb_div / ref_div = 1920MHz (应在800~3200MHz之间)

fpost = pll_oclk /post_div1 / post_div2 = 80MHz (注意:post_div1应大于post_div2)

输入图像设置

官方文档说明可以输出colorbar进行mipi输出接口独立测试,这个我就没有尝试了,直接参考例子把输入vi视频缩放后输出,主要注意以下2个参数:

vo_config={.disp_rect = {0, 0, 800, 1280},//从image中扣取[800x1280]进行显示,x/y测试无效.image_size = {800, 1280}//将vi输入图像缩放到[800x1280]大小}

第二个参数表示将输入[3840*2160]图像缩放到多大的尺寸,我试了可小可大,5000x5000都时可以的。

第一个参数感觉是从缩放后的图像中扣取显示区域,但我测试了xy参数不起作用,宽高只能是显示屏分辨率[800, 1280],若设置为500x500将在显示屏下部和右侧出现黑边。

参考文件

官方文件:

RGB_MIPI屏幕时钟时序计算器.xlsx

21AP10_PINOUT_CN.xlsx

01 EB-SS928-DC-393型开发板底板原理图.pdf

01 EB-SS928-DC-393型开发板用户快速入门.pdf

02 EB-SS928-DC-393型开发板数据手册V1.2.pdf

屏幕对接 使用指南.pdf

MIPI 使用指南.pdf

MPP 媒体处理软件 V5.0 开发参考.pdf

MPP 媒体处理软件 V5.0 FAQ.pdf

这篇关于SS928官方vo例子适配mipi屏的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!