mipi专题

显示篇(1)兼容屏mipi(1)

固件支持多款屏,但烧录完毕后仅支持一个屏幕 即该固件虽有兼容屏功能,但是烧录后,判断屏幕A.B.C。如果第一次识别当前屏A,会记录下来A屏相关配置。后面开机只匹配A。 该种做法目的为了加快开机速度,不会每次开机都会识别匹配。 适用场景:同一固件兼容多款产品,后期不会再次换屏。 uboot补丁 diff --git a/drivers/video/sunxi/disp2/disp/de/d

MIPI联盟D-PHYv1.2规范阅读笔记二之物理层接口协议PPI

本文阅读自eetop.cn_mipi_D-PHY_specification_v1-2.pdf Logical PHY-Protocol Interface Description(PHY物理层协议接口描述PPI) PHY物理层协议接口被用于连接物理层和通信栈与更高层协议栈之间建立联系。 表 31 定义了物理层协议接口(PPI)中使用的信号。对于具有多个数据通道的物理层(PHY),每个通道使

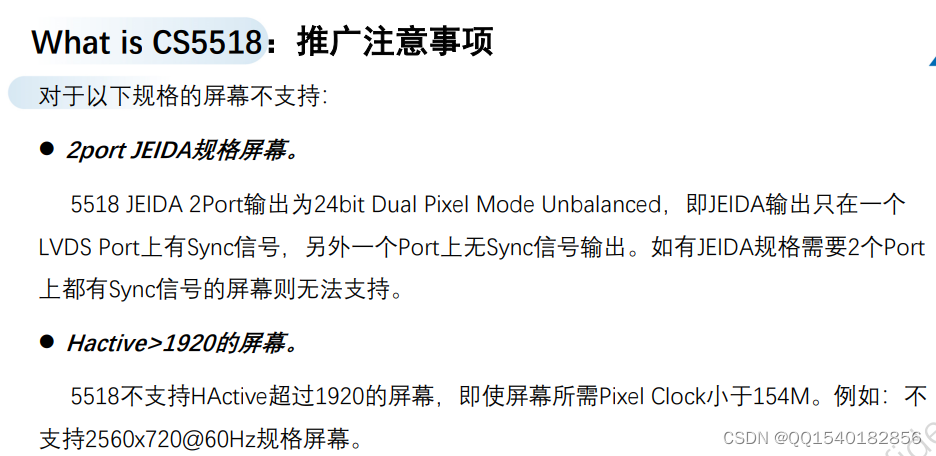

CS5518芯片设计|替代GM8775设计方案|MIPI转LVDS芯片方案|DSI转LVDS芯片方案

CS5518支持常见的1920*1080分辨率的屏,支持视频格式为 FULL HD(1920 x 1200)。为MIPI DSI 转LVDS 双通道桥接芯片,实现将MIPI DSI信号转换为单/双通道 LVDS输出功能,MIPI 支持1/2/3/4 通道可选,支持 4Gbps 速率。LVDS 时钟频率154MHz,该芯片主要应用于手持设备、双屏显示,大屏幕显示等应用需求。 CS5518和其他品牌

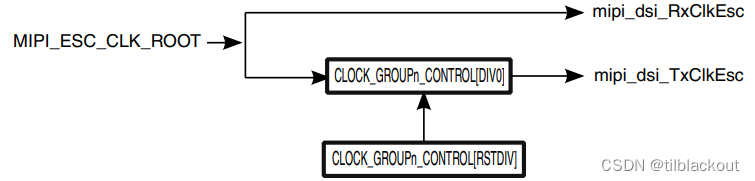

I.MX RT1170之MIPI DSI初始化和显示流程详解

MIPI DSI(Mobile Industry Processor Interface Display Serial Interface)是一种广泛应用于移动设备显示屏的接口标准。由MIPI联盟制定,DSI接口旨在提供高效、低功耗的显示屏数据传输解决方案。 本节来就通过学习I.MX RT1170单片机中的MIPI DSI接口例程,来学习MIPI DSI的初始化流程和相关的参数。 文章目

FPGA高端项目:FPGA解码MIPI视频+图像缩放+视频拼接,基于MIPI CSI-2 RX Subsystem架构实现,提供4套工程源码和技术支持

目录 1、前言工程概述免责声明 2、相关方案推荐我这里已有的 MIPI 编解码方案本方案在Xilinx Artix7-35T上解码MIPI视频的应用本方案在Xilinx Artix7-100T上解码MIPI视频的应用本方案在Xilinx Kintex7上解码MIPI视频的应用本方案在Xilinx Zynq7000上解码MIPI视频的应用本方案在Xilinx Zynq UltraScale上解

Android MIPI屏配置

参考资料:RockChip发布的DRM Display Driver Development Guide手册,以及网上大量相关博客资料 首先要拿到《屏幕硬件规格书》和《DataSheet》,软件配置主要依靠DataSheet提供数据支持。 查阅DataSheet里面on sequence和off sequence说明,这是屏幕上电和下电的时序,将这些数据转换成RK dts文件对应的格式,转换方

Zynq开发-使用PYNQ快速入门摄像头MIPI驱动(OV5640)-overlay设计

目录 1. 简介 2. Overlay 设计 2.1 总体设计 2.2 MIPI 子系统 2.3 去马赛克 2.4 AXI_IIC 3. 注意事项 4. 总结 1. 简介 本文是关于《Zynq开发-使用PYNQ快速入门摄像头MIPI驱动(OV5640)-CSDN博客》的博客文章,涉及了overlay设计的Vivado工程细节。在使用PYNQ调试MIPI驱动之前,需要搭建

Zynq开发-使用PYNQ快速入门摄像头MIPI驱动(OV5640)

目录 1. 简介 2. 配置代码 2.1 初始化寄存器 2.2 分辨率寄存器 2.3 白平衡寄存器 2.4 配置寄存器代码 2.5 顶层代码 3. 细节指引 4. 总结 1. 简介 PYNQ是一种基于Python的开发环境,专门设计用于快速、简便地在Xilinx的Zynq平台上进行开发。在《Zynq开发之-PYNQ配置,XVC(Xilinx Virtual Cable

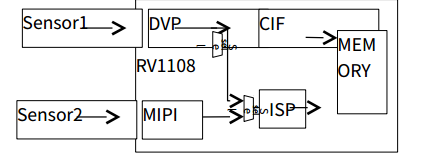

rk芯片的camera模组接口cif接口和mipi接口的区别

从rk出的rv1108芯片demo板上的硬件连接框图如下,会发现有两个camera接口,分别是mipi接口的主摄像头,和使用cif的次摄像头。从名字上看,mipi(mobile industry processor interface),在rv1108的芯片上主要分为dsi和csi,也就是用于视频输出的显示接口和用于视频输入的camera接口。cif(camera interface)就比较单

基于FPGA实现的HDMI TO MIPI扩展显示器方案

FPGA方案,HDMI IN接收原始HDMI 信号,输出显示到LCD 屏上 客户应用:扩展显示器 主要特性: 1.支持2K以下任意分辨率显示 2.支持OSD 叠加多个图层 3.支持MIPI/EDP/LVDS/RGB屏 4.支持放大缩小匹配屏分辨率 5.零延时,输入即输出 6.支持音频信号独立输出 7.可定制功能,扩展应用

Jetson Orin NX L4T35.5.0平台LT6911芯片 调试记录(1)MIPI问题调试

1.前言 硬件: JetsonOrinNX16GB, 35.5.0 转换芯片: 龙讯LT6911 dts配置 mode0 { // E2832_1920x1080_60Fpsmclk_khz = "24000";num_lanes = "4";tegra_sinterface = "serial_a";phy_mode = "DPHY";discontinuous_clk = "

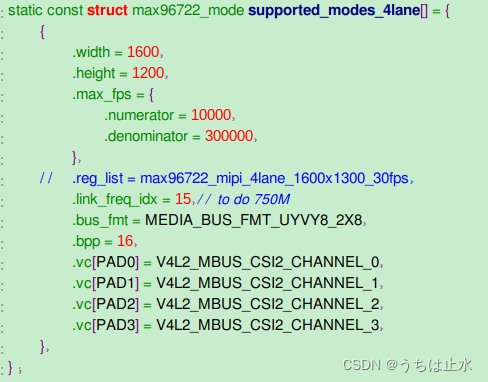

RK3588平台MIPI CSI调试错误记录

rkcif-mipi-lvds2: ERROR: csi size err, intstat:0x1000000, lastline:0x438, cnt 10 这里0x438 表示场的分辨率只到1080大小,但是驱动配置里超过这个大小了。 对应驱动代码修改: 1200 --》 1080 就可以了。

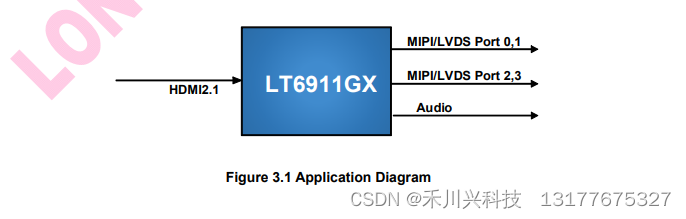

LT6911GX HDMI2.1 至四端口 MIPI/LVDS,带音频 龙迅方案

1. 描述LT®6911GX 是一款面向 VR / 显示应用的高性能 HDMI2.1 至 MIPI 或 LVDS 芯片。HDCP RX作为HDCP中继器的上游,可以与其他芯片的HDCP TX配合使用,实现中继器功能。对于 HDMI2.1 输入,LT6911GX 可配置为 3/4 通道。自适应均衡功能使其适合长电缆应用,最大带宽高达 32Gbps。对于 MIPI 输出,LT6911GX 具有可配置的

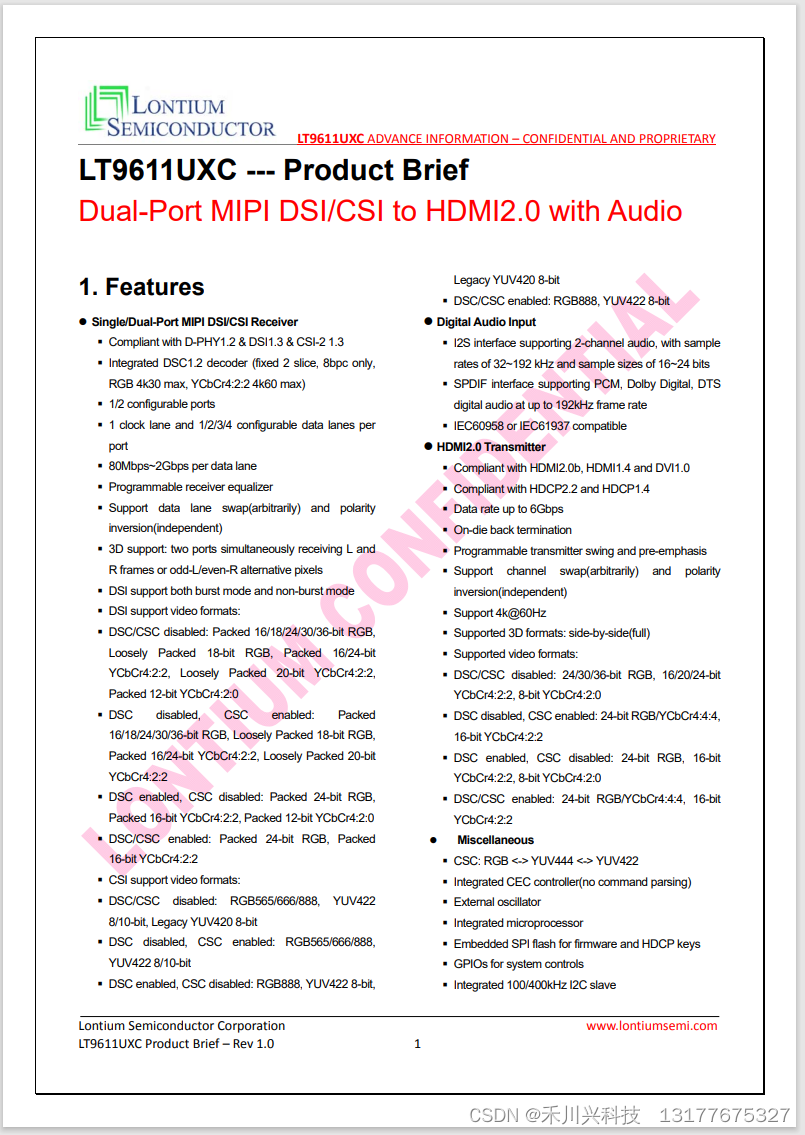

LT9611UXC双端口 MIPI DSI/CSI 转 HDMI2.0,带音频

1. 说明 LT®9611UXC 是一款高性能 MIPI DSI/CSI 至 HDMI2.0 转换器。MIPI DSI/CSI 输入具有可配置的单端口或双端口,具有 1 个高速时钟通道和 1~4 个高速数据通道,工作速率最高为 2Gbps/通道,可支持高达 16Gbps 的总带宽。 LT9611UXC 支持突发模式 DSI 视频数据传输,还支持灵活的视频数据映射路径。集成的 DSC 解码器可实现

国产POL8903 LVDS转MIPI带旋转功能方案介绍

一、芯片简介 1、系统 高性能 MIPS 32bit CPU 内核: 高性能 DSP 内核图像处理单元 16KB指令 Cache 16KB数据 Cache 96KB片上 SRAM 内嵌DDR3控制器 2、 LVDS 输入 支持1或者2通道 LVDS 输入 支持最大1920x1080@60Hz输入 兼容 VESA 和 JEIDA 格式 通道内5条差分信号对,支持1clock/

液晶屏MIPI接口与LVDS接口区别

原文链接:http://bbs.elecfans.com/jishu_887561_1_1.html 液晶屏接口类型有LVDS接口、MIPI DSIDSI接口(下文只讨论液晶屏LVDS接口,不讨论其它应用的LVDS接口,因此说到LVDS接口时无特殊说明都是指液晶屏LVDS接口),它们的主要信号成分都是5组差分对,其中1组时钟CLK,4组DATA(MIPI DSI接口中称之为lane),

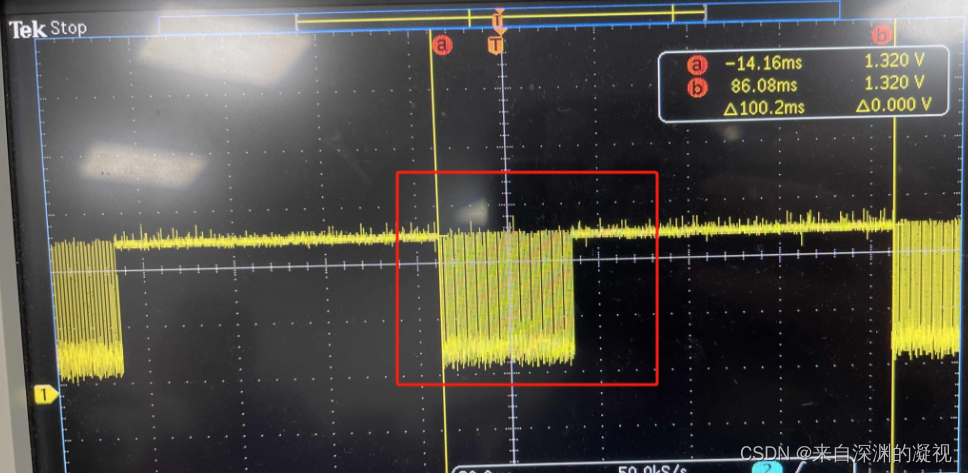

高通camera mipi不通的解决方法 .

打开mipi中断的状态开关,也就是一个注册mipi中断的软件上的宏定义。 首先你要确定你的camera是几lane的,如果lane是对的,检查下模组,比如是2M的camera,是否真的使用了2lane,模组内部可能会断路使用一个lane。 其次你的平台配置如何,mipi的配置是否在stream on之前,中断状态是否有? 再次,mipi的配置高通7x和8x是不一样的,走csi和csid的流程不通

Harmony鸿蒙南向驱动开发-MIPI CSI

CSI(Camera Serial Interface)是由MIPI联盟下Camera工作组指定的接口标准。CSI-2是MIPI CSI第二版,主要由应用层、协议层、物理层组成,最大支持4通道数据传输、单线传输速度高达1Gb/s。 物理层支持HS(High Speed)和LP(Low Speed)两种工作模式。HS模式下采用低压差分信号,功耗较大,但数据传输速率可以很高(数据速率为80M~1Gb

[RK3588-Android12] 调试MIPI-双通道-压缩屏(Video Mode/MIPI Dphy 8Lane/DSC 144HZ)

问题描述 被测屏幕:小米Pad6 分辨率:1800X2880 模式:Video Mode/MIPI Dphy 8Lane/DSC 144HZ PPS: 11 00 00 89 30 80 0B 40 03 84 00 14 01 C2 01 C2 02 00 01 F4 00 20 01 AB 00 06 00 0D 05 7A 06 1A 18 00 10 F0 03 0C 20 00 06

FPGA高端图像处理开发板-->鲲叔4EV:12G-SDI、4K HDMI2.0、MIPI等接口谁敢与我争锋?

目录 前言鲲叔4EV----高端FPGA图像处理开发板核心板描述底板描述配套例程源码描述配套服务描述开发板测试视频演示开发板获取 前言 在CSDN写博客传播FPGA开发经验已经一年多了,帮助了不少人,也得罪了不少人,有的人用我的代码赢得了某些比赛、得到了心仪的offer,也有的人天天骂我,anyway,哪怕只要还能帮助一个即将毕业的学生找到工作,哪怕只要还能帮助一个工程师解决项目

FPGA高端项目:解码索尼IMX327 MIPI相机+图像缩放+HDMI输出,提供开发板+工程源码+技术支持

目录 1、前言2、相关方案推荐本博主所有FPGA工程项目-->汇总目录我这里已有的 MIPI 编解码方案 3、本 MIPI CSI-RX IP 介绍4、个人 FPGA高端图像处理开发板简介5、详细设计方案设计原理框图IMX327 及其配置MIPI CSI RX图像 ISP 处理自研HLS图像缩放详解图像缓存HDMI输出工程源码架构时序约束 6、工程源码1详解-->IMX327解码+HLS图像

MIPI CSI-2 Low Level Protocol解读

一、Low Level Protocol介绍 LLP 是一种面向字节的基于数据包的协议,支持使用短数据包和长数据包格式传输任意数据。为简单起见,本节中的所有示例均为单通道配置。 LLP特性: 传输任意数据(与有效载荷无关) 8 位字大小 在同一链路上支持多达四个交错的虚拟通道 用于帧开始、帧结束、行开始和行结束信息的特殊数据包 特定于应用程序的有效负载数据的类型、像素深度和格式的描

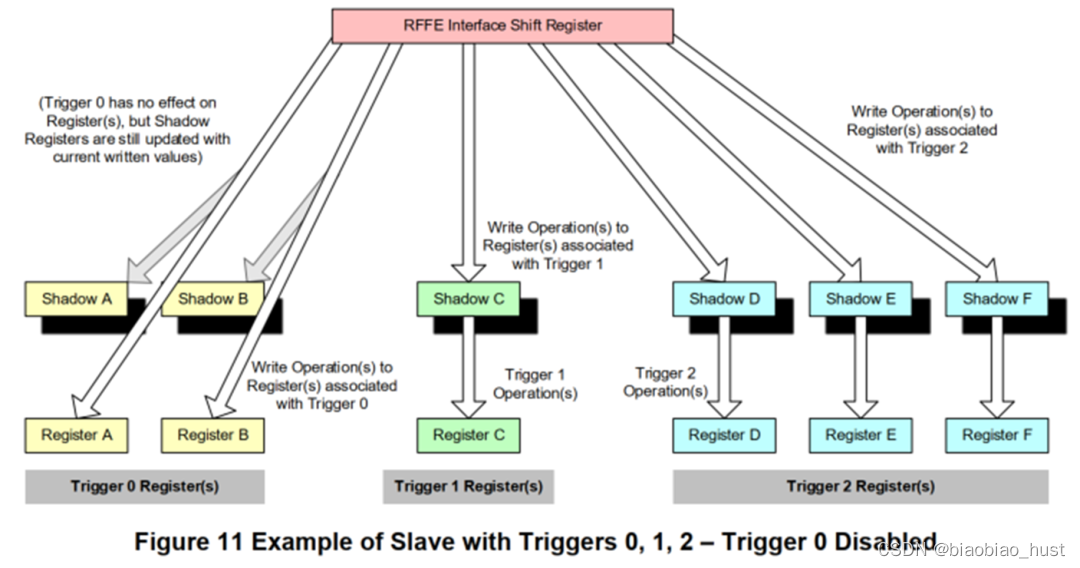

MIPI RFFE接口

1. 概况 MIPI RFFE是一种专门针对当前及未来无线系统在射频(RF)前端控制界面规范。随着手机射频系统日趋复杂,业界需要一个单一控制界面解决方案。MIPI联盟的RF前端控制界面(RFFE)规范通过提供一个可连接到收发器或无线电的总线界面解决了这一难题,可用于给多种射频前端设备,如低噪声放大器(LNA)、功率放大器(PA)、天线开关、天线调谐器、DC/DC转换器、滤波器、感测

FPGA高端项目:解码索尼IMX390 MIPI相机转HDMI输出,提供FPGA开发板+2套工程源码+技术支持

目录 1、前言2、相关方案推荐本博主所有FPGA工程项目-->汇总目录我这里已有的 MIPI 编解码方案 3、本 MIPI CSI-RX IP 介绍4、个人 FPGA高端图像处理开发板简介5、详细设计方案设计原理框图IMX390 及其配置MIPI CSI RX图像 ISP 处理图像缓存HDMI输出工程源码架构 6、工程源码1详解-->IMX390 解码+FDMA图像缓存+HDMI输出7、工程

十.固态激光雷达--扫地机的避障单线激光测距模块的cmos sensor mipi接口知识20240322

十.固态激光雷达–扫地机避障的单线激光测距模块的重要器件介绍介绍 文章目录 十.固态激光雷达--扫地机避障的单线激光测距模块的重要器件介绍介绍10.1 背景10.2 sensor mipi与DVP 接口比较10.2.1 DVP接口10.2.2 MIPI接口10.2.3 DVP/MIPI选择 10.3 sensor 卷帘快门(Rolling Shutter)与全局快门(Global Shut

![[RK3588-Android12] 调试MIPI-双通道-压缩屏(Video Mode/MIPI Dphy 8Lane/DSC 144HZ)](https://img-blog.csdnimg.cn/direct/2ac86bc95b754720a4357ee834fd793c.png)