本文主要是介绍Power Struggles Revisiting the RISC vs. CISC Debate on Contemporary ARM and x86 Architectures,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

Power Struggles: Revisiting the RISC vs. CISC Debate on Contemporary ARM and x86 Architectures (2013)

-

摘要:

- RISC和CISC的争论在1980s激化,而当时芯片面积和处理器设计复杂度是主要的限制因素,并且当时台式机和服务器独占计算领域

- 相比于1980s,现在能耗和功耗是主要的设计约束,计算领域也发生了变化,ARM的平板电脑和手机的增长已经超过了x86的台式机和笔记本电脑的增长情况

- 传统的低功耗ARM ISA正在进入高性能服务器市场,而x86则正在进入移动低功耗市场。这种情况下,ISA在性能还是能效上的固有作用的问题越来越重要

- 论文工作:

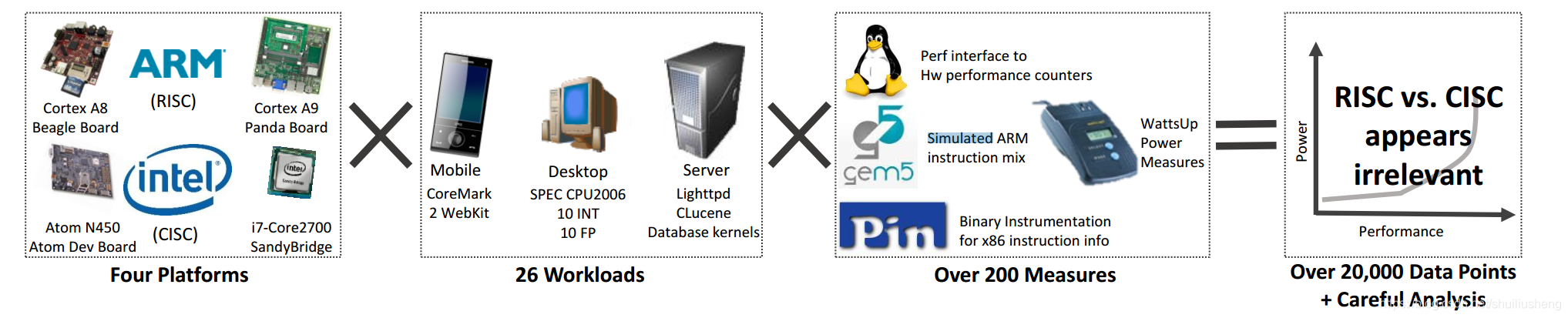

- 论文使用了移动,台式机和服务器计算的工作负载对ARM Cortex-A8和Cortex-A9以及Intel Atom和Sandybridge i7微处理器进行了测量

- 论文证明了ISA在现代微处理器的性能和能效中的作用(ISA是RISC还是CISC似乎不重要了)

- 论文发现ARM和x86处理器只是针对不同的性能级别进行了优化的工程设计点。在一类ISA或另一类ISA中,根本没有更高的能效

- 在A8或更高的性能水平上,RISC / CISC与性能,功率和能耗无关。对于最低性能水平的处理器尚未研究。

- 尽管ISA不断发展,但它一直专注于实现专业化,并且在很大程度上与RISC或CISC无关。

-

介绍

-

任何ISA研究都面临着将与ISA正交的多个实现因素和受ISA影响或驱动的因素分开的挑战。当考虑进行能耗测量/分析时,挑战更加严重。此外,ISA可能需要某些微体系结构功能,而另一些可能是由独立于ISA的性能和应用领域目标所决定的

-

独立于ISA的因素包括:工艺,设备优化(高性能,低能耗/低待机功耗晶体管),内存带宽,I/O设备影响,OS,编译器和工作负载。

-

论文的研究ISA的方法

-

为具有相似微体系结构的每个ISA考虑多个芯片,使用已有的技术模型来区分工艺技术带来的影响

-

在所有的芯片上使用相同的OS和编译器前端,并且构造不太依赖于OS的工作负载

-

论文的数据:www.cs.wisc.edu/vertical/isa-power-struggles

-

-

论文的主要关注点:whether and, if so, how the ISA impacts performance and power

-

论文实验的主要发现:

- 尽管平均周期数差距小于2.5x,但是不同实现之间的性能差距仍旧较大

- 指令数和指令之间的占比情况是ISA不相关的(Instruction count and mix are ISA-independent to first order.)

- 性能差异来自于独立于ISA的微体系结构差异产生

- 能耗与ISA无关

- ISA差异对实现有影响,但是现代微体系结构技术使它们无济于事。一个ISA从根本上说并不是更有效的(one ISA is not fundamentally more efficient)

- ARM和x86实现只是针对不同性能级别进行了优化的设计点(design points )

-

微体系结构的影响在性能,功耗和能耗的影响中占据了主导地位。

-

尽管ISA是RISC还是CISC似乎无关紧要,但ISA仍在发展。表达更多的语义信息可以提高性能(x86 SSE,更大的地址空间),更好的安全性(ARM Trustzone),更好的虚拟化等。

-

-

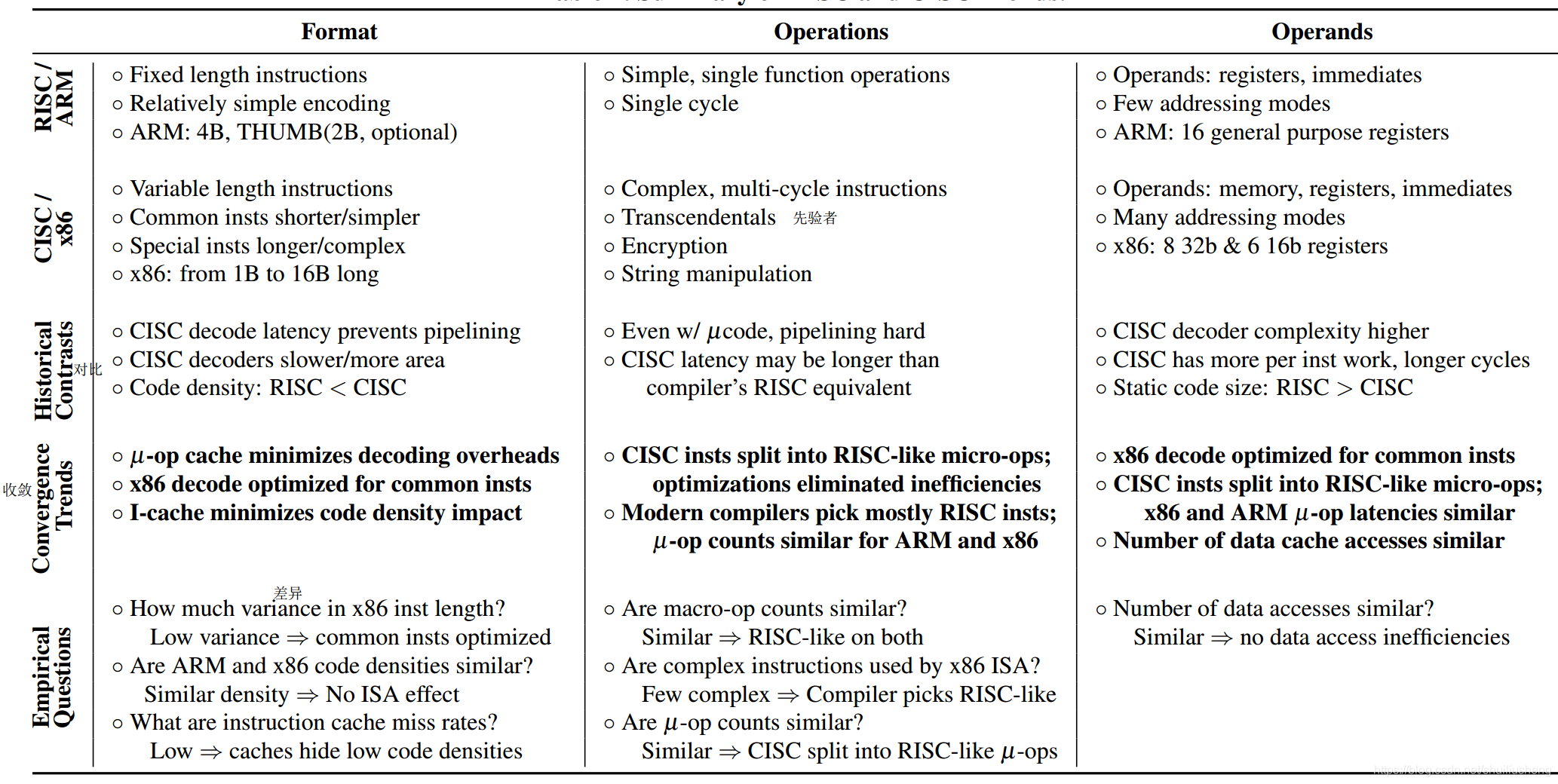

RISC和CISC趋势总结

-

实现的平台和应用

-

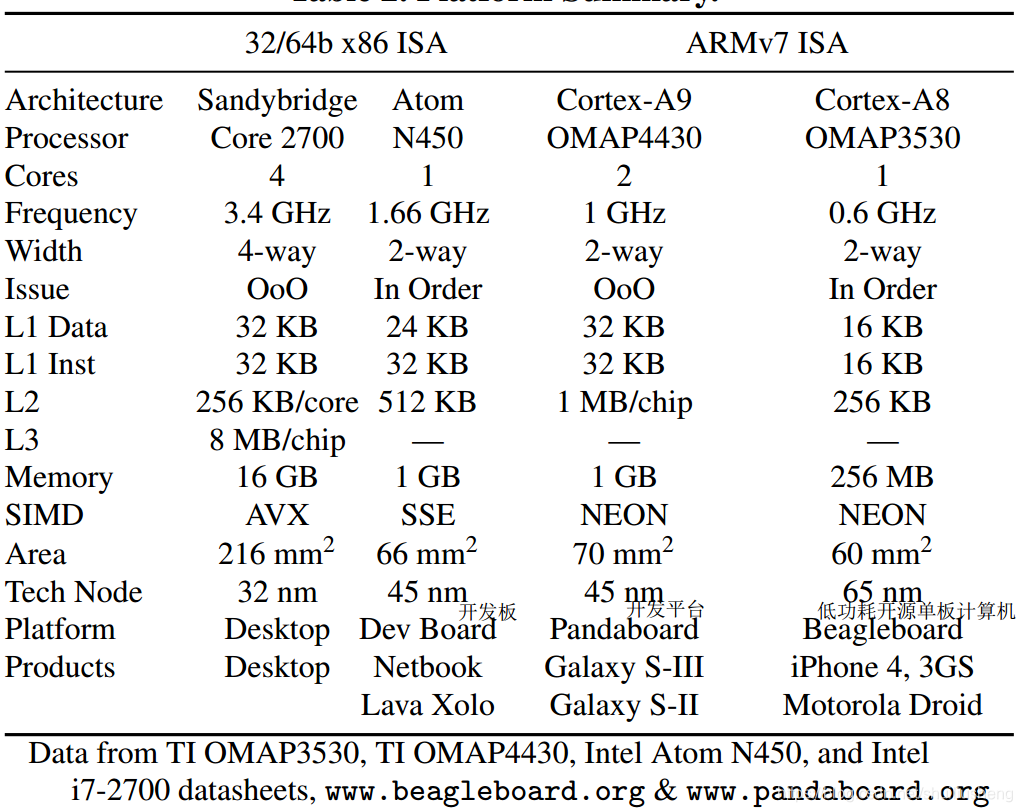

硬件平台:ARM和x86的各两种芯片实现(选择标准:尽可能让非处理器特征相似)

-

操作系统:Linux 2.6 LTS内核,带有一些特定于主板的小补丁(为了在使用性能计数器子系统时能够获得准确的结果)

-

编译器:经过验证的gcc 4.4,优化选项O3,禁用了特定于机器的调整。对于x86,由于ARM的64位平台不可用,因此选择32位。对于ARM,禁用Thumb指令。允许编译器进行自动矢量化,但是生成的SIMD很少(SSE,Neon)

-

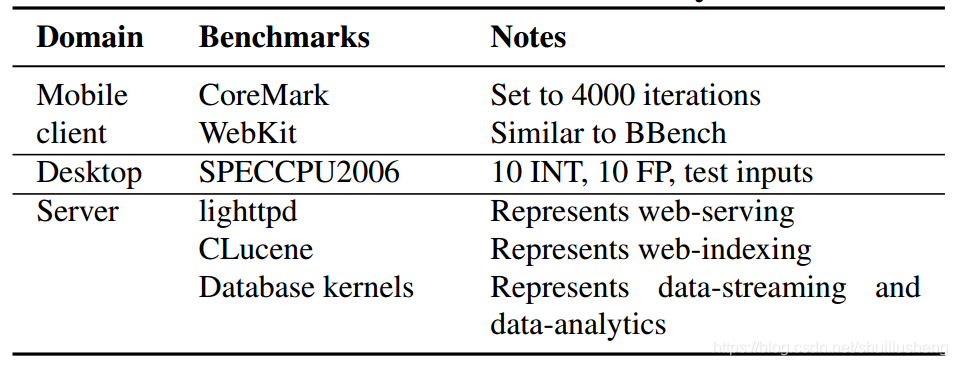

应用程序:均为单线程,只关注单核的情况

-

BBench是最近提出的智能手机基准测试套件,它是“一种网页渲染基准测试,包括当今Internet上11个最受欢迎的网站” 。(使用跨平台的WebKit以减少在不同平台上浏览器的差异)

-

SPECCPU2006是一个广为人知的标准台式机基准测试,可深入了解核心行为。(由于Cortex-A8的内存限制,只选择了部分合适的程序)

-

CLucene(clucene.sourceforge.net),这是一种高效的跨平台索引实现,类似于CloudSuite的Nutch

-

-

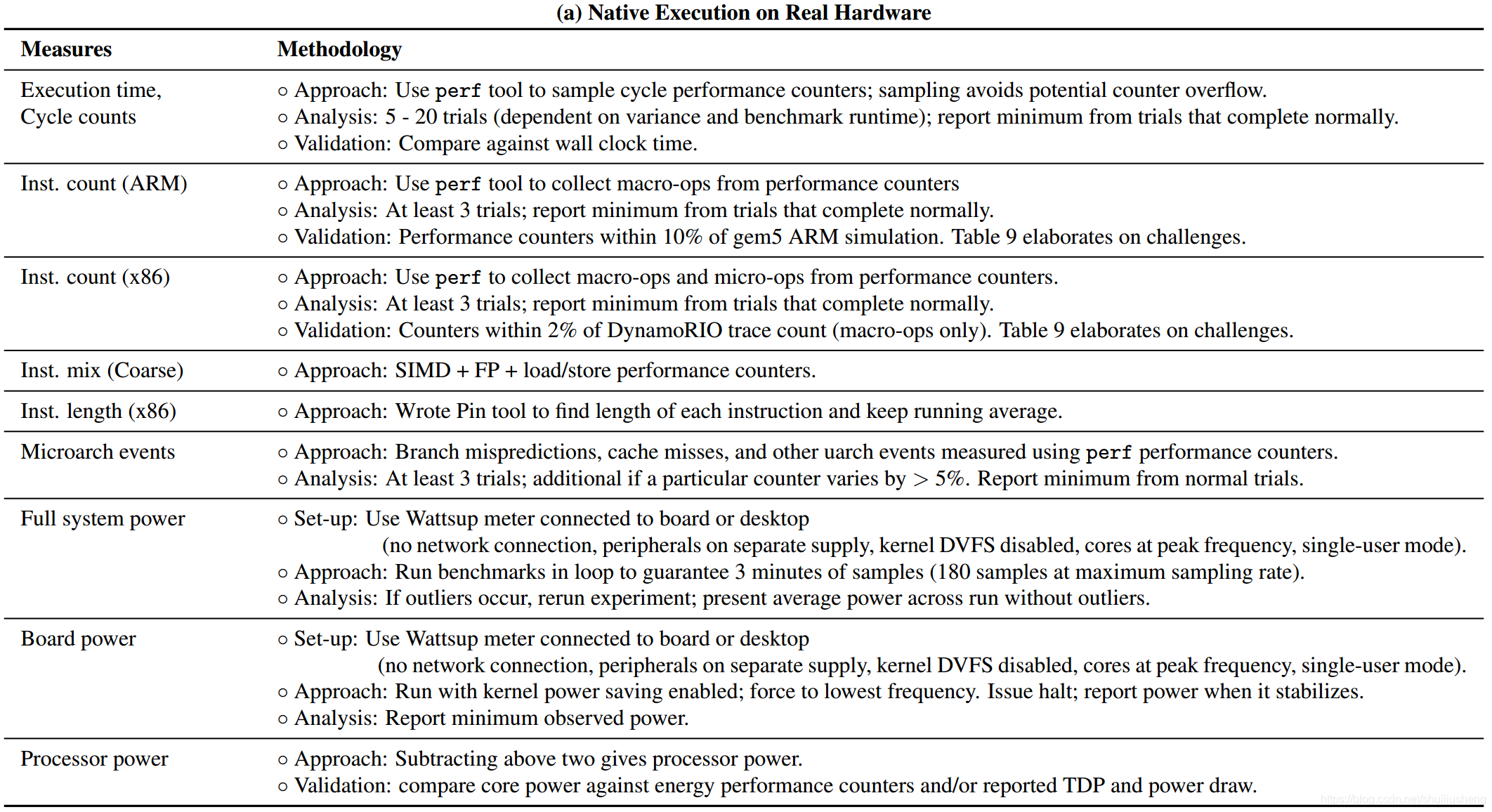

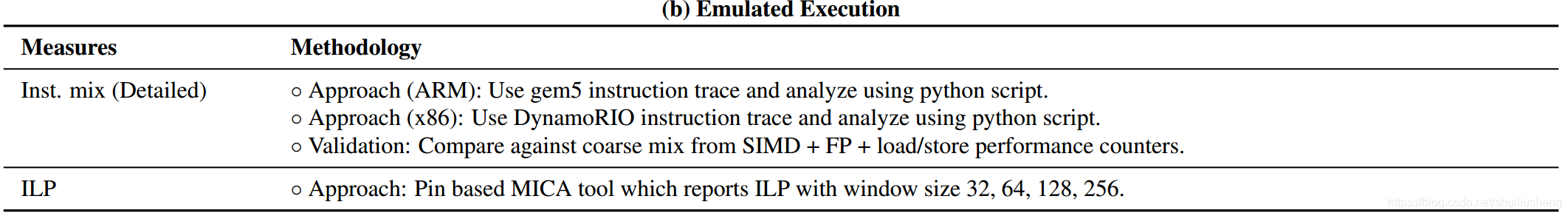

实验的方法总结

-

-

数据分析的方法

- 性能分析流程

- 记录每个基准测试的执行时间

- 使用周期数来归一化频率的影响

- 根据测量的动态指令数(包括宏操作和微操作)来分析周期数的差异和ISA的影响

- 使用指令分布,代码二进制大小和平均动态指令长度来分析ISA的影响

- 根据详细的微体系结构事件来分析非ISA影响的性能差异

- 将性能差异归因于频率/ISA/ISA无关的微体系结构特征。 分析ISA是否强制微体系结构特性的定性原因。

- 功耗和能耗的分析流程

- 记录每个基准程序原始测量的功耗

- 为了排除工艺技术的影响,将所有处理器缩放到45nm,并且将频率标准化到1GHz

- 通过分析原始的能耗,来了解功耗和性能之间的相互作用

- 从能耗方面,定性的说明ISA对微体系结构的影响

- trade-off分析流程

- 结合性能和能耗的测量结果,使用 Pareto曲线比较处理器的实现

- 使用能量性能帕累托边界比较实测和综合处理器的实现

- 性能分析流程

-

性能分析

-

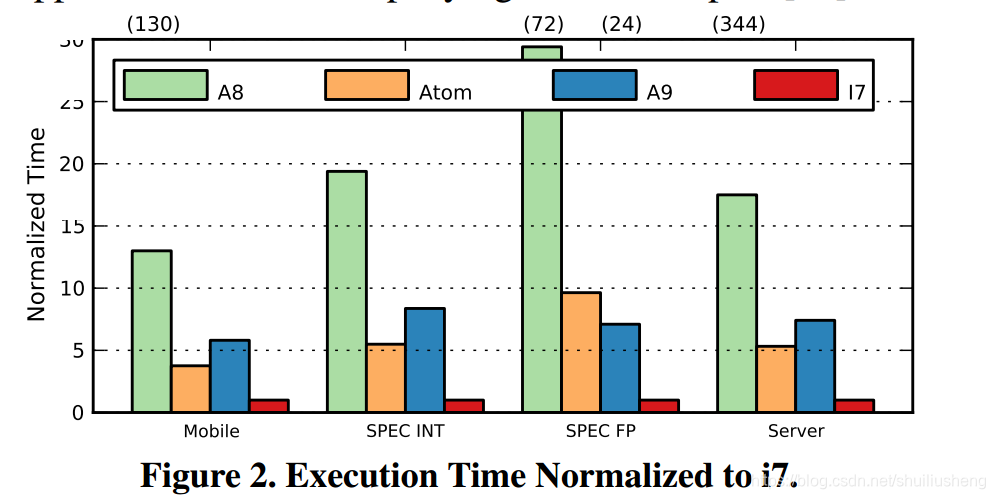

执行时间的比较(原始执行时间,括弧内为异常值):四个平台之间存在很大的性能差距,因为频率范围从600 MHz到3.4 GHz,并且微体系结构有很大的不同。

-

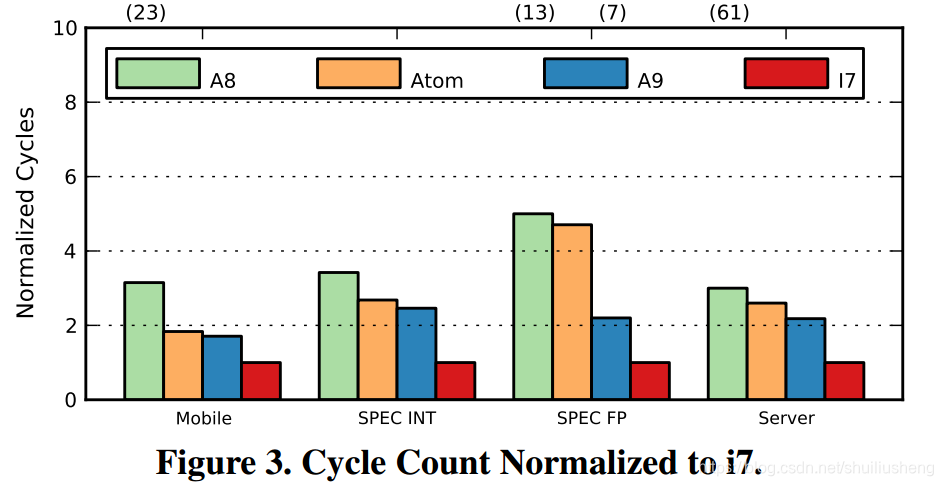

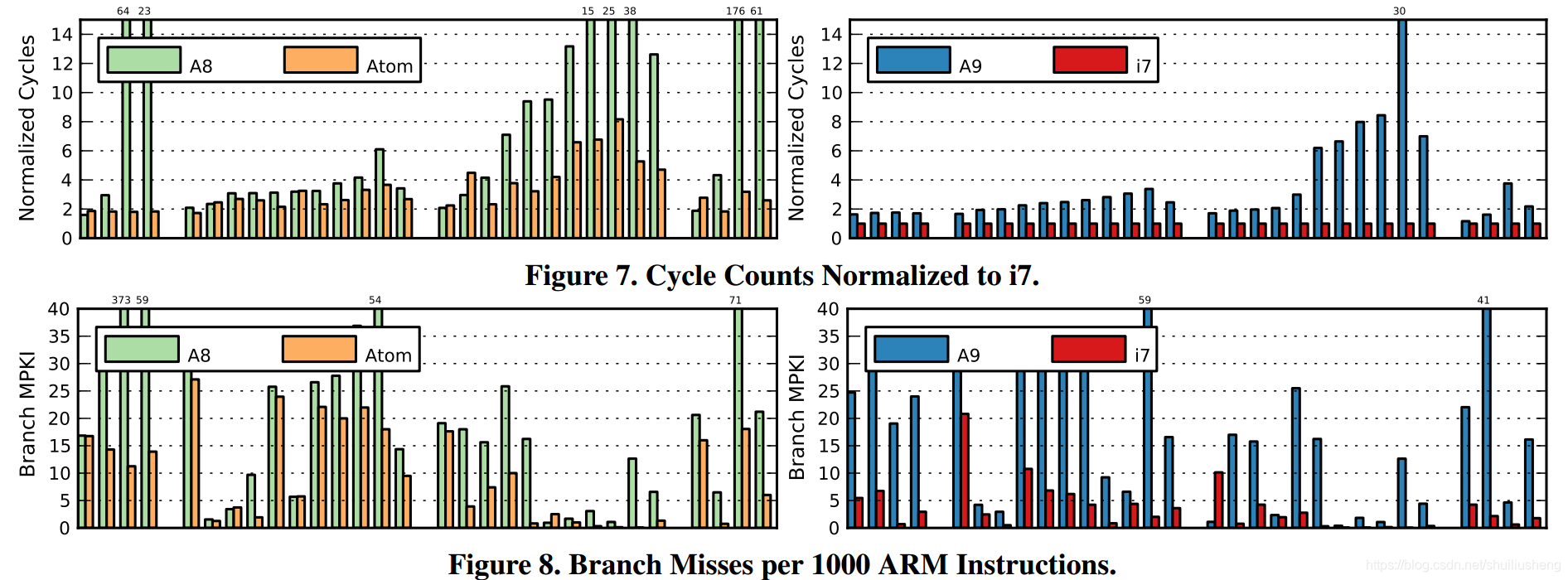

时钟周期数比较:

-

乱序实现的A9和i7之间的每个测试程序的周期数差距小于2.5×

-

按序实现的A8和Atom之间,周期数差距小于1.5x

-

当按周期数归一化后,性能差异在按序和乱序之间彼此比较时差距小于2.5x

-

-

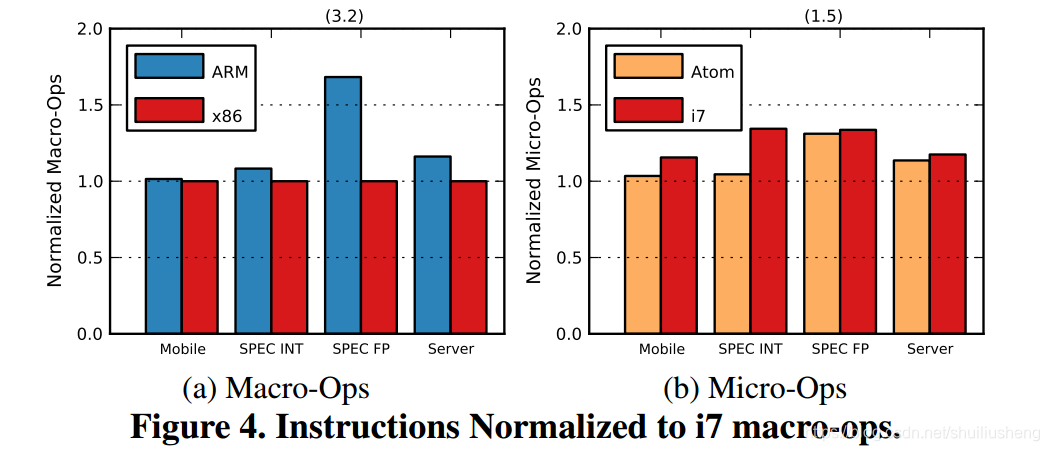

指令数比较:

-

指令数在ISA之间类似;(暗示gcc从x86 ISA选择类似RISC的指令)

-

SPEC FP中所有ARM的异常值是由于x86仅支持超验(transcendental) FP操作

-

x86微操作与宏操作的比率通常小于1.3x(再次表明gcc选择了类似RISC的指令)

-

指令和周期数意味着x86实现的CPI更低,微体系结构可以克服x86 ISA开销(如果有)

-

-

指令格式:

-

SPEC INT,SPEC FP和移动工作负载的ARM和x86平均二进制大小相似,表明代码密度相似

-

执行的x86指令平均比ARM指令短多达25%:典型的简短x86指令。

-

x86 FP基准测试往往具有更复杂的指令,它们的指令编码更长

-

-

指令分布(mix):

-

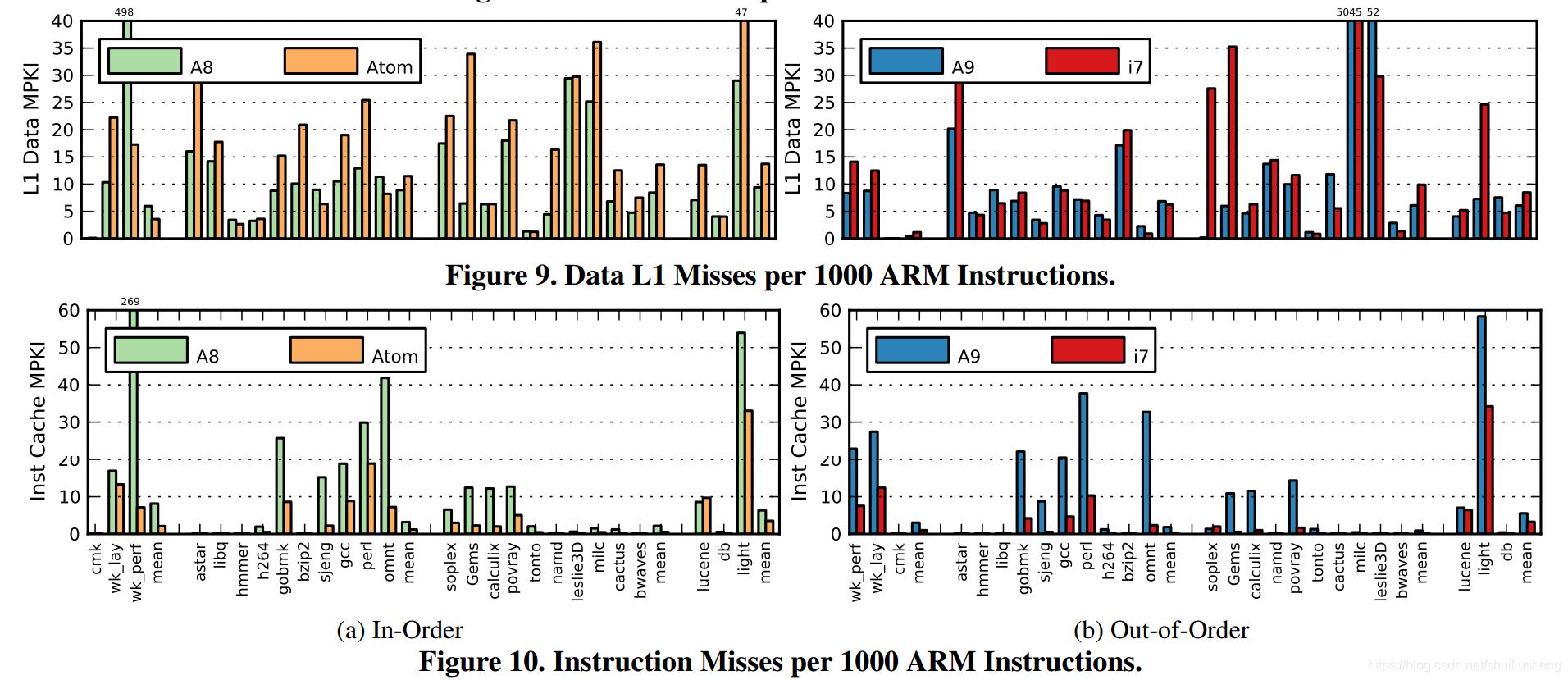

对于所有程序,整个ISA的load和store的占比相似,这表明ISA不会导致数据访问的显着差异。

-

ARM的大量指令是由于缺少诸如fsincon,fyl2xpl之类的FP指令

-

结合指令数和指令分布,结论是ISA在x86和ARM实现中的影响无法区分

-

-

微体系结构的影响:微架构对性能有重大影响。 ARM和x86体系结构具有相似的指令计数。 高度精确的分支预测器和大型缓存尤其有效地使x86体系结构能够维持高性能。

-

-

功耗和能耗分析

-

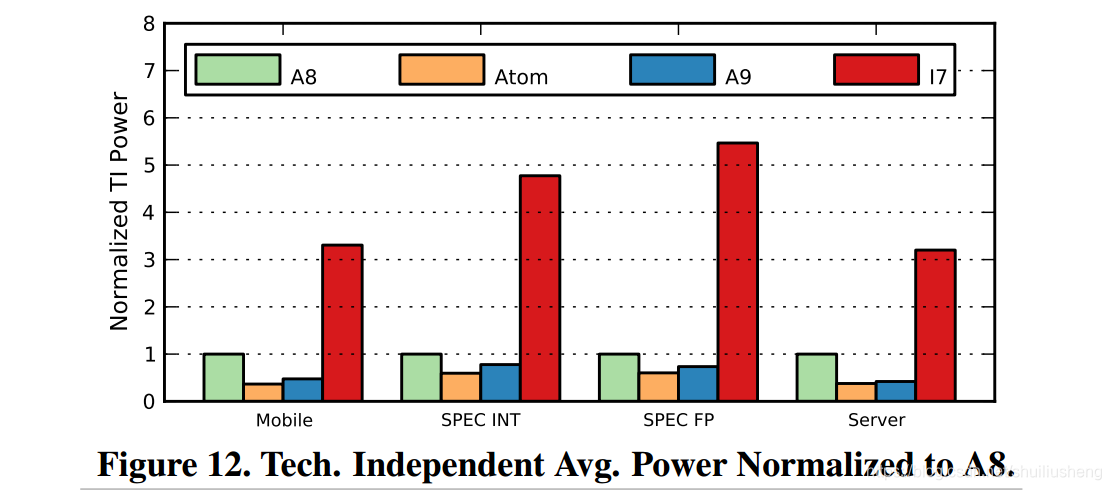

随着频率和技术的扩展,ISA无关紧要

-

i7处理器被设计为具有高性能,但未对功耗进行优化

-

Atom的功耗与ARM A8和A9相当

-

由于功率和性能都是主要的设计选择,因此能耗也主要受到设计选择的影响,ISA对能耗的影响微不足道

-

性能优化的选择比ISA对功耗的影响更大

-

这篇关于Power Struggles Revisiting the RISC vs. CISC Debate on Contemporary ARM and x86 Architectures的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!