本文主要是介绍Verilog HDL表决器电路设计,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

一、电路基本原理

1.电路是多输入,单输出组合逻辑电路

2.输出根据输入比较关系,确定为0或1

3.输入为奇数

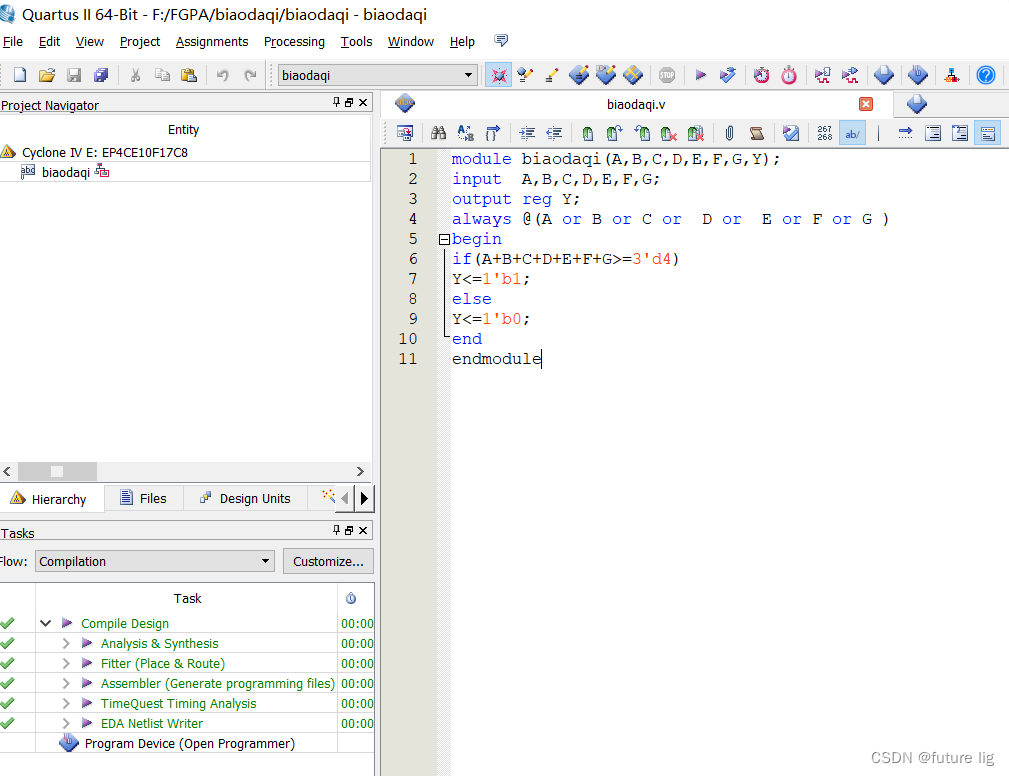

二、Verilog代码实现(下面以七人表决器设计为例子)

代码实现:

module biaojueqi(A,B,C,D,E,F,G,Y);//注意工程名,根据自己工程名而定

input A,B,C,D,E,F,G;

output reg Y;

always @(A or B or C or D or E or F or G )

begin

if(A+B+C+D+E+F+G>=3'd4)

Y<=1'b1;

else

Y<=1'b0;

end

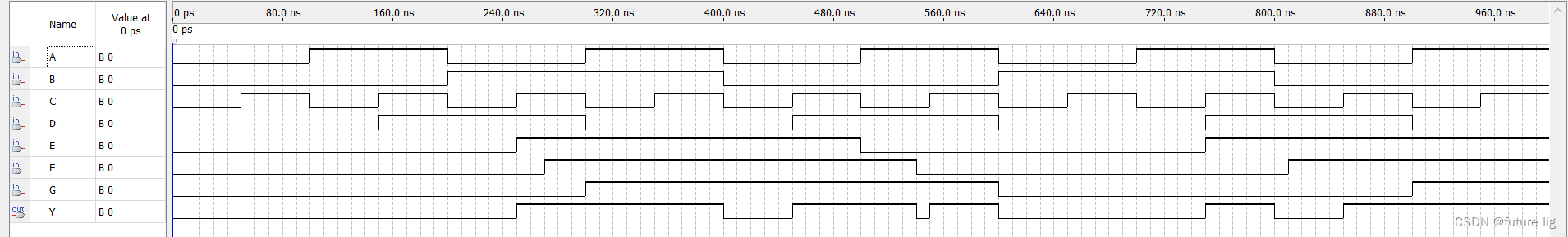

endmodule编译代码,波形图如下

三、任务实现

1.新建工程

2.设计输入

3.工程编译

4.设计仿真

5.器件选择与管脚约束

6.配置烧写

这篇关于Verilog HDL表决器电路设计的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!