hdl专题

ADI HDL 和 Vivado版本对应

ADI HDL 和 Vivado版本对应 ADI HdlVivadoQuartushdl_2014_r12013.414.0hdl_2014_r22014.214.0hdl_2015_r12014.4.115.0hdl_2015_r22015.2.115.1hdl_2016_r12015.4.215.1hdl_2016_r22016.216.0hdl_2017_r12016.416.1hdl_2

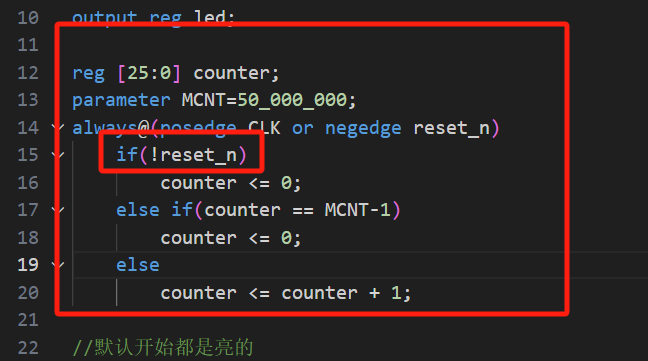

FPGA第 8 篇,硬件描述语言Verilog HDL,初识Verilog HDL

前言 我们都知道 FPGA 是一种高度可编程的集成电路,适用于实现各种数字逻辑功能,而 Verilog HDL是一种广泛使用的硬件描述语言(Hardware Description Language, HDL),主要用于数字电子系统的描述、仿真和综合,以及其他数字系统的逻辑设计。通过使用 Verilog,工程师可以高效地设计和验证 FPGA 电路,从而实现所需的数字系统功能。

Verilog | HDL 音乐盒设计(代码类)

博主github:https://github.com/MichaelBeechan 博主CSDN:https://blog.csdn.net/u011344545 module music(clk,beep,pause,stop,switch,led); //定义时钟及几个功能变量input clk,pause,switch,stop; //输入变量out

Verilog | HDL 音乐流水灯(代码类)

博主github:https://github.com/MichaelBeechan 博主CSDN:https://blog.csdn.net/u011344545 module beyond(clk,beep,led);input clk;output beep;output [7:0]led;reg beep;reg [22:0]i;reg clk_4hz;reg [7:0]l

Verilog | HDL LCD显示(代码类)

博主github:https://github.com/MichaelBeechan 博主CSDN:https://blog.csdn.net/u011344545 module lcd(clk, rs, rw, en,dat,switch2); input clk,switch2; output [7:0] dat; output rs,rw,en; reg e; reg [7:0]

HDL-A/1-110VAC-2电流继电器 JOSEF约瑟 导轨安装

一. 应用 HDL系列电流继电器是静态型,不带方向性的、瞬动、交流电流继电器。可用于电力系统输电线,电机过负荷和短路保护中,作为启动元件。 继电器对短路电流中的直流分量不敏感,因此可用于要求哲态超小的线路中,改继电器由集成电路构成执行回路, 有灵敏度高、动作速度快、功耗小、整定方便等特点。继电器的直流电源和出口继电器由信号指示灯监视。 用户可根据具体情况直接控制被保护设备。继电

Verilog HDL基础知识(二)

引言:本文继续介绍Verilog HDL基础知识,重点介绍赋值语句、阻塞与非阻塞、循环语句、同步与异步、函数与任务语法知识。 1. 赋值语句 在Verilog中,有两种进行赋值的方法,即连续赋值语句和过程赋值语句(块)。 1.1 连续赋值语句 连续赋值用于表示组合逻辑。左侧必须是Net数据类型即wire和tri类型。 连续赋值始终处于活动状态,这意味着,对右侧值的任何更改都会导致赋值左侧

Verilog HDL基础知识(一)

引言:本文我们介绍Verilog HDL的基础知识,重点对Verilog HDL的基本语法及其应用要点进行介绍。 1. Verilog HDL概述 什么是Verilog?Verilog是IEEE标准的硬件描述语言,一种基于文本的语言,用于描述最终将在硬件中实现的电路。Verilog和它的竞争对手VHDL一样,可以用于仿真和综合,实现对硬件进行建模。 Verilog最初是由Cadence收购的

fpga系列 HDL: 05 阻塞赋值(=)与非阻塞赋值(<=)

在Verilog硬件描述语言(HDL)中,信号的赋值方式主要分为两种:连续赋值和过程赋值。每种赋值方式有其独特的用途和语法,并适用于不同类型的电路描述。 1. 连续赋值(Continuous Assignment,assign 和=) 连续赋值主要用于描述组合逻辑,通常与assign关键字一起使用。它在顶层模块或过程块外部进行,用于对wire类型的信号赋值。 特点: 组合逻辑:连续赋值用于

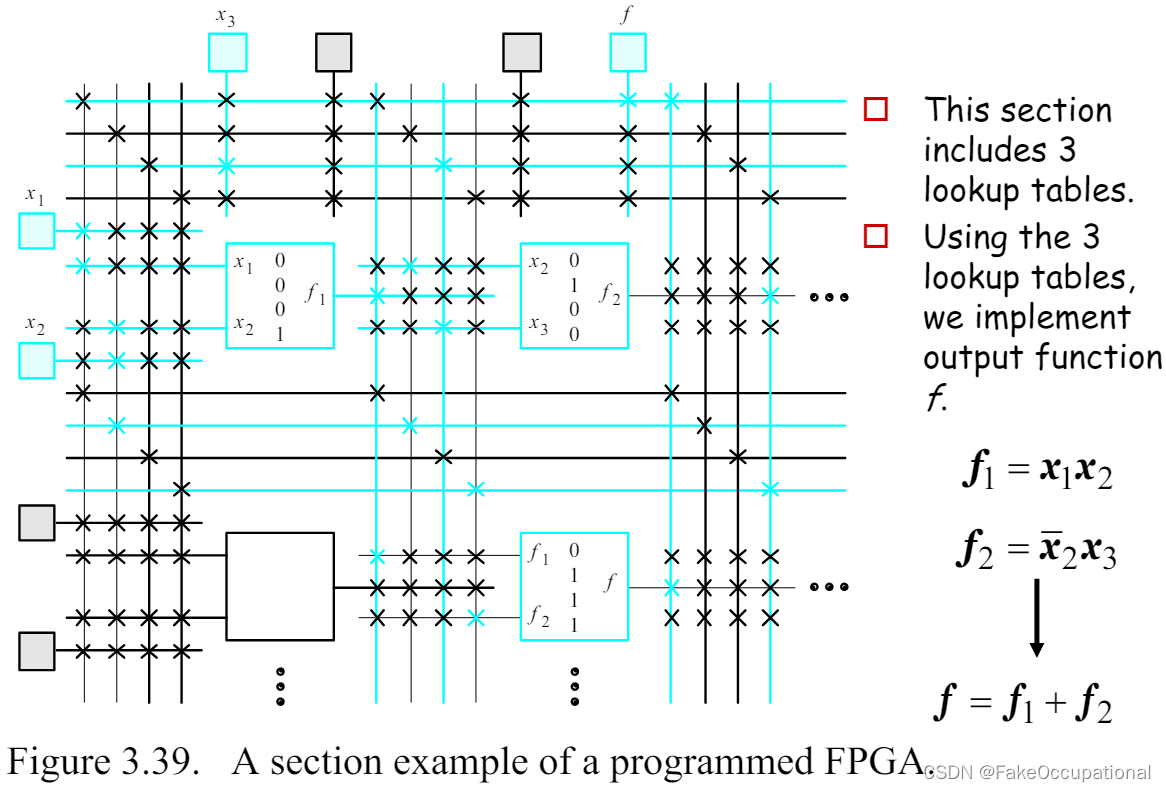

fpga系列 HDL 00 : 可编程逻辑器件原理

一次性可编程器件(融保险丝实现) 一次性可编程器件(One-Time Programmable Device,简称 OTP)是一种在制造后仅能编程一次的存储设备。OTP器件在编程后数据不可更改。这些器件在很多应用场景中具有独特的优势和用途。 示例 MMI 16R6 可编程元件(显示为保险丝,下图中的波浪线)将真实输入和补码输入连接到与门。这些与门(也称为乘积项,下图中的面包片)通过“或

Verilog HDL的基本语法

Verilog HDL的基本语法 前言 Verilog HDL是一种用于数字逻辑电路设计的语言。用Verilog HDL描述的电路设计就是该电路的Verilog HDL模型。Verilog HDL既是一种行为描述的语言也是一种结构描述的语言。这也就是说,既可以用电路的功能描述也可以用元器件和它们之间的连接来建立所设计电路的Verilog HDL模型。Verilog模型可以

Verilog HDL的程序结构及其描述

这篇博文是写给要入门Verilog HDL及其初学者的,也算是我对Verilog HDL学习的一个总结,主要是Verilog HDL的程序结构及其描述,如果有错,欢迎评论指出。 一、Verilog HDL的程序结构 首先我们不开始讲Verilog HDL的语法,我们从Verilog HDL的程序结构出发。相信大家都看过芯片吧,它有个名字,有个外壳,外壳向外伸出有引脚(BGA封装的那种请不

Verilog HDL程序设计——基本要素

Verilog基本上熟悉了,继续整理一下Verilog的学习笔记吧。前面记载了Verilog的结构,写Verilog的结构有了,但是该怎么写呢?在写之前就得了解一下Verilog的一些基本要素了,也就是Verilog是怎么一点一点写出来的。 一、标识符与注释 前面已经说到,模块名的定义要符合标识符的定义,那么什么是标识符呢?它的语法是什么呢? ①标识符是赋给对象的唯一名称,

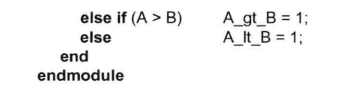

Verilog HDL常用综合语法

前面已经记录了一些组成Verilog的基本组成,可以用这些基本组成来构成表达式。这一节,就来记录一下把这些表达式构成一个文件的各种行为描述语句。 ①这里用Verilog基本要素进行的行为描述主要是针对综合来的,也就是可以设计出实际电路来的(行为描述语句有两大子集,一个是面向综合,一个是面向仿真)。②行为描述语句一般指放在always语句中。内容提纲如下所示: ·触发事件控制 ·条件语句

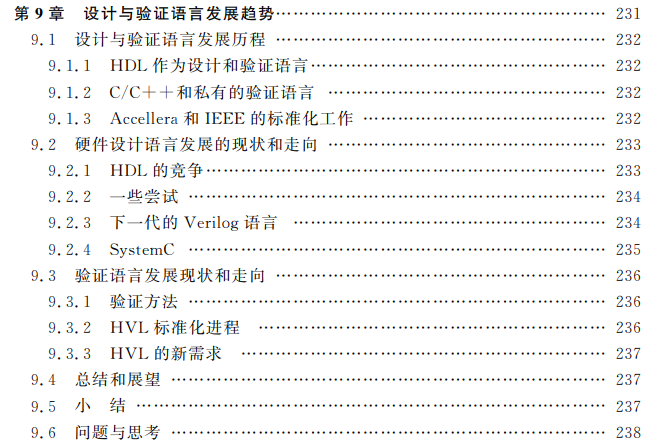

【数字IC/FPGA】书籍推荐(1)----《轻松成为设计高手--Verilog HDL实用精解》

在下这几年关于数字电路、Verilog、FPGA和IC方面的书前前后后都读了不少,发现了不少好书,也在一些废话书上浪费过时间。接下来会写一系列文章,把一部分读过的书做个测评,根据个人标准按十分制满分来打分分享给大家。 书名:轻松成为设计高手–Verilog HDL实用精解 内容:Verilog语法、设计方法学 评价:8.5分。属于是比较推荐的Verilog语法入门书籍,同时也包括一些

拔河游戏机——ABLE-HDL语言实现

兹于2016年12月,应《数字逻辑》课程设计的要求,本人在老师指导下用ABLE-HDL语言实现了拔河游戏机的功能。 拔河游戏机 1、题目描述 拔河游戏机用7个发光二极管排列成一行,开机后只有中间一个发亮,以此作为拔河的中心线,游戏双方各持一个按键,迅速地、不断地按动产生脉冲,谁按得快,亮点向谁方向移动,每按一次,亮点移动一次。任一方终端二极管发亮时这一方获胜,

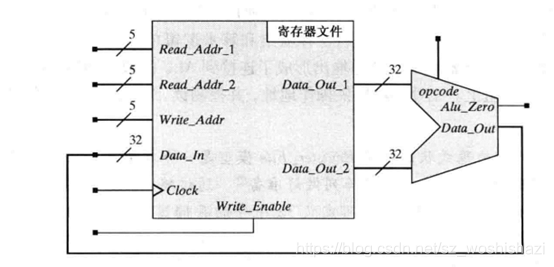

Verilog HDL高级数字设计 从零学习(四)

Verilog HDL高级数字设计 从零学习(四) 用循环算法的数字机模型函数和任务ASMD图计数器、移位寄存器和寄存器组的行为级模型 🔈声明: 🔑未经作者允许,禁止转载 🚩推荐一个IC、FPGA新手入门的好网站:👉快 点 击 进 入 学 习 吧👈 本章主要总结一下刚结束的第五章的内容,但由于第五章包含了亚稳态的知识,暂时还没有很懂,所以这部分内容会

Verilog HDL高级数字设计 从零学习(三)

Verilog HDL高级数字设计 从零学习(三) 行为建模基于布尔方程的组合逻辑行为级模型Verilog中的锁存器和电平敏感电路触发器和锁存器的周期性行为模型行为建模方式的比较线性反馈移位寄存器的数据流模型 🔈声明: 🔑未经作者允许,禁止转载 🚩推荐一个IC、FPGA新手入门的好网站:👉快 点 击 进 入 学 习 吧👈 由于第五章内容较多,所以分为

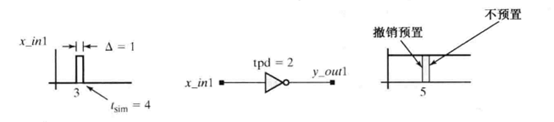

Verilog HDL高级数字设计 从零学习(二)

Verilog HDL高级数字设计 从零学习(二) 4.1 Verilog原语和设计封装4.2.1 Verilog中的四值逻辑4.2.2 测试方法4.3 传播延时 🔈声明: 🔑未经作者允许,禁止转载 🚩推荐一个IC、FPGA新手入门的好网站:👉快 点 击 进 入 学 习 吧👈 刚看完了第四章的内容,在此记录一下。 整个第四章主要是介绍了一些RTL级的设

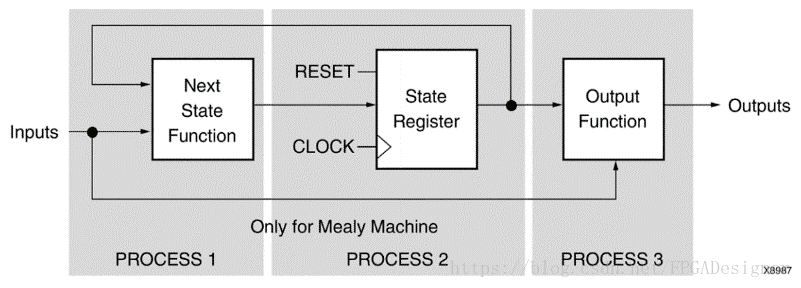

Verilog HDL高级数字设计 从零学习(一)

Verilog HDL高级数字设计 从零学习(一) 3.4 时序机设计3.5 状态转移图利用D触发器实现FSM的步骤 🔈声明: 🔑未经作者允许,禁止转载 🚩推荐一个IC、FPGA新手入门的好网站:👉快 点 击 进 入 学 习 吧👈 标题由于年初刚决定转做FPGA开发,虽然开发板的很多例程都做过,但感觉做的都是接口和一些简单的协议,最近真的开始自己设计

CheKine 系列高密度脂蛋白(HDL-C)含量检测方案

高密度脂蛋白( high-density lipoprotein,HDL) 为血清蛋白之一,是由脂质和蛋白质及其所携带的调节因子组成的复杂脂蛋白 ,亦称为a1脂蛋白。比较富含磷脂质,在血清中的含量约为200mg/dl。其蛋白质部分, A-Ⅰ约为75%, A-Ⅱ约为20%。由于可输出胆固醇促进胆固醇的代谢,所以作为动脉硬化预防因子而受到重视。 生理作用: 高密度脂蛋白运载周围组织中的胆固醇

(一)60秒倒计时电路Logisim电路原理图和Verilog HDL 描述+ DE2-70开发板

首先,感谢MOOC华中科技大学谭志虎老师的计算机硬件设计课程!这套课程学习下来,帮助我理解了当时学习数字逻辑课程中存在的许多困惑!! 硬件菜鸡一枚,本人硬件课程设计遇到的,特此记录下来,作为自己的学习记录,同时希望给还在挠头的同学一点参考,起到抛砖引玉的效果。废话少说!!正文来了!!!! 第一步:先在logisim这个软件中用画电路原理图的方式,来看看它的电路原理图是啥样的吧! 讲解一下原理图

Vivado使用技巧(1):HDL编写技巧

在Vivado中进行HDL代码设计,不仅需要描述数字逻辑电路中的常用功能,还要考虑如何发挥Xilinx器件的架构优势。目前常用的HDL语言有三种。 (1)VHDL语言的优势有: 语法规则更加严格;在HDL源代码中初始化RAM组件更容易;支持package;自定义类型;枚举类型;没有reg和wire之间的混淆。 (2)Verilog语言的优势有: 与C语言类似的语法;代码结构更紧凑;支持块注

HDL部分的axis_packet_generator_v1_0.v

module 模块名称 #(parameter integer 整数) 可以通过 module 模块名称 #(parameter integer 整数,) 的方式,实现像C语言一样给函数形参 具体解释如下input wire 和input wire变量说明 如图中,实例化ModuleA 一个对象 A,在ModuleB实例化一个 对象 B之后,.data_in用的是A.int

vivado RAM HDL Coding Guidelines

从编码示例下载编码示例文件。 块RAM读/写同步模式 您可以配置块RAM资源,为提供以下同步模式给定的读/写端口: •先读取:在加载新内容之前先读取旧内容。 •先写:新内容立即可供阅读先写也是众所周知的如通读。 •无变化:数据输出不会随着新内容加载到RAM而变化。 Vivado合成为所有这些同步模式提供了推理支持。你可以描述了用于RAM的每个端口的不同同步模式。 分布式RAM示例

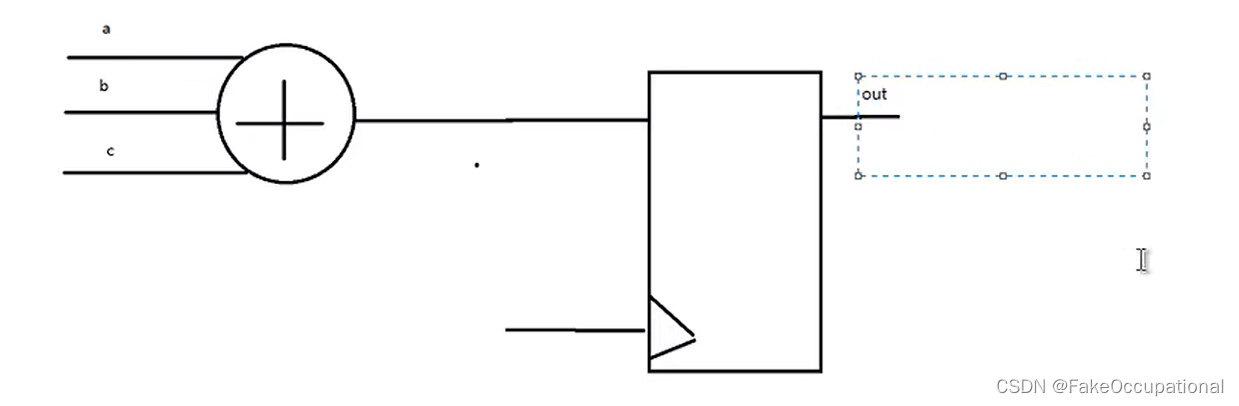

Verilog HDL小练习(一)二路选择器amp;amp;三位加法器

二路选择器是一种及基础的逻辑电路其基本功能描述为,当选择0时输出a,选择1时输出b RTL级描述如下: module muxtwo(out,a,b,sl);input a,b,sl;output out;//============================reg out;always@(sl or a or b)//表示只要有一个变化就执行下面的语句if(!sl)out=