本文主要是介绍(一)60秒倒计时电路Logisim电路原理图和Verilog HDL 描述+ DE2-70开发板,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

首先,感谢MOOC华中科技大学谭志虎老师的计算机硬件设计课程!这套课程学习下来,帮助我理解了当时学习数字逻辑课程中存在的许多困惑!!

硬件菜鸡一枚,本人硬件课程设计遇到的,特此记录下来,作为自己的学习记录,同时希望给还在挠头的同学一点参考,起到抛砖引玉的效果。废话少说!!正文来了!!!!

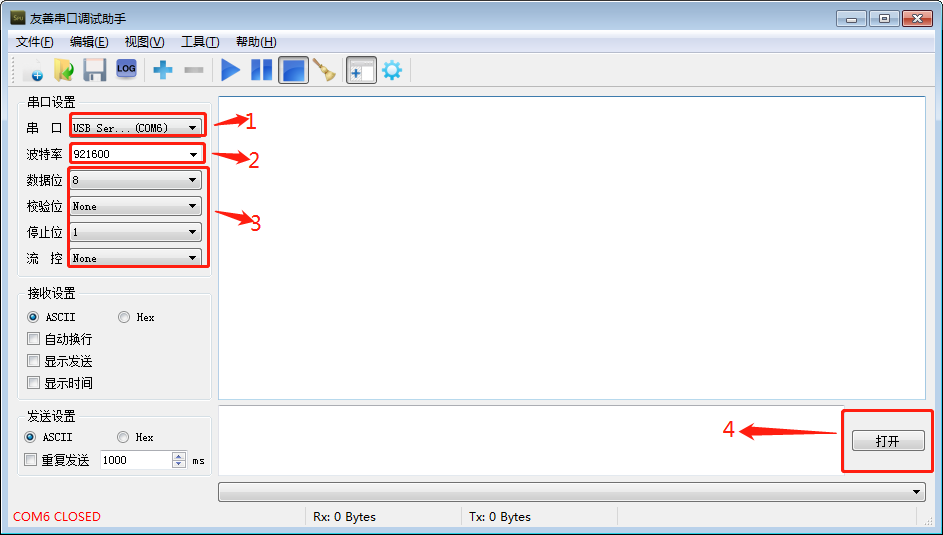

第一步:先在logisim这个软件中用画电路原理图的方式,来看看它的电路原理图是啥样的吧!

讲解一下原理图,因为我要在数码管上显示0059到0000所以,60秒倒计时的时间输出数据为16位二进制,因此我在设计倒计时模块的时候,采用了4个计数器(前面的高两位计数器其实没有起作用,使能信号始终为0,仅仅用来占位),第3个计数器可以从5到0进行倒数,第4个计数器可以从9到0倒数,每当从9数到0时,立马输出一个借位信号,将这个借位信号,传给第三个计数器,让第三个计数器可以减1。当第三个计数器和第四个计数器的借位信号输出都为1时,代表倒计时已经为0000,此时通过与非门将所有计数器的使能信号全部置0,(使能信号为0,停止计数)。

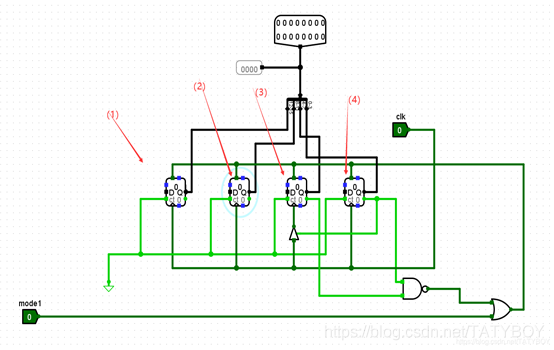

第二步,将倒计时电路进行封装,然后测试结果是否正确。

测试结果:如上面的测试结果图,按下倒计时的mode1,倒计时就开始了。当到0000时,自动停止。

第三步:将60秒倒计时用Verilog HDL硬件描述语言进行描述

module time_60(CK,CD,mode1);

input CK;

input mode1;

output[15:0]CD;

reg [15:0]cd=60; //初值设为60,可以设为任意,代表任意时间的倒计时

always@(posedge CK)

beginif(mode1)begin if(cd > 0)cd = cd-1; //60开始一直减下去,到0就不减了endendassign CD = cd;

endmodulemodule disp_dec(hex,dispout); //将十进制数转为BCD码

input[15:0] hex;

output[15:0] dispout;

reg [15:0] hex_;

reg [15:0] dec;

always@(*)beginhex_[15:0]=hex[15:0];dec[3:0]=hex_%10;dec[7:4]=(hex_%100-dec[3:0])/10;dec[11:8]=4'b0000;dec[15:12]=4'b0000;endassign dispout = dec;

endmodulemodule timeback(clk,en,distime); //顶层模块,调用上面两个模块

input clk;

input en;

output [15:0]distime;

wire [15:0]s1; //十进制时间的输出与BCD码转换器的输入之间的连线time_60 m2(.CK(clk),.CD(s1),.mode1(en));

disp_dec m1(.hex(s1),.dispout(distime));

endmodule

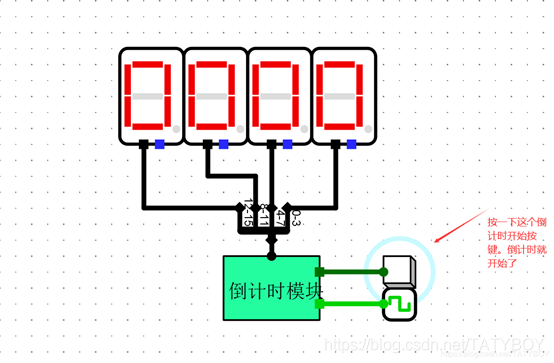

第四步:将上的倒计时电路下载到DE2-70开发板上

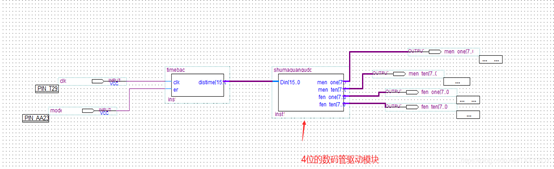

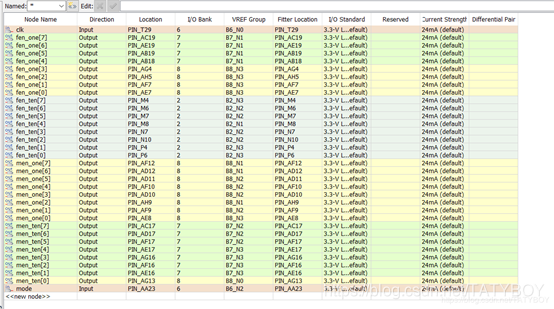

给60秒倒计时电路,接上数码管驱动模块,分配好引脚,下载到板子上就可以了,倒计时的Verilog HDL顶层模块图

4位的数码管译码电路Verilog HDL代码

//一位的七段译码模式

module seg_decode1(iflag,ia,oy); //高有效,不带小数点的数码管显示驱动input iflag; //共阴、共阳输出控制模块input [3:0] ia; //4位二进制的输入output reg [7:0]oy;//数码管的显示输出always@(iflag,ia)begincase(ia) //当iflag=1,共阴极输出,ia的取值对应输出4'b0000:oy=8'h3f; //04'b0001:oy=8'h06; //14'b0010:oy=8'h5b; //24'b0011:oy=8'h4f; //34'b0100:oy=8'h66; //44'b0101:oy=8'h6d; //54'b0110:oy=8'h7d; //64'b0111:oy=8'h27; //74'b1000:oy=8'h7f; //84'b1001:oy=8'h6f; //9endcaseif(!iflag) //iflag=0,共阳极输出oy=~oy; endendmodule //四位的七段译码模块

module seg_decode4(iflag,dec1,dec2,dec3,dec4,men_one,men_ten,fen_one,fen_ten);input iflag;input[3:0] dec1; //放置各个数码管的输入数据input[3:0] dec2;input[3:0] dec3;input[3:0] dec4;output [7:0] men_one; //个位output [7:0] men_ten; //十位output [7:0] fen_one; //百位output [7:0] fen_ten; //千位, 数码管输出显示seg_decode1 u1(iflag,dec1,men_one);seg_decode1 u2(iflag,dec2,men_ten);seg_decode1 u3(iflag,dec3,fen_one);seg_decode1 u4(iflag,dec4,fen_ten);endmodule //顶层模块,显示数据

module shumaguanqudong(Din,men_one,men_ten,fen_one,fen_ten); //码表显示驱动,合并上面的4个数码管驱动的输入与输出input [15:0]Din; //16位输入数据output [7:0] men_one; //个位output [7:0] men_ten; //十位output [7:0] fen_one; //百位output [7:0] fen_ten; //千位, 数码管输出显示seg_decode4 c2(.iflag(1'b0),.dec1(Din[3:0]),.dec2(Din[7:4]),.dec3(Din[11:8]),.dec4(Din[15:12]),.men_one(men_one),.men_ten(men_ten),.fen_one(fen_one),.fen_ten(fen_ten)); endmodule

原理图中,引脚分配情况

SW0是倒计时的使能信号mode1,高有效。

KEY0是倒计时的时钟信号

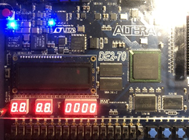

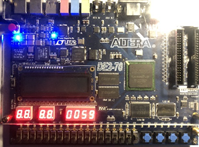

下板子的结果:

到此结束!!!!!

这篇关于(一)60秒倒计时电路Logisim电路原理图和Verilog HDL 描述+ DE2-70开发板的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!