logisim专题

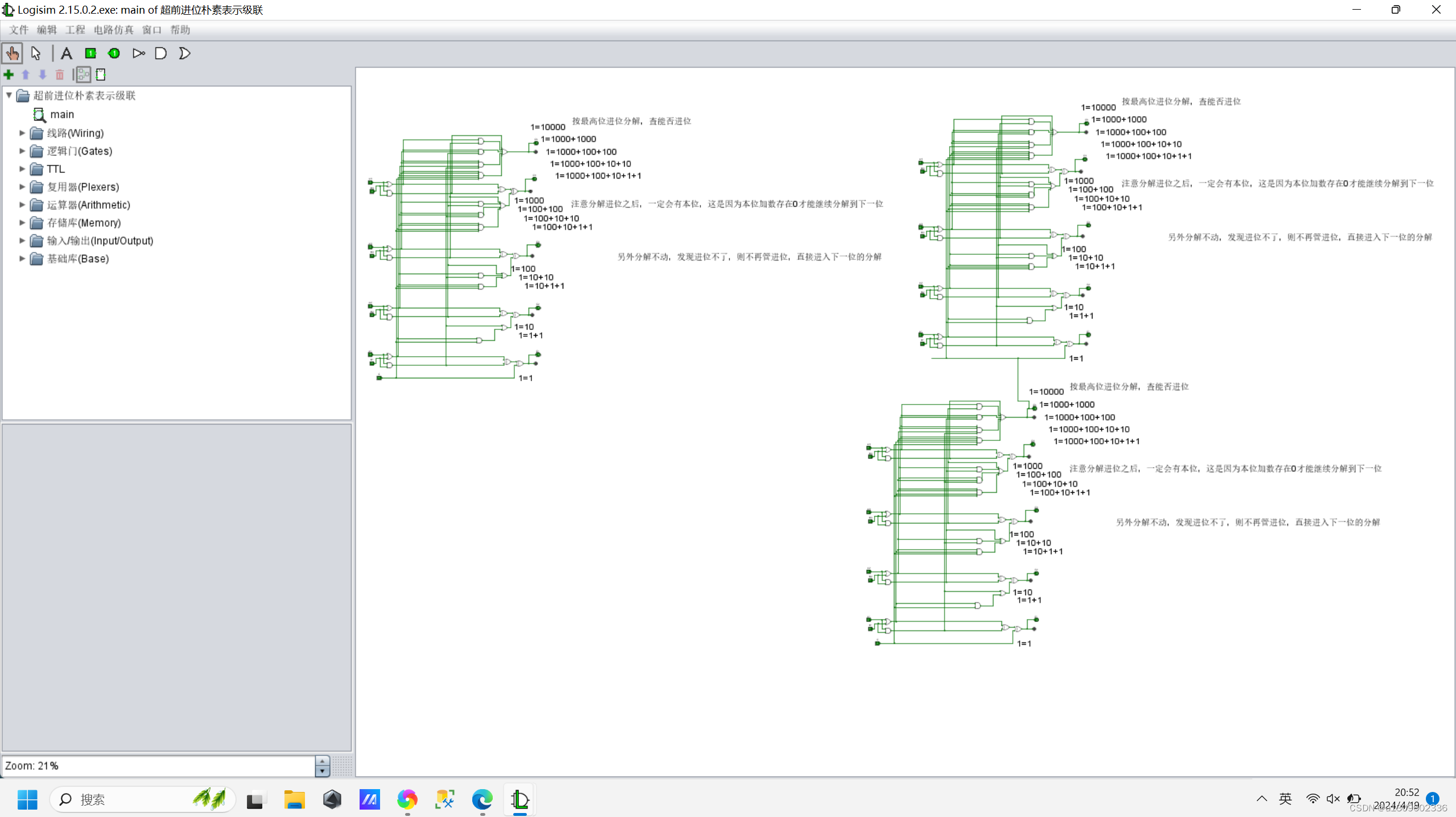

logisim 图解超前进位加法器原理解释

鄙人是视频作者,文件在视频简介的网盘链接。 找规律图解超前进位加法器与原理解释_哔哩哔哩_bilibili 一句话就是“把能导致进位到这个位置的情况全都穷举一遍。” 穷举情况看图中算式。 视频讲解比较啰嗦。

Logisim下半加器,全加器及二进制补码

一、1bit半加器电路 其电路由一个异或门和一个与门所组成,如图 ABCS0000010110011110 二、1bt全加器 由两个半加器组成,如图 ABCinCoutS0000001001100011101000101011101011011111 三、4位二进制数的补码器电路 补码原理如下:

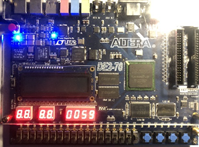

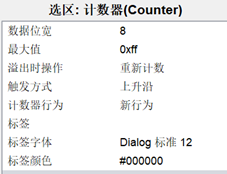

(一)60秒倒计时电路Logisim电路原理图和Verilog HDL 描述+ DE2-70开发板

首先,感谢MOOC华中科技大学谭志虎老师的计算机硬件设计课程!这套课程学习下来,帮助我理解了当时学习数字逻辑课程中存在的许多困惑!! 硬件菜鸡一枚,本人硬件课程设计遇到的,特此记录下来,作为自己的学习记录,同时希望给还在挠头的同学一点参考,起到抛砖引玉的效果。废话少说!!正文来了!!!! 第一步:先在logisim这个软件中用画电路原理图的方式,来看看它的电路原理图是啥样的吧! 讲解一下原理图

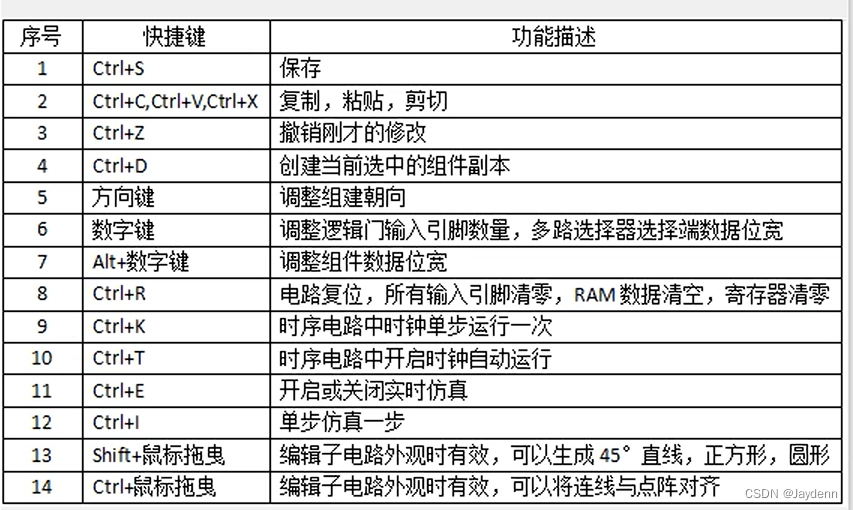

Logisim各部件简单翻译

Logisim各部件简单翻译 线路(Wiring) 逻辑门(Gates) 复用器(Plexers) 运算器(Arithmetic) 存储器(Memory) 输入/输出(Input/Output) 其他标签内部常用翻译

华科计算机组成原理实验(详细注解) 运算器设计(HUST) Educoder平台 Logisim环境

circ文件下载链接 第1关:8位可控加减法电路设计 第2关:CLA182四位先行进位电路设计 调整的位置 第3关:4位快速加法器设计 全加器FA可以通过第一关复制得到 第4关:16位快速加法器设计 第5关:32位快速加法器设计 第四关复制粘贴稍微调整线路得到 第6关:5位无符号阵列乘法器设计 若测试不通过,可以重新连接或换一个文件复制粘贴 第7关:6位有符

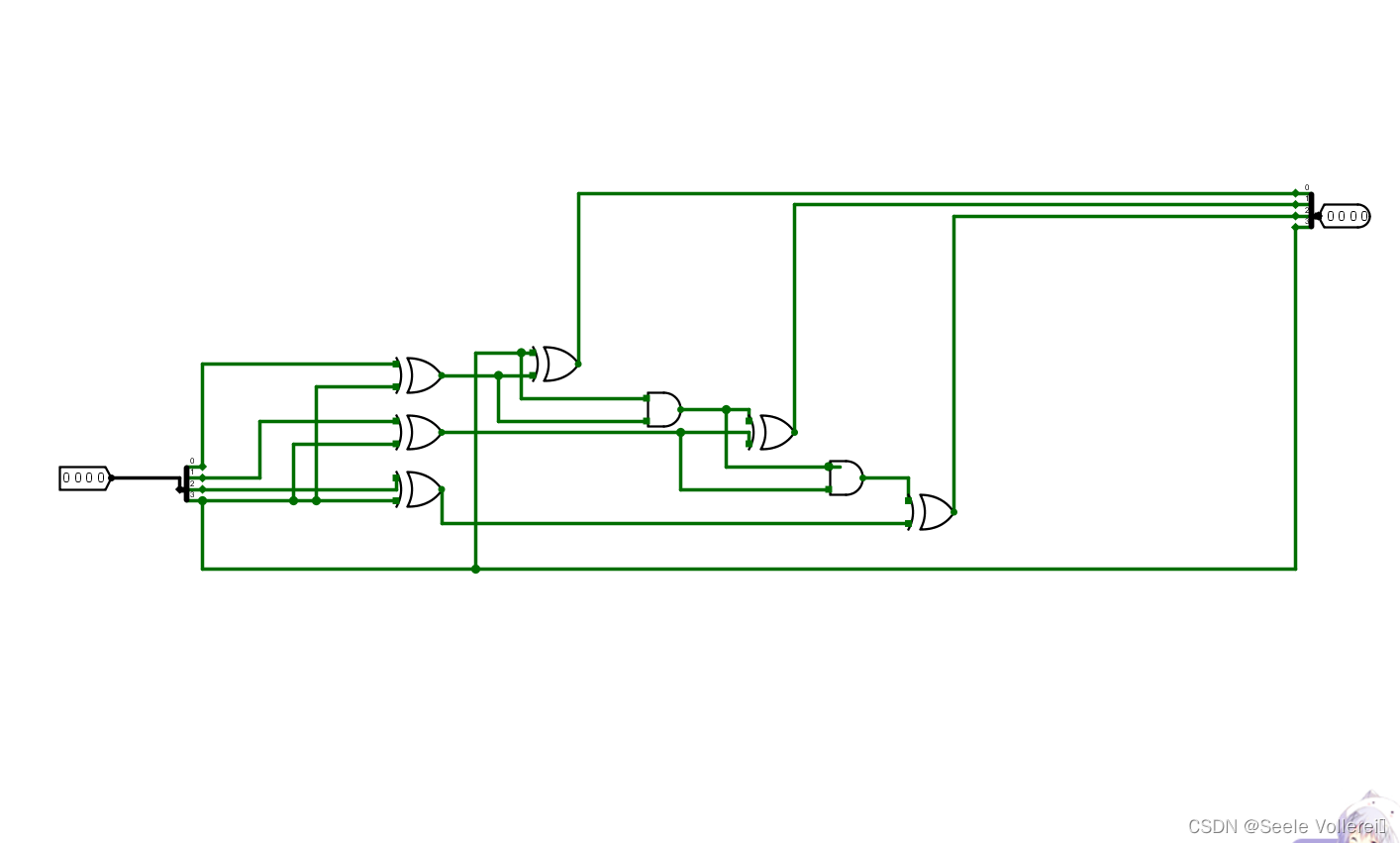

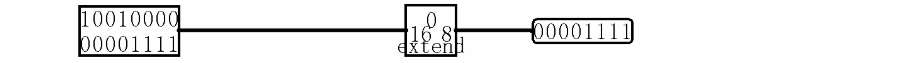

Logisim 构建一个1-bit全加器 Tunnel、Splitter、Extenders的使用

参考博客:《Logisim的使用》https://www.cnblogs.com/lfri/p/9790102.html 电路描述 功能:实现一个1-bit全加器 上面是别人的电路,下面是我的电路 经过测试,两个电路结果相同。 思路就是:把每一个输入连到两个AND Gate上,同时保证两个输入不能连接到相同的两个AND Gate上 还没十分理解为什么要设计成三个输入,可能是两个普通输入,一个

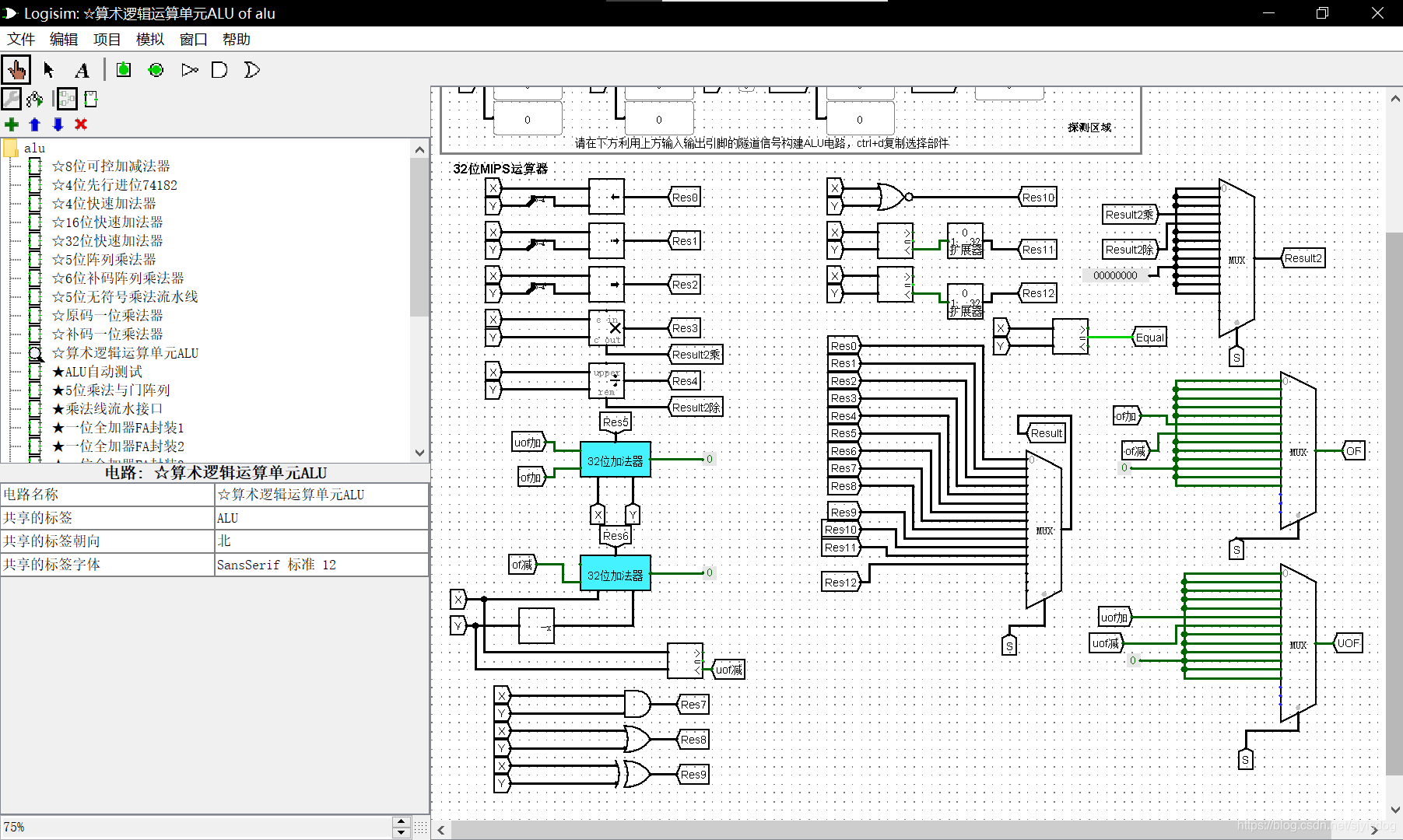

头歌-自己动手画CPU(第三关)-MIPS运算器设计-Logisim

四位先行进位74182 四位快速加法器 十六位快速加法器 32位快速加法器 我这个画法是参考了同学的感觉比较牛逼 就把之前的删了改成这个了 32位MIPS运算器 画的时候注意分离的参数、比较器的数字类型就行了 把这些图全连完 交上就对了 别嫌麻烦

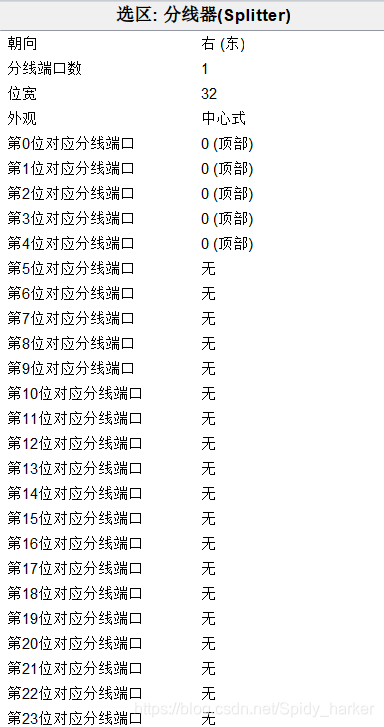

头歌-自己动手画CPU(第四关)-汉字字库存储芯片扩展实验-Logisim

字库电路: 分离器参数: 需要把参考字库中与D1相连的ROM中的内容分4份(已经分好了0123)贴到下面这四个ROM里: 提交,答案正确。 要源文件的童鞋请关注、点赞、收藏后私信我